#### Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

2016年5月

# FDMF5839 - 集成有热警告和热关断功能的智能功率级 (SPS) 模块

#### 特性

- 包含 Flip Chip 低侧 MOSFET 的超紧凑型 5 mm x 5 mm PQFN Copper-Clip 封装

- 高电流处理能力: 35 A

- 三态 5 V PWM 输入栅极驱动器

- 低侧驱动 (LDRV) 的动态电阻模式可在负电感电流期 间减慢低侧 MOSFET 开关

- 自动 DCM(低侧栅极关断)使用 ZCD# 输入

- 热警告功能 (THWN#),对栅极驱动器 IC 过温情况 发出警告

- 热关断 (THDN)

- 高侧短路故障 # 检测/关断

- 双通道模式使能/故障#引脚

- ZCD# 输入和 EN 输入各自的内部上拉和下拉

- Fairchild PowerTrench® MOSFET,可提供干净的电压波形并降低振铃噪声

- 低侧 MOSFET 中的 Fairchild SyncFET 技术(集成 肖特基二极管)

- 集成式自举肖特基二极管

- 优化的/极短的死区时间

- VCC 欠压锁定 (UVLO)

- 为使开关频率达到 1.5 MHz 而进行优化

- PWM 最低可控导通时间: 30 ns

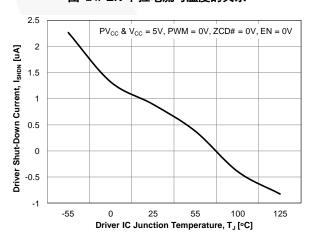

- 低关断电流: < 3 µA

- 优化的 FET 对以实现最高效率: 10~15% 占空比

- 工作结温范围: -40°C 至 +125°C

- 飞兆绿色封装并符合 RoHS 标准

#### 描述

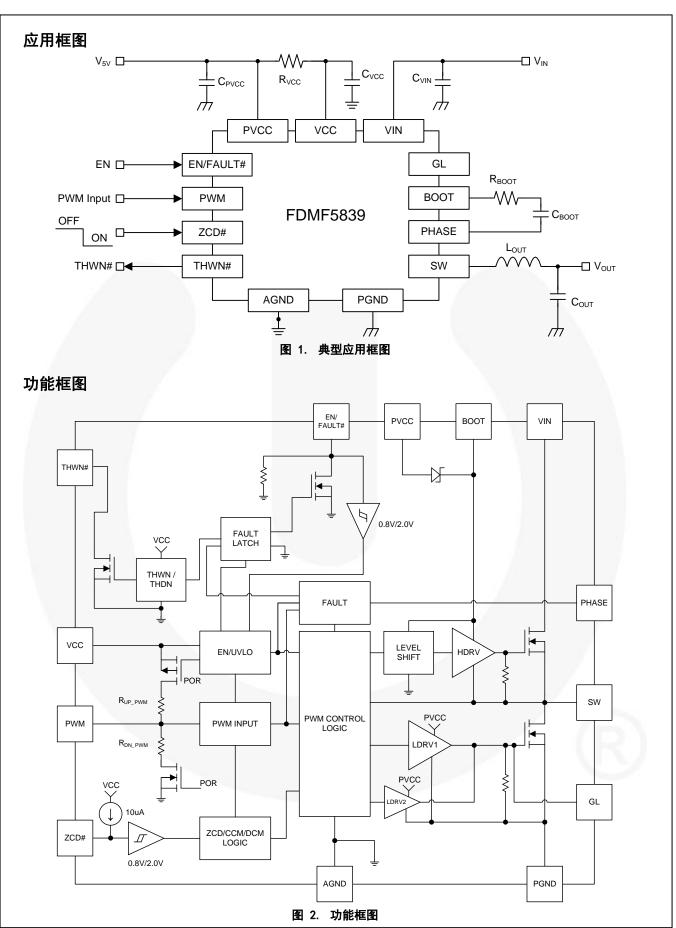

SPS 系列是 Fairchild 新一代完全优化的超小型集成 MOSFET 及驱动器功率级解决方案,可用于高电流、高频率、同步降压 DC-DC 应用。FDMF5839 将一个带有自举肖特基二级管的驱动器 IC、两个功率 MOSFET 和一个热监控器集成至热增强的超紧凑型 5 mm x 5 mm 封装内。

通过集成的方法对 SPS 开关功率级进行了优化,以实现驱动器和 MOSFET 的动态性能、最小化系统电感和功率 MOSFET R<sub>DS(ON)</sub>。 SPS 系列采用 Fairchild 的高性能 PowerTrench<sup>®</sup> MOSFET 技术,可以减少开关振铃,省去大多数降压转换器应用中使用的缓冲器电路。

驱动器 IC 通过减少死区时间和传播延迟,可进一步提高性能。热警告功能 会发出潜在过温情况的警告。如果发生过温情况,热关断功能则会关断驱动器。FDMF5839还为提高轻负载效率整合了自动 DCM 模式 (ZCD#)。FDMF5839还提供三态 5 V PWM 输入,可实现与大量PWM 控制器的兼容性。

#### 应用

- 笔记本、平板电脑和超级本

- 服务器和工作站、V-Core 和非 V-Core 直流一直流 转换器

- 台式和一体式电脑、V-Core 和非 V-Core 直流一直 流转换器

- 高性能游戏主板

- 高电流直流—直流负载点 (POL) 转换器

- 网络和电信微处理器稳压器

- 小尺寸稳压器模块

#### 订购信息

| 器件编号     | 额定电流 | 封装                                     | 顶标   |

|----------|------|----------------------------------------|------|

| FDMF5839 | 35 A | 31 引脚、铜条键合 PQFN SPS、5.0 mm x 5.0 mm 封装 | 5839 |

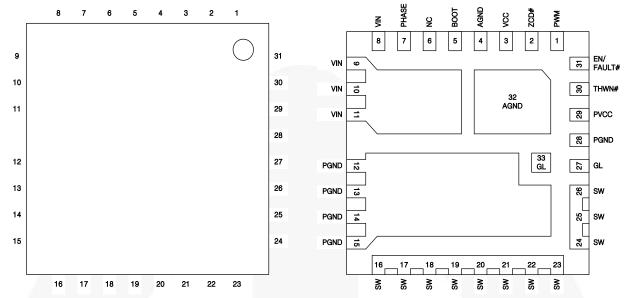

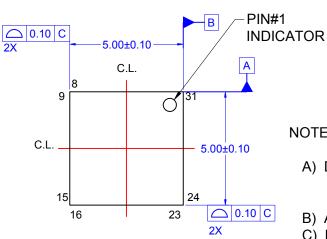

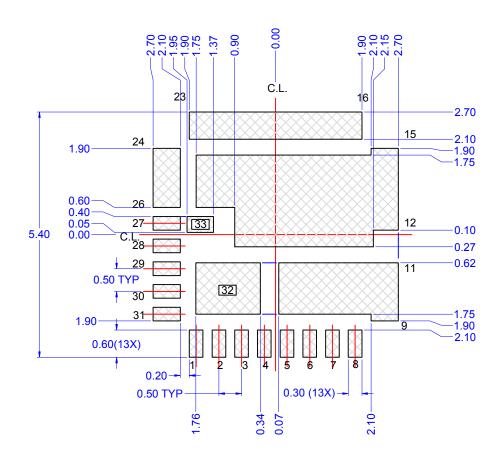

# 引脚配置

图 3. 引脚配置—俯视图和透视图

# 引脚定义

| 引脚号      | 名称             | 描述                                                                                                |  |  |  |

|----------|----------------|---------------------------------------------------------------------------------------------------|--|--|--|

| 1        | PWM            | 栅极驱动器 IC 的 PWM 输入                                                                                 |  |  |  |

| 2        | ZCD#           | ZCD(自动 DCM)比较器的使能输入                                                                               |  |  |  |

| 3        | VCC            | 所有模拟控制功能的电源输入; 这是"静态的" V <sub>CC</sub>                                                            |  |  |  |

| 4,32     | AGND           | IC 模拟部分和基板的模拟接地,内部连接至 PGND                                                                        |  |  |  |

| 5        | воот           | 高侧 MOSFET 栅极驱动器的电源。BOOT 与 PHASE 之间的电容器提供导通 N 沟道高侧 MOSFET 所需的电荷。                                   |  |  |  |

| 6        | NC             | 未连接                                                                                               |  |  |  |

| 7        | PHASE          | 自举电容器的返回连接,内部连接至 SW 节点                                                                            |  |  |  |

| 8~11     | VIN            | 力率级的功率输入                                                                                          |  |  |  |

| 12~15,28 | PGND           | 力率级的功率地                                                                                           |  |  |  |

| 16~26    | SW             | 高侧和低侧 MOSFET 之间的开关节点;同时是栅极驱动器 SW 节点比较器的输入和 ZCD<br>比较器的输入                                          |  |  |  |

| 27,33    | GL             | 栅极低电平、低侧 MOSFET栅极监控器                                                                              |  |  |  |

| 29       | PVCC           | LS <sup>(1)</sup> 栅极驱动器和 自举二极管的电源输入                                                               |  |  |  |

| 30       | THWN#          | 125℃ 热警告标识 – 当检测到 125℃ 热警告预设温度时会拉至低电平                                                             |  |  |  |

| 31       | EN /<br>FAULT# | 双功能,栅极驱动器 IC 的使能输入。FAULT# - 在检测到故障情况(HS <sup>(2)</sup> MOSFET 短路或 150°C THDN)时,内部下拉在物理上将该引脚拉至低电平。 |  |  |  |

#### 注意:

- 1. LS=低侧。

- 2. HS =高侧。

### 绝对最大额定值

如果应力超过绝对最大额定值,器件可能会损坏。在超出推荐的工作条件的情况下,该器件可能无法正常工作,所以不建议让器件在这些条件下长期工作。此外,长期在高于推荐的工作条件下工作,会影响器件的可靠性。绝对最大额定值仅是应力规格值。 $T_A=T_J=25^{\circ}C$

| 符号                                | 参数                                                                         |                                                                        |      | 最大值                  | 单位   |  |

|-----------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|------|----------------------|------|--|

| V <sub>CC</sub>                   | 电源电压                                                                       | 以 AGND 为基准                                                             | -0.3 | 6.0                  | V    |  |

| PV <sub>CC</sub>                  | 驱动电压                                                                       | 以 AGND 为基准                                                             | -0.3 | 6.0                  | V    |  |

| V <sub>EN/FAULT#</sub>            | 输出启用/禁用                                                                    | 以 AGND 为基准                                                             | -0.3 | 6.0                  | V    |  |

| $V_{PWM}$                         | PWM 信号输入                                                                   | 以 AGND 为基准                                                             | -0.3 | V <sub>CC</sub> +0.3 | V    |  |

| V <sub>ZCD#</sub>                 | ZCD 模式输入                                                                   | 以 AGND 为基准                                                             | -0.3 | 6.0                  | V    |  |

| 1/                                | <b>化中亚加亚中立测学习加</b>                                                         | 以 AGND 为基准(仅适用于直流)                                                     | -0.3 | 6.0                  | W    |  |

| $V_{GL}$                          | 低电平栅极生产测试引脚<br>                                                            | 以 AGND为基准,AC<20 ns                                                     | -3.0 | 6.0                  | V    |  |

| V <sub>THWN#</sub>                | 热警告                                                                        | 以 AGND 为基准                                                             | -0.3 | 6.0                  | V    |  |

| V <sub>IN</sub>                   | 电源输入                                                                       | 以 PGND、AGND 为基准                                                        | -0.3 | 30.0                 | V    |  |

| V                                 | DUACE                                                                      | 以PGND、AGND 为基准(仅适用于直流)                                                 | -0.3 | 30.0                 | V    |  |

| $V_{PHASE}$                       | PHASE                                                                      | 以PGND为基准, AC <20 ns                                                    | -7.0 | 35.0                 |      |  |

| V                                 | 以 PGND、AGND 为基准(仅适用于直流)                                                    |                                                                        | -0.3 | 30.0                 | V    |  |

| $V_{SW}$                          | 开关节点输入<br>                                                                 | 以 PGND 为基准,AC <20 ns                                                   | -7.0 | 35.0                 | V    |  |

| \/                                | <b>力兴力</b> 源                                                               | 以 AGND 为基准(仅适用于直流)                                                     | -0.3 | 35.0                 | V    |  |

| $V_{BOOT}$                        | 自举电源                                                                       | 以 AGND 为基准,AC <20 ns                                                   | -5.0 | 40.0                 | V    |  |

| V <sub>BOOT-PHASE</sub>           | Boot 至 PHASE 电压                                                            | 以 PVCC 为基准                                                             | -0.3 | 6.0                  | V    |  |

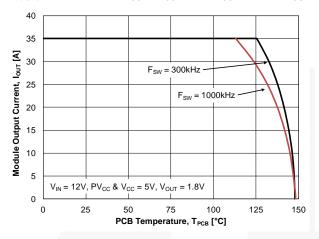

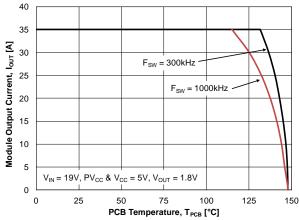

| (3)                               | FA 11 - + ' +                                                              | $f_{SW} = 300 \text{ kHz}, V_{IN}=12 \text{ V}, V_{OUT}=1.8 \text{ V}$ |      | 35                   | ^    |  |

| I <sub>O(AV)</sub> <sup>(3)</sup> | 输出电流<br>                                                                   | $f_{SW} = 1 \text{ MHz}, V_{IN}=12 \text{ V}, V_{OUT}=1.8 \text{ V}$   |      | 30                   | Α    |  |

| I <sub>FAULT</sub>                | EN/FAULT# 灌电流                                                              |                                                                        | -0.1 | 7.0                  | mA   |  |

| θ <sub>J-A</sub>                  | 结至环境热阻                                                                     |                                                                        |      | 12.4                 | °C/W |  |

| θ <sub>J-PCB</sub>                | 结至 PCB 热阻(在 Fairchild SPS 热板下)                                             |                                                                        |      | 1.8                  | °C/W |  |

| T <sub>A</sub>                    | 环境温度范围                                                                     |                                                                        |      | +125                 | °C   |  |

| $T_J$                             | 最大结温                                                                       |                                                                        |      | +150                 | °C   |  |

| T <sub>STG</sub>                  | 存储温度范围                                                                     |                                                                        |      | +150                 | °C   |  |

| ECD.                              | 静电放电防护       人体模型, ANSI/ESDA/JEDEC JS-001-2012         元件充电模型, JESD22-C101 |                                                                        | 3000 |                      | .,   |  |

| ESD                               |                                                                            |                                                                        | 2500 |                      | V    |  |

#### 注:

3.  $I_{O(AV)}$  额定值是通过在  $T_A=25$ °C 及自然对流冷却条件下测试 Fairchild 的 SPS 评测板得到的。该额定值受限于 SPS 峰值温度  $T_J=150$ °C,并随工作条件和 PCB 布局变化。在不同应用设置中,该额定值可能会发生变化。

# 推荐工作条件

推荐的操作条件表明确了器件的真实工作条件。指明推荐的工作条件,以确保器件的最佳性能达到数据表中的规格。飞兆半导体建议不要超过推荐工作条件,也不能按照绝对最大额定值进行设计。

| 符号               | 参数         | 最小值                | 典型值  | 最大值                 | 单位 |

|------------------|------------|--------------------|------|---------------------|----|

| V <sub>CC</sub>  | 控制电路电源电压   | 4.5                | 5.0  | 5.5                 | V  |

| PV <sub>CC</sub> | 栅极驱动电路电源电压 | 4.5                | 5.0  | 5.5                 | V  |

| V <sub>IN</sub>  | 输出级电源电压    | 4.5 <sup>(4)</sup> | 19.0 | 24.0 <sup>(5)</sup> | V  |

#### 注意:

- 4. 根据应用条件,可实现 3.0 V V<sub>IN</sub>。

- 5. 在  $V_N$  较高的条件下运行,在 MOSFET 开关瞬态过程中,可能在 SW  $\Xi$  GND 和 BOOT  $\Xi$  GND 节点上产生大量交流电压过冲。 为了确保 SPS 可靠运行,SW  $\Xi$  GND 和 BOOT  $\Xi$  GND 必须保持在上表中的绝对最大额定值或以下。

# 电气特性

典型值是在  $V_{IN}$ =12 V、 $V_{CC}$ = $PV_{CC}$ =5 V 且  $T_A$ = $T_J$ =+25°C 条件下测得的,除非另有说明。

最小/最大值是在  $V_{IN}$ =12 V、 $V_{CC}$ = $PV_{CC}$ =5 V ± 10% 且  $T_{J}$ = $T_{A}$ =-40 ~ 125°C 条件下测得的,除非另有说明。

| 符号                       | 参数                                           | 条件                                                                                                     | 最小值                    | 典型值       | 最大值 | 单位 |

|--------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------|-----------|-----|----|

| 基本工作                     | 1                                            |                                                                                                        |                        |           | •   |    |

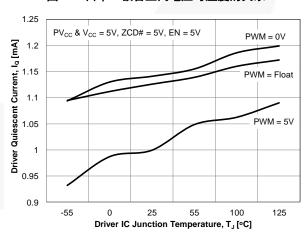

| <br>IQ                   | 静态电流                                         | I <sub>Q</sub> =I <sub>VCC</sub> + I <sub>PVCC</sub> 、 EN=HIGH 、<br>PWM=LOW 或 HIGH 或 Float(非开<br>关过程中) |                        |           | 2   | mA |

| I <sub>SHDN</sub>        | 关断电流                                         | I <sub>SHDN</sub> =I <sub>VCC</sub> + I <sub>PVCC</sub> , EN=GND                                       |                        |           | 3   | μΑ |

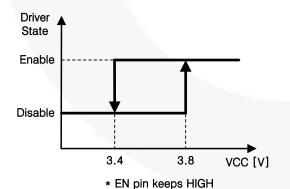

| $V_{\text{UVLO}}$        | 欠压闭锁阈值                                       | V <sub>CC</sub> 上升                                                                                     | 3.5                    | 3.8       | 4.1 | V  |

| V <sub>UVLO_HYST</sub>   | UVLO 滞环                                      |                                                                                                        |                        | 0.4       |     | V  |

| t <sub>D_POR</sub>       | POR 延迟到启用 IC                                 | Vcc UVLO 上升到内部 PWM 启用                                                                                  |                        |           | 20  | μs |

| EN 输入                    |                                              |                                                                                                        |                        | •         | •   |    |

| V <sub>IH_EN</sub>       | 输入电压高电平                                      |                                                                                                        | 2.0                    |           |     | V  |

| V <sub>IL_EN</sub>       | 输入电压低电平                                      |                                                                                                        |                        |           | 0.8 | V  |

| R <sub>PLD_EN</sub>      | 下拉电阻                                         |                                                                                                        | /                      | 250       |     | kΩ |

| t <sub>PD_ENL</sub>      | EN 低电平传输延迟                                   | PWM=GND, EN 变为低电平到 GL<br>变为低电平                                                                         |                        | 25        |     | ns |

| t <sub>PD_ENH</sub>      | EN 高电平传输延迟                                   | PWM=GND,EN 变为高电平到 GL<br>变为高电平                                                                          |                        |           | 20  | μs |

| ZCD# 输入                  |                                              |                                                                                                        |                        |           |     |    |

| V <sub>IH_ZCD#</sub>     | 输入电压 高电平                                     |                                                                                                        | 2.0                    |           |     | V  |

| V <sub>IL_ZCD#</sub>     | 输入电压低电平                                      |                                                                                                        |                        |           | 0.8 | V  |

| I <sub>PLU_ZCD#</sub>    | 上拉电流                                         |                                                                                                        | 1                      | 10        |     | μΑ |

| t <sub>PD_ZLGLL</sub>    | ZCD# 低电平传输延迟                                 | PWM=GND, ZCD# 变为低电平到<br>GL变为低电平(确保 I <sub>L</sub> <=0)                                                 |                        | 10        |     | ns |

| t <sub>PD_ZHGLH</sub>    | ZCD# 高电平传输延迟                                 | PWM=GND,ZCD# 变为高电平到<br>GL 变为高电平                                                                        |                        | 10        |     | ns |

| PWM 输入                   |                                              |                                                                                                        |                        |           |     |    |

| R <sub>UP_PWM</sub>      | 上拉电阻                                         |                                                                                                        |                        | 10        |     | kΩ |

| R <sub>DN_PWM</sub>      | 下拉电阻                                         |                                                                                                        |                        | 10        |     | kΩ |

| $V_{IH\_PWM}$            | PWM 高电平电压                                    | V <sub>CC</sub> =PV <sub>CC</sub> =5 V;                                                                | 3.8                    |           |     | V  |

| $V_{TRI\_Window}$        | 三态窗口                                         | 最小值/最大值:                                                                                               | 1.2                    |           | 3.1 | V  |

| $V_{IL\_PWM}$            | PWM 低电平电压                                    | T <sub>A</sub> =T <sub>J</sub> =-40°C 至 125°C                                                          | 7                      |           | 0.8 | V  |

| t <sub>D_HOLD-OFF</sub>  | 三态关断时间                                       | 且 V <sub>CC</sub> =PV <sub>CC</sub> =5 V ±10%                                                          |                        | 90        | 130 | ns |

| $V_{HIZ\_PWM}$           | 三态开路电压                                       |                                                                                                        | 2.1                    | 2.5       | 2.9 | V  |

| 最低可控导通                   |                                              |                                                                                                        | /                      | 1         |     |    |

| t <sub>MIN_PWM_ON</sub>  | PWM 最低可控导通时间                                 | SW 节点从 GND 切换到 VIN<br>所需的最小 PWM 高电平脉冲                                                                  | 30                     |           |     | ns |

| 强制最小 GL                  | 高电平时间                                        |                                                                                                        |                        |           |     |    |

| t <sub>MIN_GL_HIGH</sub> | 强制最小 GL 高电平                                  | 当检测到低电平 VBOOT-SW 且<br>PWM LOW=< 100 ns 时,最小 GL 高<br>电平时间                                               |                        | 100       | 6   | ns |

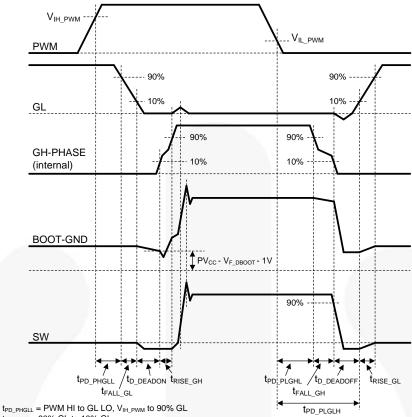

| PWM 传输延                  | 迟与死区时间(V <sub>IN</sub> =12 V、V <sub>CC</sub> | = PV <sub>CC</sub> =5 V、f <sub>SW</sub> =1 MHz、I <sub>OUT</sub> =20 A                                  | , T <sub>A</sub> =25°( | <b>C)</b> |     |    |

| t <sub>PD_PHGLL</sub>    | PWM 高电平传输延迟                                  | PWM 变为高电平到 GL 变为低电平, V <sub>IH_PWM</sub> 到 90% GL                                                      |                        | 15        |     | ns |

| t <sub>PD_PLGHL</sub>    | PWM 低电平传输延迟                                  | PWM变为低电平到 GH <sup>(6)</sup> 变为低电<br>平,V <sub>IL_PWM</sub> 到 90% GH                                     |                        | 30        |     | ns |

| t <sub>PD_PHGHH</sub>    | PWM 高电平传输延迟(ZCD#<br>保持低电平)                   | PWM 变为高电平到 GH 变为高电平, V <sub>IH_PWM</sub> 到 10% GH(ZCD#=LOW、I <sub>L</sub> =0,且假定工作模式为 DCM)             |                        | 10        |     | ns |

接下页

# 电气特性

典型值是在 V<sub>IN</sub>=12 V、V<sub>CC</sub>=PV<sub>CC</sub>=5 V 且 T<sub>A</sub>=T<sub>J</sub>=+25°C 条件下测得的,除非另有说明。

最小/最大值是在  $V_{IN}$ =12 V、 $V_{CC}$ = $PV_{CC}$ =5 V ± 10% 且  $T_{J}$ = $T_{A}$ =-40 ~ 125°C 条件下测得的,除非另有说明。

| 符号                             | 参数                                            | 条件                                                      | 最小值      | 典型值  | 最大值      | 单位 |

|--------------------------------|-----------------------------------------------|---------------------------------------------------------|----------|------|----------|----|

|                                |                                               | GL 变为低电平到 GH 变为高电平,                                     |          |      |          |    |

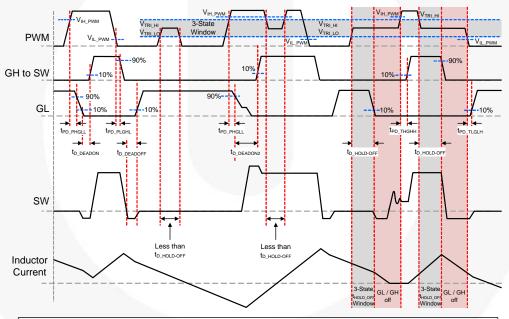

| t <sub>D_DEADON</sub>          | LS 关断到 HS 导通死区时间                              | 10% GL 到 10% GH, PWM 从低电平过渡到高电平—参见图 29                  |          | 7    |          | ns |

|                                |                                               | GH 变为低电平到 GL 变为高电平,                                     |          |      |          |    |

| $t_{D\_DEADOFF}$               | HS 关断到 LS 导通死区时间                              | 10% GH 到 10% GL, PWM 从高电平过渡到低电平—参见图 29                  |          | 5    |          | ns |

| t <sub>R_GH_20A</sub>          | 20 A I <sub>OUT</sub> 下的 GH 上升时间              | 10% GH 到 90% GH, I <sub>OUT</sub> =20 A                 |          | 9    |          | ns |

| t <sub>F_GH_20A</sub>          | 20 A I <sub>OUT</sub> 下的 GH 下降时间              | 90% GH 到 10% GH, I <sub>OUT</sub> =20 A                 |          | 9    |          | ns |

| t <sub>R_GL_20A</sub>          | 20 A I <sub>OUT</sub> 下的 GL 上升时间              | 10% GL 到 90% GL, I <sub>OUT</sub> =20 A                 |          | 6    |          | ns |

| t <sub>F_GL_20A</sub>          | 20 A I <sub>OUT</sub> 下的 GL 下降时间              | 90% GL 到 10% GL, I <sub>OUT</sub> =20 A                 |          | 5    |          | ns |

| t <sub>PD_TSGHH</sub>          | 退出三态传输延迟                                      | PWM(从三态)变为高电平到 GH<br>变为高电平,V <sub>IH_PWM</sub> 到 10% GH |          |      | 45       | ns |

| t <sub>PD_TSGLH</sub>          | 退出三态传输延迟                                      | PWM(从三态)变为低电平到 GL<br>变为高电平,V <sub>IL_PWM</sub> 到 10% GL |          |      | 45       | ns |

| 高侧驱动器 (H                       | HDRV, V <sub>CC</sub> =PV <sub>CC</sub> =5 V) |                                                         |          |      |          |    |

| R <sub>SOURCE_GH</sub>         | 输出电阻,源                                        | 源电流=100 mA                                              | N        | 0.68 |          | Ω  |

| R <sub>SINK_GH</sub>           | 输出电阻, 灌                                       | 灌电流=100 mA                                              |          | 0.9  |          | Ω  |

| t <sub>R_GH</sub>              | GH 上升时间                                       | 10% GH 到 90% GH, C <sub>LOAD</sub> =1.3 nF              |          | 4    | A.       | ns |

| t <sub>F GH</sub>              | GH 下降时间                                       | 90% GH 到 10% GH, C <sub>LOAD</sub> =1.3 nF              |          | 3    |          | ns |

|                                |                                               | 存在 LDRV2,V <sub>cc</sub> =PV <sub>cc</sub> =5 V)        |          |      |          |    |

| R <sub>SOURCE_GL</sub>         | 输出电阻,源                                        | 源电流=100 mA                                              |          | 1.2  |          | Ω  |

| I <sub>SOURCE GL</sub>         | 输出源峰值电流                                       | GL=2.5 V                                                |          | 2    |          | Α  |

| R <sub>SINK</sub> GL           | 输出电阻, 灌                                       | 灌电流=100 mA                                              |          | 1.62 |          | Ω  |

| I <sub>SINK_GL</sub>           | 输出灌峰值电流                                       | GL=2.5 V                                                |          | 2    |          | Α  |

| 低侧驱动器(                         | CCM1 运行模式下,LDRV1 与                            | LDRV2 并行,V <sub>CC</sub> =PV <sub>CC</sub> =5 V)        | •        |      | •        |    |

| R <sub>SOURCE</sub> GL         | 输出电阻,源                                        | 源电流=100 mA                                              |          | 0.65 |          | Ω  |

| I <sub>SOURCE_GL</sub>         | 输出源峰值电流                                       | GL=2.5 V                                                |          | 4    |          | Α  |

| R <sub>SINK_GL</sub>           | 输出电阻, 灌                                       | 灌电流=100 mA                                              |          | 0.53 |          | Ω  |

| I <sub>SINK_GL</sub>           | 输出灌峰值电流                                       | GL=2.5 V                                                |          | 7    |          | Α  |

| t <sub>R_GL</sub>              | GL 上升时间                                       | 10% GL 到 90% GL, C <sub>LOAD</sub> =7.0 nF              | - V      | 9    |          | ns |

| t <sub>F_GL</sub>              | GL 下降时间                                       | 90% GL 到 10% GL, C <sub>LOAD</sub> =7.0 nF              |          | 6    |          | ns |

| 热警告标识 (1                       | 125°C)                                        |                                                         |          | 1    |          |    |

| T <sub>ACT_THWN_125</sub>      |                                               |                                                         | 1        | 125  |          | °C |

| T <sub>RST_THWN_125</sub>      |                                               | - T」=TA 时在驱动器 IC 上测得                                    |          | 110  |          | °C |

| R <sub>PLD_THWN</sub>          | 下拉电阻                                          | I <sub>PLD_THWN</sub> =1 mA                             |          | 100  |          | Ω  |

| 热关断 (150°(                     | C)                                            | _                                                       | l        | - 7  |          |    |

| T <sub>ACT_THDN</sub>          | 激活温度                                          | T <sub>J</sub> =T <sub>A</sub> 时在驱动器 IC 上测得             |          | 150  |          | °C |

| R <sub>PLD_EN-THDN</sub>       | 下拉电阻                                          | I <sub>PLD EN-THDN</sub> =1 mA                          |          | 50   |          | Ω  |

| <u>灾难性故障(</u>                  |                                               | res_en mon                                              |          |      |          |    |

| V <sub>SW MON</sub>            | SW 监控器基准电压                                    |                                                         |          | 1.3  | 2        | V  |

| t <sub>D_FAULT</sub>           | 传输延迟到将 EN/FAULT# 信号拉至低电平                      |                                                         |          | 20   |          | ns |

| <u> </u>                       | 2 2-10 D                                      |                                                         | <u>I</u> | I    | <u>I</u> |    |

| 日巫秋官                           |                                               |                                                         |          |      |          |    |

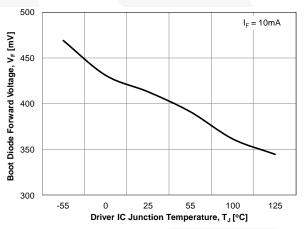

| <u>自举二极管</u><br>∨ <sub>F</sub> | 正向压降                                          | I <sub>F</sub> =10 mA                                   |          | 0.4  |          | V  |

#### 注:

6. GH=栅极高, 高侧 MOSFET 的内部栅极引脚。

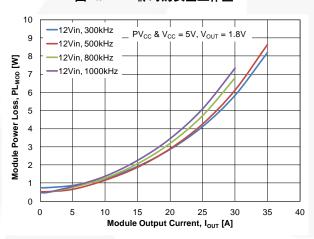

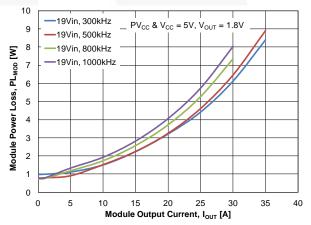

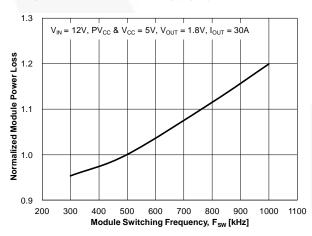

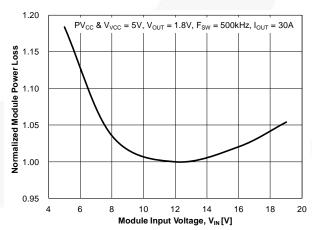

测试条件: V<sub>IN</sub>=12 V、 V<sub>CC</sub>=PV<sub>CC</sub>=5 V、V<sub>OUT</sub>=1.8 V、L<sub>OUT</sub>=250 nH、T<sub>A</sub>=25℃ 且为自然对流冷却,除非另有说明。

图 4. 12 V<sub>IN</sub> 时的安全工作区

图 5. 19 V<sub>IN</sub> 时的安全工作区

图 6. 12 V<sub>IN</sub> 时的功耗与输出电流之间的关系

图 7. 19 V<sub>IN</sub> 时的功耗与输出电流之间的关系

图 8. 功耗与开关频率之间的关系

图 9. 功耗与输入电压之间的关系

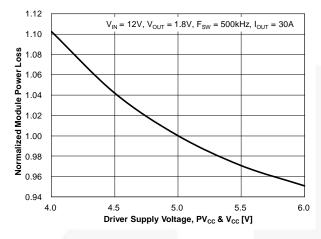

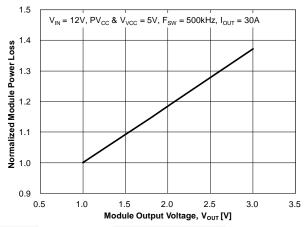

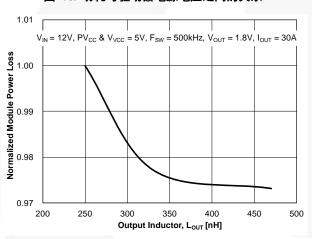

测试条件: V<sub>IN</sub>=12 V 、 V<sub>CC</sub>=PV<sub>CC</sub>=5 V 、V<sub>OUT</sub>=1.8 V 、L<sub>OUT</sub>=250 nH 、T<sub>A</sub>=25℃ 且为自然对流冷却,除非另有说明。

图 10. 功耗与驱动器电源电压之间的关系

图 11. 功耗与输出电压之间的关系

图 12. 功耗与输出电感器之间的关系

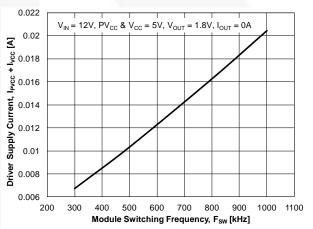

图 13. 驱动器电源电流与开关频率之间的关系

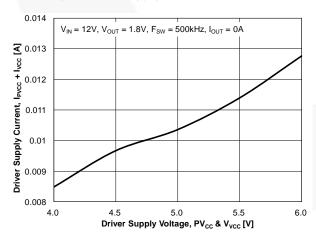

图 14. 驱动器电源电流与驱动器电源电压之间的关系

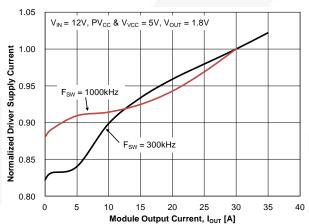

图 15. 驱动器电源电流与输出电流之间的关系

测试条件: V<sub>IN</sub>=12 V 、V<sub>CC</sub>=PV<sub>CC</sub>=5 V 、V<sub>OUT</sub>=1.8 V 、L<sub>OUT</sub>=250 nH 、T<sub>A</sub>=25°C 且为自然对流冷却,除非另有说明。

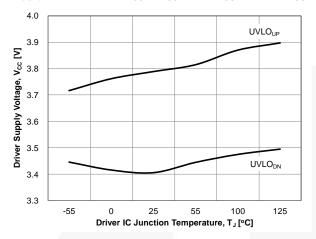

图 16. UVLO 阈值与温度的关系

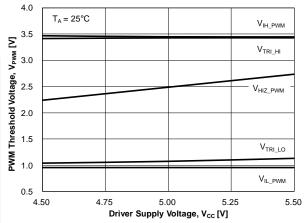

图 17. PWM 阀值与驱动器电源电压的关系

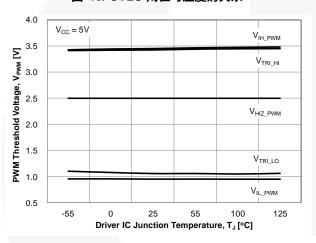

图 18. PWM 阈值与温度的关系

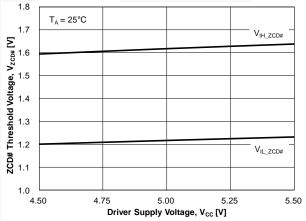

图 19. ZCD# 阀值与驱动器电源电压的关系

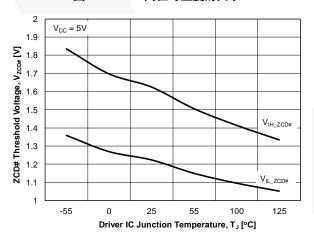

图 20. ZCD# 阈值与温度的关系

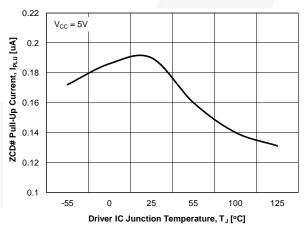

图 21. ZCD# 上拉电流与温度的关系

测试条件: V<sub>IN</sub>=12 V 、 V<sub>CC</sub>=PV<sub>CC</sub>=5 V 、V<sub>OUT</sub>=1.8 V 、L<sub>OUT</sub>=250 nH 、T<sub>A</sub>=25°C 且为自然对流冷却,除非另有说明。

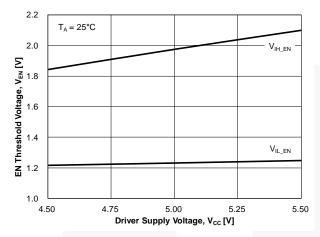

图 22. EN 阀值与驱动器电源电压的关系

图 23. EN 阈值与温度的关系

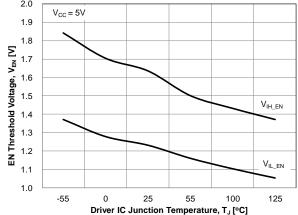

图 24. EN 下拉电流与温度的关系

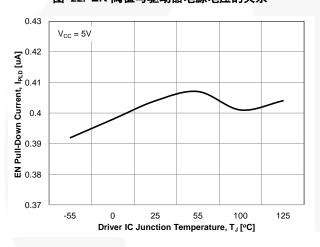

图 25. 自举二极管正向电压与温度的关系

图 26. 驱动器关断电流与温度的关系

图 27. 驱动器静态电流与温度的关系

#### 功能说明

SPS FDMF5839 是一个驱动器加 MOSFET 模块,已针对同步降压转换器拓扑进行优化。需要一个 PWM 输入信号来正确驱动高侧和低侧 MOSFET。该部分能够驱动高达 1.5 MHz 的频率。

#### 上电复位 (POR)

PWM 输入级应该包含 POR 特性,从而确保 LDRV 和 HDRV 在 UVLO>~ 3.8 V(上升阀值)之前被强制为非活动状态 (LDRV=HDRV=0)。待所有栅极驱动模块完全上电并且已完成启动时序,内部驱动器 IC EN\_PWM 信号就被释放为高电平,允许驱动器输出。一旦驱动器上电复位完成(< 最大 20 μs),驱动器继承 PWM 信号的状态(假定启动期间,控制器处于高电阻状态或强制 PWM 信号位于驱动器三态窗口以内)。

正常启动/上电必须支持下面三个条件。

- V<sub>CC</sub> 上升至 5 V, 然后 EN 变为高电平;

- EN 引脚绑定至 VCC 引脚;

- 在 5 V V<sub>CC</sub> 达到 UVLO 上升阀值之前, EN 被指令控制为高电平。

POR 方法旨在提高  $V_{CC}$ ,使 UVLO >上升阀值,且 EN=HIGH。

#### 欠压锁定 (UVLO)

UVLO 只在  $V_{CC}$  上进行,而不在  $PV_{CC}$  或  $V_{IN}$  上进行。当 EN 设置为高电平且  $V_{CC}$  上升超过 UVLO 阀值电平  $(3.8\ V)$ ,该部分在最大  $20\ \mu s$  POR 延迟后开始开关运行。该延迟的目的是确保内部电路偏置、稳定,并且已准备就绪可以运行。提供两个 VCC 引脚: PVCC 和 VCC。栅极驱动器电路由 PVCC 电轨供电。用户通过一个低通 R-C 滤波器将 PVCC 连接至 VCC。IC 上的模拟电路提供一个滤波后的  $5\ V$  偏压。

图 28. VCC 上的欠压锁定

#### EN/FAULT#(启用/故障标识)

通过将 EN/FAULT# 引脚拉至低电平 (EN<V<sub>IL\_EN</sub>) 可禁用驱动器,这时不管 PWM 输入状态如何都会保持 GL 和GH 低电平。通过将 EN/FAULT# 引脚升至高电平 (EN>V<sub>IH\_EN</sub>) 可启用驱动器。禁用时,驱动器 IC 具有小于  $3 \mu$ A 的关断电流。重新启用驱动器后,需要最长  $20 \mu$ S 的启动时间。

EN/FAULT# 引脚为故障标识的开漏输出,带有一个 250 kΩ 的内部下拉电阻。需要 PWM 控制器发出的逻辑高信号或从 EN/FAULT# 引脚到 VCC 的  $\sim$  10 kΩ 外部上拉电阻来启动驱动器运行。

表 1. UVLO 和启用逻辑

| UVLO | EN | 驱动器状态            |  |  |

|------|----|------------------|--|--|

| 0    | Х  | 禁用 (GH & GL = 0) |  |  |

| 1    | 0  | 禁用 (GH & GL = 0) |  |  |

| 1    | 1  | 启用(参见表 2)        |  |  |

| 1    | 打开 | 禁用 (GH & GL = 0) |  |  |

EN/FAULT# 引脚有两个功能:启用/禁用驱动器和故障标识。故障标识信号为低电平有效。当驱动器在运行期间检测到故障状况,它会导通 EN/FAULT# 引脚上的开漏并且引脚电压被拉至低电平。故障状况如下:

- 低侧 MOSFET 导通期间,高侧 MOSFET 错误导通或者 VIN ~ SW 短路:

- 因驱动器 T」为 150°C 出现热关断

当驱动器检测到一个故障状况并自行禁用,需要 VCC 上的 POR 事件来重新启动驱动器运行。

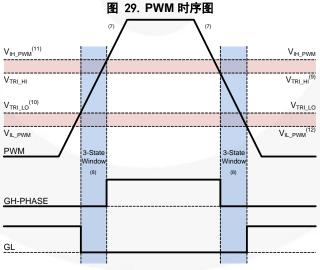

#### 三态 PWM 输入

FDMF5839 包含一个三态 5 V PWM 输入栅极驱动设计。三态栅极驱动同时具有逻辑高和低电平,以及三态关断窗口。当 PWM 输入信号进入并且保持在三态窗口内的时间为已定义的保持时间 (tp\_HOLD-OFF) 时,GL 和 GH 都被拉至低电平。该特性允许栅极驱动同时关断高侧和低侧MOSFET,从而支持诸如扩相等功能,扩相是多相稳压器上的一个常见功能。

表 2. EN/PWM/三态/ZCD# 逻辑状态

| EN | PWM | ZCD# | GH | GL                     |

|----|-----|------|----|------------------------|

| 0  | Х   | Х    | 0  | 0                      |

| 1  | 3 态 | Х    | 0  | 0                      |

| 1  | 0   | 0    | 0  | 1 (IL > 0), 0 (IL < 0) |

| 1  | 1   | 0    | 1  | 0                      |

| 1  | 0   | 1    | 0  | 1                      |

| 1  | 1   | 1    | 1  | 0                      |

t<sub>FALL\_GL</sub> = 90% GL to 10% GL

$t_{R,D,DEADON} = LS$  Off to HS On Dead Time, 10% GL to  $V_{BOOT-GND} <= PV_{CC} - V_{F,DBOOT} - 1V$  or BOOT-GND dip start point  $t_{R,SE\_GH} = 10\%$  GH to 90% GH,  $V_{BOOT-GND} <= PV_{CC} - V_{F,DBOOT} - 1V$  or BOOT-GND dip start point to GL bounce start point

$t_{PD\_PLGHL} = PWM\ LO\ to\ GH\ LO,\ V_{IL\_PWM}\ to\ 90\%\ GH\ or\ BOOT\text{-}GND\ decrease\ start\ point,}\ t_{PD\_PLGLH}\ ^*\ t_{D\_DEADOFF}\ ^*\ t_{FALL\_GH}$   $t_{FALL\_GH} = 90\%\ GH\ to\ 10\%\ GH,\ BOOT\text{-}GND\ decrease\ start\ point\ to\ 90\%\ V_{SW}\ or\ GL\ dip\ start\ point\ to\ 10\%\ GL$   $t_{DEADOFF} = HS\ Off\ to\ LS\ On\ Dead\ Time,\ 90\%\ V_{SW}\ or\ GL\ dip\ start\ point\ to\ 10\%\ GL$   $t_{RISE\_GL} = 10\%\ GL\ to\ 90\%\ GL$

t<sub>PD\_PLGLH</sub> = PWM LO to GL HI, V<sub>IL\_PWM</sub> to 10% GL

图 30. PWM 阀值定义

#### 注意:

- 7. 中的时序图 30 图假定 PWM 的斜坡非常缓和。

- 8. 较缓的 PWM 斜坡表示 PWM 信号保持在三态窗口内的时间 >>> t<sub>D\_HOLD-OFF</sub>。

- 9. V<sub>TRI\_HI</sub>=在 PWM 下降沿进入三态的 PWM 触发电平。

- 10. V<sub>TRI LO</sub>=在 PWM 上升沿进入三态的 PWM 触发电平。

- 11.  $V_{IH\_PWM}$ =在 PWM 上升沿退出三态并进入 PWM 逻辑高状态的 PWM 触发电平。

- 12. V<sub>IL\_PWM</sub>=在 PWM 下降沿退出三态并进入 PWM 逻辑低状态的 PWM 触发电平。

#### 上电顺序

SPS FDMF5839 需要四个(4)输入信号进行正常的 开关运行:  $V_{IN}$ 、 $V_{cc}/PV_{cc}$ 、PWM 和 EN。PWM 不应 VCC 之前应用和 PWM 的幅度不应该超过 VCC 更高。他们 的权力序列的所有其他组合被允。下面的上电顺序 实例可作为参考应用设计:

- 从没有输入信号开始

- -> V<sub>IN</sub> 导通: 典型 12 V<sub>DC</sub>

- -> Vcc/PVcc 导通: 典型 5 Vpc

- -> EN 高电平: 典型 5 V<sub>DC</sub>

- -> PWM 信今: 5 V 高电平 /0 V 低电平

VIN 引脚绑定至系统主要直流电源电轨。

PVCC 和 VCC 引脚绑定在一起,向栅极驱动和逻辑电路 提供来自系统  $V_{CC}$  电轨的电源。或者,PVCC 引脚可以 直接绑定至系统  $V_{CC}$  电轨,并且 VCC 引脚通过位于 PVCC 引脚和 VCC 引脚之间的滤波电阻由 PVCC 引脚 供电。滤波电阻能够减少从  $PV_{CC}$  到  $V_{CC}$  的开关噪声影响。

EN 引脚可以通过一个外部上拉电阻绑定至  $V_{CC}$  电轨,并且一旦  $V_{CC}$  电轨导通,该引脚则保持高电平。或者,EN 引脚可以直接连接至 PWM 控制器,用于其它用途。

### 高侧驱动器

高侧驱动器(HDRV)设计用来驱动一个浮置 N 沟道 MOSFET (Q1)。高侧驱动器的偏置电压由自举电源电路 形成,该电路包含内部肖特基二极管和外部自举电容器 ( $C_{BOOT}$ )。启动期间,SW 节点保持在 PGND,允许  $C_{BOOT}$  通过内部自举二极管向 PVCC 充电。当 PWM 输入变为高电平时,HDRV 开始向高侧 MOSFET 的栅极(内部 GH 引脚)充电。在该过渡过程中,电荷从  $C_{BOOT}$  中移除,并传输至 Q1 的栅极。当 Q1 导通时,SW 升至  $V_{IN}$ ,迫使 BOOT 引脚达到  $V_{IN}$  +  $V_{BOOT}$ ,从而为 Q1 提供充分的  $V_{GS}$  增强。为了完成开关周期,通过将 HDRV 拉至 SW 关断 Q1。当 SW 跌至 PGND 时,CBOOT 重新充电至 PVCC。HDRV 输出与 PWM 输入同相。当驱动器被禁用或 PWM 信号保持在三态窗口的时间超过三态保持时间  $t_{D_{HOLD-OFF}}$  时,高侧栅极保持在低电平。

#### 低侧驱动器

低侧驱动器 (LDRV) 设计用于驱动以大地为基准、低 RDS(ON). N 沟道 MOSFET (Q2) 的栅源极。LDRV 的内部偏置在内部连接于 PVCC 与 AGND 之间。当启用驱动器时,驱动器输出与 PWM 输入之间的相移为  $180^\circ$ 。当禁用驱动器时 (EN = 0 V),LDRV 保持低电平。

#### 连续电流模式 2 (CCM2) 运行

SPS FMDF5839 低侧驱动器设计的一个主要特性是能够在检测到负电感电流时控制低侧栅极驱动器部分,称为CCM2 运行。这是通过 ZCD 比较器信号实现的。按比例缩减驱动强度的主要原因是在低侧 MOSFET 硬开关电感电流时限制 V<sub>DS</sub> 峰值应力。该 V<sub>DS</sub> 峰值应力是包含大量负载瞬态和快速广泛的输出电压调节的应用中存在的一个问题。

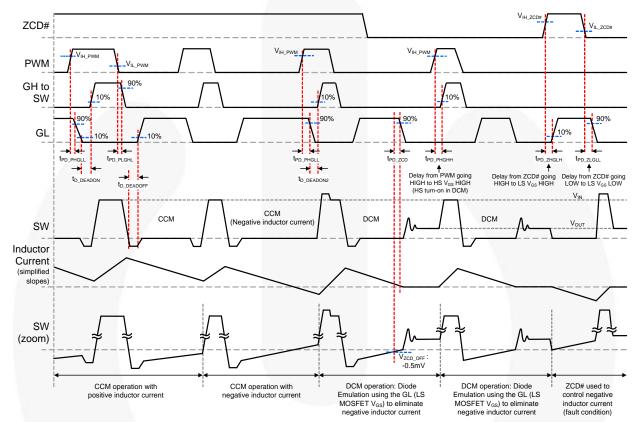

SPS FDMF5839 的 MOSFET 栅极驱动器在三种模式中的一种模式下运行,如下所述。

#### 包含正电感电流的连续电流模式 1 (CCM1)

在这种模式下,电感电流总是流向输出电容器,尤其是在重载功率级。高侧 MOSFET 通过传导电感电流的低侧体二极管导通,并且 SW 大约为低于接地电压的 V<sub>F</sub>,这意味着硬开关导通和关断高侧 MOSFET。

#### 非连续电流模式 (DCM)

通常在轻载功率级,高侧 MOSFET 在零电感电流时导通,随电感电流斜坡上升,然后再在每个开关周期回到零电流。当高侧 MOSFET 在 DCM 模式运行下导通时,SW 节点可能为低于接地电压的  $V_F$  到高于  $V_{IN}$  的  $V_F$  之间的任意电压。这是因为在低侧 MOSFET 关断后,SW 节点电容随电感电流谐振。

不管 SW 节点电压如何,驱动器 IC 中的电平转换器应该能够导通高侧 MOSFEMT。在这种情况下,高侧 MOSFET 关断正电流。

在该模式期间,LDRV1 和 LDRV2 并联运行并且低侧栅极驱动器上拉和下拉电阻以全强度运行。

#### 包含负电感电流的连续电流模式 2 (CCM2)

该模式通常用于同步降压转换器中,将能量从输出电容器中取出,然后将能量传输至输入电容器(间歇模式)。在这种模式下,当低侧 MOSFET 关断时,电感电流是负向的(即流向 MOSFET)(当高侧 MOSFET 导通时也可能为负向)。这种情况会导致,当高侧 MOSFET 用作同步整流器(暂时运行在同步间歇模式下)时,低侧 MOSFET 进行硬开关。

在该模式期间,只有"较弱的"LDRV2用于低侧 MOSFET 导通和关断。目的是在进行硬开关以减少 V<sub>DS</sub> 应力时,减缓低侧 MOSFET 的开关速度。

#### CCM1/DCM/CCM2 模式下的死区时间

驱动器 IC 设计确保最短 MOSFET 死区时间,同时去掉潜在的穿通(交叠导通)电流。为了确保最佳的模块效率,必须在 CCM1 和 DCM 模式运行期间将体二极管导通时间缩短至很小的毫微秒范围。当在与 CCM1/DCM 不同的模式下运行功率 MOSFET 时,CCM2 模式会改变栅极驱动电阻。必须考虑改变后的死区时间运行。

#### CCM1/DCM 模式下, 低侧 MOSFET 关断到高侧 MOSFET 导通死区时间

为了防止在低侧 MOSFET 关断到高侧 MOSFET 导通开 关过渡过程中出现交叠,采用一个自适应电路监控 GL 引脚电压。当 PWM 信号变为高电平时, GL 在一个传输 延迟 (tPD PHGLL) 后变为低电平。一旦 GL 引脚放电至低 于~1-2 V, GH 在一个自适应延迟 to DEADON 后被拉至 高电平。

在某些情况下, ZCD# 上升沿信号领先 PWM 上升沿 几十毫微秒, 这会导致出现 GH 和 GL 交叠。当 PWM 控制器发送领先、滞后的或同步的 PWM 和 ZCD# 信号时,可能出现这种情况。为了避免这种现象,添加 另外一个固定传输延迟 (tFD ON1), 确保在低侧 MOSFET 关断到高侧 MOSFET 导通之间总是存在最小延迟。

#### CCM2 模式下,低侧 MOSFET 关断到高侧 MOSFET 导 诵死区时间

如 CCM2 模式运行章节所述, 在检测到 CCM2 模式 时,低侧驱动器强度可以调整。CCM2 特性能够减缓低 侧 MOSFET 的充电和放电过程,从而在低侧 MOSFET 硬开关(负电感电流)期间最大程度地减少峰值开关电

压过冲。为了避免交叠导通, 低侧栅极的降速还需要调 整(增加)低侧 MOSFET 关断到高侧 MOSFET 导通之 间的死区时间。实现一个相当长的固定死区时间 (t<sub>FD ON2</sub>), 以确保在 CCM2 模式运行期间不存在交叠导

#### CCM1/DCM 模式下, 高侧 MOSFET 关断到低侧 MOSFET 导诵死区时间

为了在高侧 MOSFET 关断到低侧 MOSFET 导通过渡过 程中获得非常短的死区时间,需要在 SPS 栅极驱动器中 实现一个固定的死区时间方法。固定死区时间电路监控 内部 HS 信号, 并且不管 SW 节点状态如何都会在所需 t<sub>D\_DEADOFF</sub> (~ 5 ns, t<sub>D\_DEADOFF</sub>=t<sub>FD\_OFF1</sub>) 后添加一个足够 长的固定延迟至 GL 栅极。

#### 退出三态状况

当退出有效的三态状况时, FDMF5839 的栅极驱动器会 执行 PWM 输入指令。如果 PWM 输入由三态变为低电 平,则导通低侧 MOSFET。如果 PWM 输入由三态变为 高电平,则导通高侧 MOSFET。如下面图 31 所示。

to\_\_xxx = propagation delay from external signal (PWM, ZCD#, etc.) to IC generated signal. Example : to\_DPHGLL - PWM going HIGH to low-side MOSFET VGS (GL) going LOW to\_xxx = delay from IC generated signal to IC generated signal. Example : to\_DEADON - low-side MOSFET VGS LOW to high-side MOSFET VGS HIGH

FYMM  $t_{PO\_PHGLL}$  = PWM rise to LS  $V_{GS}$  fall,  $V_{IL\_PWM}$  to 90% LS  $V_{GS}$  to  $p\_FGHL$  = PWM fall to HS  $V_{GS}$  fall,  $V_{IL\_PWM}$  to 90% HS  $V_{GS}$   $t_{PO\_PHGHH}$  = PWM rise to HS  $V_{GS}$  rise,  $V_{IH\_PWM}$  to 10% HS  $V_{GS}$  (ZCD# held LOW)

tpD\_ZIGLL = ZCD# fall to LS V<sub>GS</sub> fall, V<sub>IL\_ZCD#</sub> to 90% LS V<sub>GS</sub> tpD\_ZHGLH = ZCD# rise to LS V<sub>GS</sub> rise, V<sub>IH\_ZCD#</sub> to 10% LS V<sub>GS</sub>

Exiting 3-State  $t_{PD\_TSGHH}$  = PWM 3-State to HIGH to HS  $V_{GS}$  rise,  $V_{IH\_PWM}$  to 10% HS  $V_{GS}$ tpd TSGLH = PWM 3-State to LOW to LS VGS rise, VIL PWM to 10% LS VGS

图 31. PWM 高电平/低电平/三态时序图

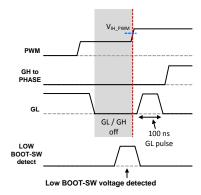

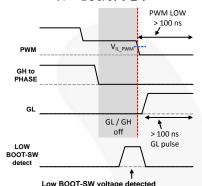

#### 以较低的 BOOT-SW 电压退出三态

SPS 模块用于多相 VR 拓扑中,需要该模块在三态状况中等待一个不确定的时间。较长的空闲时间会致使自举电容器逐渐放电,直至根据 PVcc 和 Vout 最终出现钳位。较低的 BOOT-SW 电压可能导致电平转换电路以及所有 HDRV 浮置电路的传输延迟增加,是从 BOOT-SW 电轨偏置。逐渐耗尽的 BOOT-SW 电容器电压还可能导致另一个问题,即在导通期间施加到 HS MOSFET 栅极的电压。较低的 BOOT-SW 电压会导致非常弱的 HS 栅极驱动,因此,会增大 HS RDS(ON) 并增加不可靠运行的风险,这是因为如果 BOOT-SW 跌得太低,HS MOSFET 可能不会导通。

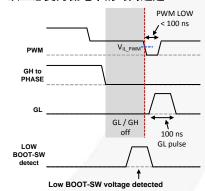

为了解决这个问题,当模块在三态状况时,SPS 监控较低的 BOOT-SW 电压。当模块以较低的 BOOT-SW 电压 退出三态状况时,不管 PWM 输入如何都会输出一个 100 ns 的最短 GL 导通 时间。这样就能确保自举电容器会被充分充电至一个安全的工作电平并且最小化对系统 瞬态响应的影响。下面列举退出三态状况的场景。

- 如果该部分以较低的 BOOT-SW 电压退出三态状况并且控制器发出 PWM=HIGH 的指令, SPS 会输出一个 100 ns 的 GL 脉冲并且执行 PWM=HIGH 指令(参见图 32)。

- 如果该部分以较低的 BOOT-SW 电压退出三态状况并且控制器发出 PWM=LOW 指令的时间为 100 ns 或 更 长, SPS 执 行 PWM 输入的指令。如果 PWM=LOW 的时间少于 100 ns,GL 保持导通 100 ns,然后执行 PWM 输入的指令(参见图 33 和 图 34)。

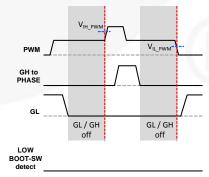

- 如果未检测到低 BOOT-SW 电压状况,在退出三态时,SPS 执行 PWM 指令(参见图 35)。

在退出三态状况或在初始上电时, SPS 短暂停留在自适应死区时间模式中。自适应死区时间模式持续时间不超过两个 (2) 连续的开关周期, 从而为自举电容器提供足够的时间充电至一个安全的电平。模块会切换回固定的死区时间控制, 从而实现最大的效率。

图 32. 检测到较低的 BOOT-SW 电压并且 PWM 从三态变为高电平

图 33. 检测到较低的 BOOT-SW 电压并且 PWM 从三态变为低电平的时间超过 100 ns

图 34. 检测到较低的 BOOT-SW 电压并且 PWM 从三态变为低电平的时间少于 100 ns

Low BOOT-SW voltage NOT detected

图 35. 未检测到较低的 BOOT-SW 电压并且 PWM 从三态变为高电平或低电平

#### 过零检测 (ZCD) 运行

ZCD 控制模块包含用于确定电感电流何时反向并且控制何时关断低侧 MOSFET 的电路。低偏移比较器在 LS MOSFET 导通期间监控低侧 MOSFET 的 SW 至 PGND电压。当感测电压的极性从负改为正时,比较器会改变状态并且已检测到反向电流。该比较器偏移必须在最差为 0.5 mV 的范围内检测负 V<sub>SW</sub>。负偏移旨在确保电感电

流从不反向;一些小的体二极管导通更倾向于具有负电 流。

比较器在低侧栅极驱动上升沿过后导通,由低侧栅极驱动器的输入信号关断。这样一来,零电流比较器连接到一个先断后合连接,允许用所有低电压晶体管设计该比较器。

图 36. ZCD# & PWM 时序图

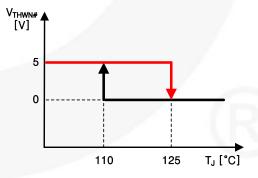

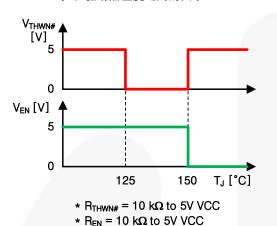

### 热警告标识 (THWN#)

FDMF5839 提供一个针对过温状况的热警告 (THWN) 功能。如果驱动器 IC 检测到 125°C 激活温度,THWN 标识会将 THWN# 引脚拉至低电平(至 AGND)。一旦温度降至 110°C 重置温度,THWN# 引脚输出返回至高电阻状态。图 37 显示 THWN# 运行状况。THWN 不会禁用 SPS 模块并且独立于其它功能工作。

THWN 模式运行需要一个到 Vcc 电轨的上拉电阻。THWN# 标识低电平有效。

#### 热关断 (THDN)

一旦驱动器  $T_J$ 达到  $150^{\circ}$ C,就会触发已编程热关断。关断事件为闩锁关断,其中 THDN 信号对故障闩锁进行计时并且在物理上拉低 EN 引脚。

若要重新启用驱动器 IC,需要重新循环  $5 \ V_{CC}$ (POR事件)。

\*  $R_{THWN\#}$  = 10 k $\Omega$  to 5V VCC

图 37. 栅极驱动器 T」与 VTHWN# 的关系

150°C THDN 特性与 125°C THWN# 标识相结合。如果驱动器温度达到 125°C, THWN# 引脚被拉至低电平。如果驱动器继续运行并且其温度上升至 150°C, 会激活热关断。SPS 模块由 EN 低电平关断并且 THWN# 标识被去断言,因此 VTHWN# 回到高电平。图 38 显示THWN#、EN,和驱动器温度之间的关系。

图 38. VTHWN#、VEN 与驱动器温度之间的关系

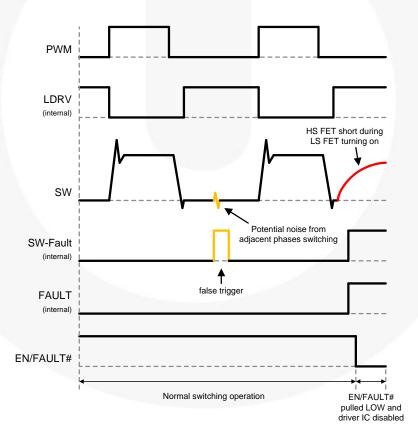

#### 灾难性故障

SPS FDMF5839 包含一个灾难性故障特性。如果检测到 HS MOSFET 短路,驱动器会在内部拉低 EN/FAULT# 引脚并关断 SPS 驱动器。目的是实现一个基本电路,通过监控 LDRV 和 SW 节点状态测试 HS MOSFET 短路。

如果检测到 HS 短路故障,SPS 模块会对故障闩锁进行计时,关断模块。若要重启该模块,需要一个  $V_{CC}$  POR 事件。

图 39. 灾难性故障波形

#### 应用信息

### PVCC 和 VCC 去耦合电容器

对于电源输入(PVCC 和 VCC 引脚),需要局部去耦合电容器在开关运行过程中提供峰值驱动电流,减少噪声。将至少 0.68 ~ 1 μF/0402 ~ 0603/X5R ~ X7R 多层陶瓷电容器用于两个电源电轨。使这些电容器靠近 PVCC 和VCC 引脚以及 PGND 和 AGND 覆铜面。如果需要将这些电容器放置在电路板底面,在去耦合电容器的每个焊盘上设置通孔,使底部的电容器焊盘连接至顶部的 PVCC和 VCC 引脚。

PVCC 和 VCC 电源电压范围是  $4.5 \text{ V} \sim 5.5 \text{ V}$ ,常规应用的典型电压为 5 V。

#### VCC 上的 R-C 滤波器

PVCC 引脚提供高侧和低侧功率 MOSFET 的栅极驱动电源。多数情况下,PVCC 可以直连至 VCC,该引脚为驱动器的模拟和逻辑模块提供电源。为了避免开关噪声从PVCC 注入 VCC,可在 PVCC 和 VCC 去耦合电容器之间插入一个滤波电阻。

推荐滤波电阻取值 范围是 0 ~ 10  $\Omega$ , 多数应用的典型值 为 0  $\Omega$ 。

#### 自举电路

自举电路采用一个电荷存储电容器( $C_{BOOT}$ )。一个0.1~0.22  $\mu$ F/0402~0603/X5R~X7R 的自举电容器通常适用于多数开关应用。具体应用可能需要一个串联自举电阻,从而降低高侧 MOSFET 的开关速度。当 SPS 的开关电压 超过 15 V  $V_{IN}$  时或者能够有效控制  $V_{SW}$  过冲时,需要自举电阻。通常推荐采用零至 6  $\Omega$  的  $R_{BOOT}$  值,以减少SW 节点上的过多电压尖峰和振铃。由于高侧 MOSFET较高的开关损耗,较高的  $R_{BOOT}$  值可能导致效率降低。

不要在 BOOT 引脚和 GND 之间添加电容器或电阻器。

#### EN/FAULT#(输入/输出)

通过将 EN 引脚拉至高电平启用 SPS 中的驱动器。EN 引脚有 250 k $\Omega$  的内部下拉电阻,因此需要通过一个外部电阻器上拉至  $V_{CC}$ ,或连接至控制器或系统,以执行它们发出的指令。如果 EN 引脚浮置,该引脚就不能导通驱动器。

当驱动器温度达到 THDN 温度或者出现高侧 MOSFET 故障时,故障标识低电平信号在 EN/FAULT# 引脚上被断言。然后,驱动器关断。

EN ~ VCC 上的典型上拉电阻值是 10 k $\Omega$ 。不要在 EN 引脚上添加噪声滤波电容器。

#### PWM(输入)

PWM 引脚识别 PWM 控制器发出的三个不同逻辑电平:高电平、低电平、三态 当 PWM 引脚接收一个高电平指令,栅极驱动器导通高侧 MOSFET。当 PWM 引脚接收一个低电平指令,栅极驱动器导通低侧 MOSFET。当 PWM 引脚接收到一个三态窗口 (V<sub>TRI\_Window</sub>) 内的电压信号并且超过了三态延迟时间,栅极驱动器同时关断高侧和低侧 MOSFET。为了识别控制器发出的高电阻三态信号,PWM 引脚包含一个从 VCC 到 PWM,然后到AGND 的电阻分压器。当控制器发出的 PWM 信号为高电阻时,电阻分压器在 PWM 引脚上设置一个三态窗口内的电压电平。

#### ZCD#(输入)

当 ZCD# 引脚设置为高电平时, ZCD 功能被禁用, 并且高侧和低侧 MOSFET 在 CCM(或 FCCM(强制 CCM)模式)下根据 PWM 信号进行开关。当 ZCD# 引脚为低电平时, 在低侧 MOSFET 导通期间, 低侧 MOSFT 在SPS 驱动器检测到负电感电流时关断。该 ZCD 特性允许在轻载状况和 PFM/DCM 模式运行时提高转换器效率。

ZCD# 引脚有一个来自 VCC 的内部电流源,因此可能无需使用外部上拉电阻。一旦向 Vcc 供电并且启用驱动器,ZCD# 引脚保持逻辑高电平,无需外部元件,并且驱动器在 CCM 或 FCCM 模式下进行开关运行。ZCD# 引脚可接地,以便由 SPS 自己在 DCM 模式下进行自动二极管模拟,或者可以将其连接到控制器或系统,以执行它们发出的指令。

ZCD# ~ VCC 上的典型上拉电阻值为 10 kΩ, 用于确保稳定的 ZCD# 高电平。如果不使用 ZCD 功能, 用一个上拉电阻将 ZCD# 引脚绑定至 VCC。不要在 ZCD# 引脚上添加任何噪声滤波电容器。

#### THWN#(输出)/THDN

THWN# 引脚为开漏,因此需要一个至 VCC 的外部上拉电阻。如果驱动器温度达到  $125^{\circ}$ C, $V_{THWN#}$  被拉至低电平。当驱动器 T」冷却至低于  $110^{\circ}$ C 时, $V_{THWN#}$  重新回到高电平。当驱动器 T」低于  $150^{\circ}$ C 时,THWN# 标识运行。

在断言  $125^{\circ}$ C THWN 标识后,如果驱动器 T<sub>J</sub> 持续升高超过  $150^{\circ}$ C,会激活热关断功能,并且 SPS 模块被关断。该关断是一个闩锁功能,因此即使温度下降至  $25^{\circ}$ C,驱动器仍保持关断。一旦激活 THDN,SPS 模块需要由  $V_{CC}$  POR 重新启用。

THWN# ~ VC 典型上拉电阻是 10 kΩ。如果不使用 THWN#/THDN 功能,将 THWN# 绑定至 GND。不要在 THWN# 引脚上添加噪声滤波电容器。

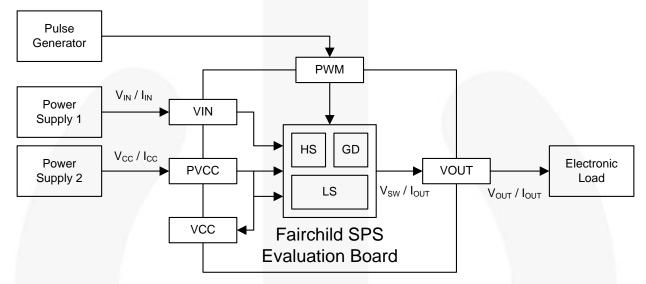

# 功耗和效率

图 41 显示功耗和效率测量的示意图。

#### 功耗计算和方程式示例:

$$\begin{array}{lll} P_{IN} = (V_{IN} * I_{IN}) + (V_{CC} * I_{CC}) & [W] \\ P_{SW} = V_{SW} * I_{OUT} & [W] \\ P_{OUT} = V_{OUT} * I_{OUT} & [W] \\ P_{LOSS\_MODULE} = P_{IN} - P_{SW} & [W] \\ P_{LOSS\_TOTAL} = P_{IN} - P_{OUT} & [W] \\ EFFI_{MODULE} = (P_{SW} / P_{IN}) * 100 & [\%] \\ EFFI_{TOTAL} = (P_{OUT} / P_{IN}) * 100 & [\%] \end{array}$$

图 41. 功耗和效率测量示意图

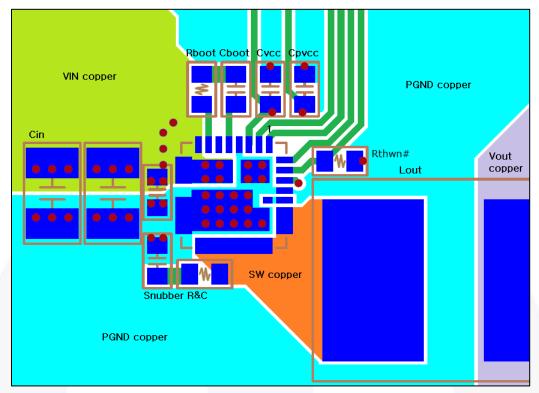

### PCB 布局指南

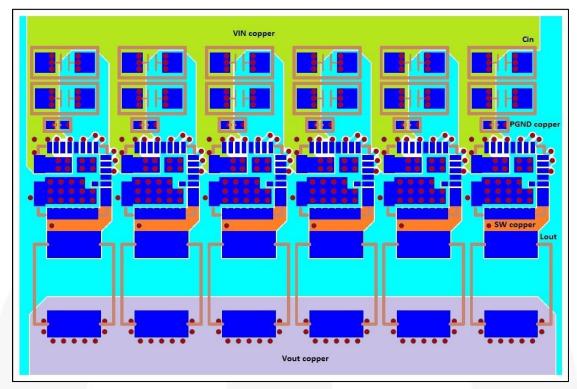

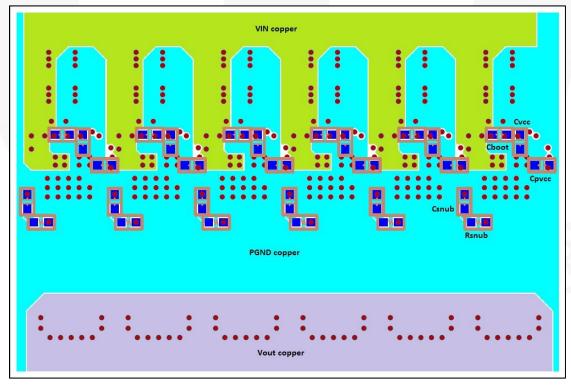

图 42 至图 45 提供了 FDMF5839 和关键元件的单相和 多相布局示例。所有大电流路径如 VIN、SW、VOUT 和 GND 覆铜都应该尽量短而宽,以减小寄生电感和电阻。 这有助于实现更加稳定、均匀分布的电流,以及增强的热辐射和系统性能。

输入陶瓷旁路电容器必须靠近 VIN 和 PGND 引脚。这是为了减少大电流电源回路电感和功率 MOSFET 开关运行感应的输入电流纹波。

SW 铜引线有两个用途。除了作为从 SPS 封装到输出电感器的高频电流路径,它还用作低侧 MOSFET 的散热器。引线应该足够短而宽,从而为 SPS 和电感器之间的高频大电流提供一个低电阻路径。短而宽的引线能够最大程度地减少电力损耗和 SPS 温升。SW 节点是具有高噪声电势的高电压高频率开关节点。必须注意最小化与相邻引线的耦合。由于铜引线用作低侧 MOSFET 的散热器,使用可能的最大面积进行平衡,从而改善 SPS 冷却效果,同时保持可以接受的噪声发射。

输出电感器应该靠近 FDMF5839 放置,以减少由 SW 铜引线产生的功耗。还应该注意电感器散热不会使 SPS 变热。

在输出级使用 PowerTrench® MOSFET, 能够有效地最小化由于快速开关产生的振铃。多数情况下, 无需在 SW 节点上使用 RC 缓冲电路。若要使用缓冲电路, 该电路应该靠近 SW 和 PGND 引脚放置。缓冲电路的电阻器和电容器的大小必须合适,以确保不会因为高功散产生过多热量

PVCC、VCC 和 BOOT 电容器的去耦合电容器必须尽量 靠近 PVCC ~ PGND、VCC ~ AGND 和 BOOT ~ PHASE 引脚对,以确保干净稳定的电源。它们的布线应 该短而宽,以最小化 PCB 寄生电阻和电感。

电路板布局应该包含一个用于 BOOT  $\sim$  PHASE 小值串联 自举电阻的占位符。自举回路的大小,包括串联  $R_{BOOT}$ 和  $C_{BOOT}$ ,应该尽可能得小。

当 SPS 的工作电压超过  $15 \text{ V V}_{\text{IN}}$  并且它能够有效控制高侧 MOSFET 导通压摆率和 SW 电压过冲时,可能需要一个自举电阻器。在同步降压设计中,由于地面反弹或较高的正负 VSW 振铃,可能存在噪声问题,RBOOT 可以改善其噪声运行余量。插入一个自举电阻能够降低 SPS 模块效率。必须考虑效率与开关噪声之间的关系。通常来说,RBOOT 取值范围为  $0.5 \Omega$  至  $6.0 \Omega$  时能够有效减少  $V_{\text{SW}}$  过冲。

VIN 和 PGND 引脚通过高于 100 MHz 的频率元件来处理较大的电流瞬态。如果可能,这些引脚应该直连至 VIN 和电路板 GND 平面。不推荐采用降温引线与这些引脚串联,因为这会增加额外的寄生电感至电源路径。与 VIN或 PGND 引脚串联增加的电感会增加正向和负向 V<sub>SW</sub> 振铃,因而会降低系统的抗噪声能力。

PGND 焊盘和引脚应该通过多个过孔连接至 GND 覆铜面,以确保稳定接地。接地不良可能在 PGND 和 AGND 之间产生噪声 和瞬态偏移电压电平。这可能会导致栅极驱动器和 MOSFET 故障运行。

BOOT 引脚振铃可以通过靠近放置自举电容器得到最有效的控制。不要在 BOOT 到 PGND 之间添加任何额外电容器。这可能会导致通过 BOOT 二极管的电流过大,进而导致较高的功散。

ZCD# 和 EN 引脚分别具有较弱的上拉和下拉电流源。 这些引脚不应有任何噪声滤波电容器。除非绝对必要,不 要浮置这些引脚。

在 VIN 和 VOUT 覆铜区域设置多个过孔,以相互连接顶层、内层和底层,从而均匀分布电流和热传导。不要在SW 覆铜区域设置太多过孔,以避免开关波形中出现额外寄生电感和噪声。只要效率和热性能可以接受,在顶层仅设置一个 SW 铜节点,不要在 SW 覆铜上设置过孔,以最小化开关节点寄生噪声。过孔应该相对较大,并且具有相当低的电感。关键高频元件,如 RBOOT、CBOOT、RC缓冲电路和旁路电容器应该尽可能地靠近 PCB 板顶层对应的 SPS 模块引脚。如果不可行,可以将它们设置在电路板底面,通过一个低电感过孔网络将它们的引脚从底部连接到顶部。

# PCB 布局指南 (接上页)

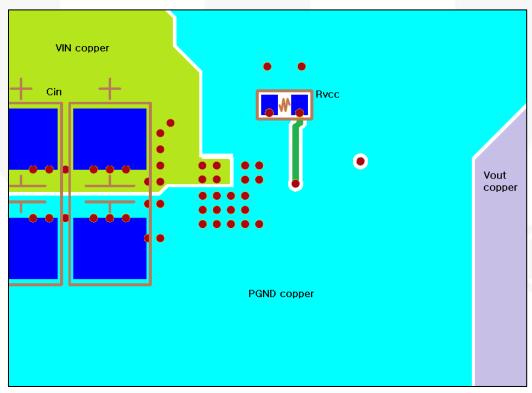

图 42. 单相电路板布局示例-俯视图

图 43. 单相电路板布局示例—仰视图 (镜像)

# PCB 布局指南 (接上页)

图 44. 包含 6 mm x 6 mm 电感器的 6 相电路板布局示例-俯视图

图 45. 包含 6 mm x 6 mm 电感器的 6 相电路板布局示例-仰视图 (镜像)

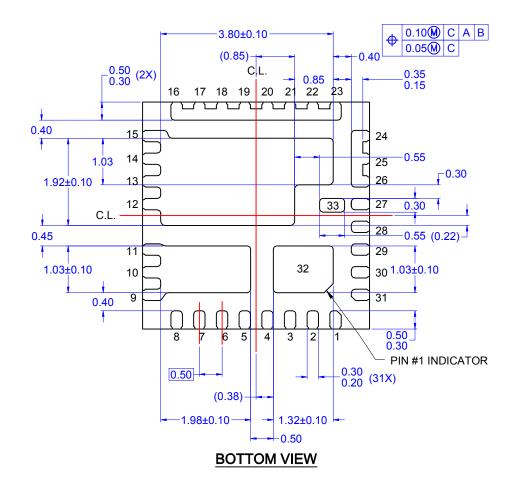

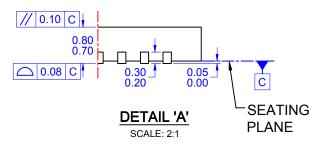

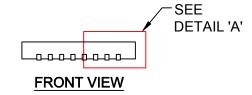

NOTES: UNLESS OTHERWISE SPECIFIED

- A) DOES NOT FULLY CONFORM TO JEDEC REGISTRATION MO-220, DATED MAY/2005.

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS DO NOT INCLUDE BURRS OR MOLD FLASH. MOLD FLASH OR BURRS DOES NOT EXCEED 0.10MM.

- D) DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- E) DRAWING FILE NAME: MKT-PQFN31BREV3

LAND PATTERN RECOMMENDATION

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and h

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative