# **Programmable Divide-By-N Dual 4-Bit Binary/BCD Down** Counter

# MC14569B

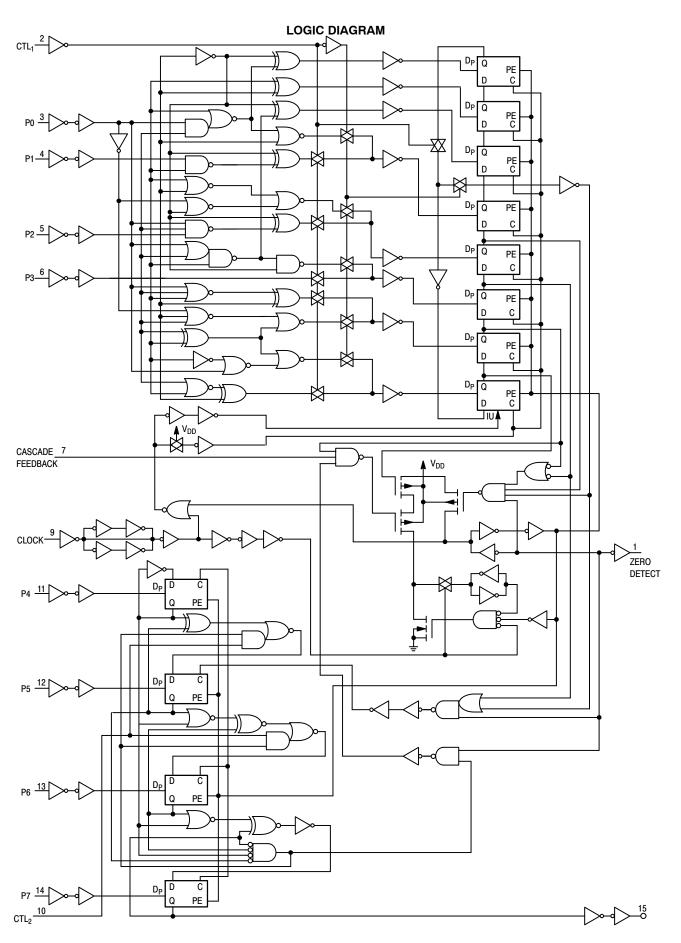

The MC14569B is a programmable divide-by-N dual 4-bit binary or BCD down counter constructed with MOS P-Channel and N-Channel enhancement mode devices (complementary MOS) in a monolithic structure.

This device has been designed for use with the MC14568B phase comparator/counter in frequency synthesizers, phase-locked loops, and other frequency division applications requiring low power dissipation and/or high noise immunity.

#### **Features**

- Speed-up Circuitry for Zero Detection

- Each 4-Bit Counter Can Divide Independently in BCD or Binary Mode

- Can be Cascaded With MC14526B for Frequency Synthesizer **Applications**

- · All Outputs are Buffered

- Schmitt Triggered Clock Conditioning

- NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- This Device is Pb-Free and is RoHS Compliant

### **MAXIMUM RATINGS** (Voltages Referenced to V<sub>SS</sub>)

| Symbol                             | Parameter                                         | Value                         | Unit |

|------------------------------------|---------------------------------------------------|-------------------------------|------|

| $V_{DD}$                           | DC Supply Voltage Range                           | -0.5 to +18.0                 | V    |

| V <sub>in</sub> , V <sub>out</sub> | Input or Output Voltage Range (DC or Transient)   | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| I <sub>in</sub> , I <sub>out</sub> | Input or Output Current (DC or Transient) per Pin | ±10                           | mA   |

| P <sub>D</sub>                     | Power Dissipation, per Package (Note 1)           | 500                           | mW   |

| T <sub>A</sub>                     | Ambient Temperature Range                         | -55 to +125                   | °C   |

| T <sub>stg</sub>                   | Storage Temperature Range                         | -65 to +150                   | °C   |

| TL                                 | Lead Temperature<br>(8-Second Soldering)          | 260                           | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Temperature Derating: "D/DW" Package: -7.0 mW/°C From 65 °C To 125 °C

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, Vin and Vout should be constrained to the range  $V_{SS} \le (V_{in} \text{ or } V_{out}) \le V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>). Unused outputs must be left open.

1

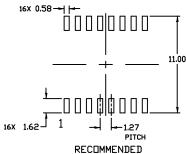

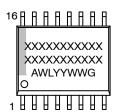

SOIC-16 WR **DW SUFFIX CASE 751G**

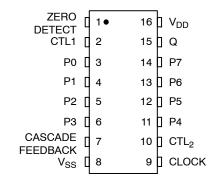

### **PIN ASSIGNMENT**

#### **MARKING DIAGRAM**

= Assembly Location

WL = Wafer Lot

YY = Year ww = Work Week = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

NOTE: Some of the devices on this data sheet have been **DISCONTINUED**. Please refer to the table on page 2.

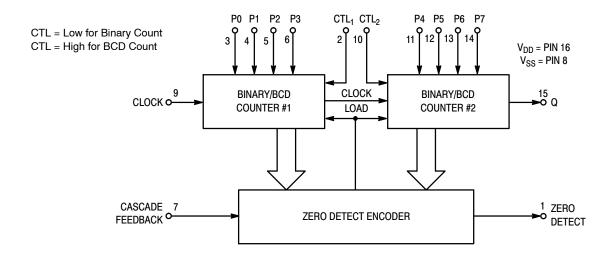

# **BLOCK DIAGRAM**

#### **ORDERING INFORMATION**

| Device          | Package                 | Shipping <sup>†</sup> |

|-----------------|-------------------------|-----------------------|

| NLV14569BDWR2G* | SOIC-16 WB<br>(Pb-Free) | 1000 / Tape & Reel    |

## **DISCONTINUED** (Note 2)

| MC14569BDWG   | SOIC-16 WB<br>(Pb-Free) | 47 Units / Rail    |

|---------------|-------------------------|--------------------|

| MC14569BDWR2G | SOIC-16 WB<br>(Pb-Free) | 1000 / Tape & Reel |

<sup>†</sup> For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup> NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

<sup>2.</sup> **DISCONTINUED:** These devices are not available. Please contact your **onsemi** representative for information. The most current information on these devices may be available on <a href="https://www.onsemi.com">www.onsemi.com</a>.

### **ELECTRICAL CHARACTERISTICS** (Voltages Referenced to V<sub>SS</sub>)

|                                                                                                                                           |           |                                                                                                                                                                          |                        | - 55                          | 5 °C                 |                               | 25 °C                          |                      | 125                           | s °C                 |      |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------|----------------------|-------------------------------|--------------------------------|----------------------|-------------------------------|----------------------|------|

| Characteristic                                                                                                                            | <b>:</b>  | Symbol                                                                                                                                                                   | V <sub>DD</sub><br>Vdc | Min                           | Max                  | Min                           | Typ<br>(Note 3)                | Max                  | Min                           | Max                  | Unit |

| Output Voltage<br>V <sub>in</sub> = V <sub>DD</sub> or 0                                                                                  | "0" Level | V <sub>OL</sub>                                                                                                                                                          | 5.0<br>10<br>15        | -<br>-<br>-                   | 0.05<br>0.05<br>0.05 | -<br>-<br>-                   | 0<br>0<br>0                    | 0.05<br>0.05<br>0.05 | -<br>-<br>-                   | 0.05<br>0.05<br>0.05 | Vdc  |

| $V_{in} = 0$ or $V_{DD}$                                                                                                                  | "1" Level | V <sub>OH</sub>                                                                                                                                                          | 5.0<br>10<br>15        | 4.95<br>9.95<br>14.95         | -<br>-<br>-          | 4.95<br>9.95<br>14.95         | 5.0<br>10<br>15                |                      | 4.95<br>9.95<br>14.95         | -<br>-<br>-          | Vdc  |

| Input Voltage<br>(V <sub>O</sub> = 4.5 or 0.5 Vdc)<br>(V <sub>O</sub> = 9.0 or 1.0 Vdc)<br>(V <sub>O</sub> = 13.5 or 1.5 Vdc)             | "0" Level | V <sub>IL</sub>                                                                                                                                                          | 5.0<br>10<br>15        | -<br>-<br>-                   | 1.5<br>3.0<br>4.0    | -<br>-<br>-                   | 2.25<br>4.50<br>6.75           | 1.5<br>3.0<br>4.0    | -<br>-<br>-                   | 1.5<br>3.0<br>4.0    | Vdc  |

| $(V_O = 0.5 \text{ or } 4.5 \text{ Vdc})$<br>$(V_O = 1.0 \text{ or } 9.0 \text{ Vdc})$<br>$(V_O = 1.5 \text{ or } 13.5 \text{ Vdc})$      | "1" Level | V <sub>IH</sub>                                                                                                                                                          | 5.0<br>10<br>15        | 3.5<br>7.0<br>11              | -<br>-<br>-          | 3.5<br>7.0<br>11              | 2.75<br>5.50<br>8.25           |                      | 3.5<br>7.0<br>11              | -<br>-<br>-          | Vdc  |

| Output Drive Current $(V_{OH} = 2.5 \text{ Vdc})$ $(V_{OH} = 4.6 \text{ Vdc})$ $(V_{OH} = 9.5 \text{ Vdc})$ $(V_{OH} = 13.5 \text{ Vdc})$ | Source    | I <sub>OH</sub>                                                                                                                                                          | 5.0<br>5.0<br>10<br>15 | -3.0<br>-0.64<br>-1.6<br>-4.2 | -<br>-<br>-          | -2.4<br>-0.51<br>-1.3<br>-3.4 | -4.2<br>-0.88<br>-2.25<br>-8.8 | -<br>-<br>-          | -1.7<br>-0.36<br>-0.9<br>-2.4 | -<br>-<br>-          | mAdc |

| (V <sub>OL</sub> = 0.4 Vdc)<br>(V <sub>OL</sub> = 0.5 Vdc)<br>(V <sub>OL</sub> = 1.5 Vdc)                                                 | Sink      | I <sub>OL</sub>                                                                                                                                                          | 5.0<br>10<br>15        | 0.64<br>1.6<br>4.2            | -<br>-<br>-          | 0.51<br>1.3<br>3.4            | 0.88<br>2.25<br>8.8            | -<br>-<br>-          | 0.36<br>0.9<br>2.4            | -<br>-<br>-          | mAdc |

| Input Current                                                                                                                             |           | I <sub>in</sub>                                                                                                                                                          | 15                     | -                             | ±0.1                 | -                             | ±0.00001                       | ±0.1                 | -                             | ±1.0                 | μAdc |

| Input Capacitance<br>(V <sub>in</sub> = 0)                                                                                                |           | C <sub>in</sub>                                                                                                                                                          | -                      | -                             | -                    | -                             | 5.0                            | 7.5                  | _                             | -                    | pF   |

| Quiescent Current<br>(Per Package)                                                                                                        |           | I <sub>DD</sub>                                                                                                                                                          | 5.0<br>10<br>15        | -<br>-<br>-                   | 5.0<br>10<br>20      | -<br>-<br>-                   | 0.005<br>0.010<br>0.015        | 5.0<br>10<br>20      | -<br>-<br>-                   | 150<br>300<br>600    | μAdc |

| Total Supply Current (No<br>(Dynamic plus Quiescer<br>Per Package)<br>(C <sub>L</sub> = 50 pF on all outpu<br>buffers switching)          | nt,       | 5) $I_T$ 5.0 $I_T = (0.58 \mu\text{A/kHz})  \text{f} + I_{DD}$ 10 $I_T = (1.20 \mu\text{A/kHz})  \text{f} + I_{DD}$ 15 $I_T = (1.95 \mu\text{A/kHz})  \text{f} + I_{DD}$ |                        |                               |                      |                               |                                | μAdc                 |                               |                      |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

4. The formulas given are for the typical characteristics only at 25 °C.

5. To calculate total supply current at loads other than 50 pF:

I<sub>T</sub>(C<sub>L</sub>) = I<sub>T</sub>(50 pF) + (C<sub>L</sub> – 50) Vfk

where: I<sub>T</sub> is in μA (per package), C<sub>L</sub> in pF, V = (V<sub>DD</sub> – V<sub>SS</sub>) in volts, f in kHz is input frequency, and k = 0.001.

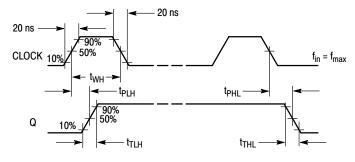

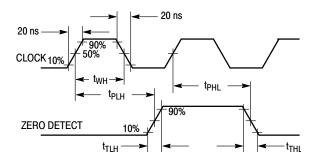

# SWITCHING CHARACTERISTICS ( $C_L$ = 50 pF, $T_A$ = 25 °C)

|                                           |                                     |                        |                   | All Types          |                    |      |

|-------------------------------------------|-------------------------------------|------------------------|-------------------|--------------------|--------------------|------|

| Characteristic                            | Symbol                              | V <sub>DD</sub><br>Vdc | Min               | Typ<br>(Note 6)    | Max                | Unit |

| Output Rise Time                          | t <sub>TLH</sub>                    | 5.0<br>10<br>15        | -<br>-<br>-       | 100<br>50<br>40    | 200<br>100<br>80   | ns   |

| Output Fall Time                          | t <sub>THL</sub>                    | 5.0<br>10<br>15        | -<br>-<br>-       | 100<br>50<br>40    | 200<br>100<br>80   | ns   |

| Turn-On Delay Time<br>Zero Detect Output  | t <sub>PLH</sub>                    | 5.0<br>10<br>15        | -<br>-<br>-       | 420<br>175<br>125  | 700<br>300<br>250  | ns   |

| Q Output                                  |                                     | 5.0<br>10<br>15        | -<br>-<br>-       | 675<br>285<br>200  | 1200<br>500<br>400 | ns   |

| Turn-Off Delay Time<br>Zero Detect Output | t <sub>PHL</sub>                    | 5.0<br>10<br>15        | -<br>-<br>-       | 380<br>150<br>100  | 600<br>300<br>200  | ns   |

| Q Output                                  |                                     | 5.0<br>10<br>15        | -<br>-<br>-       | 530<br>225<br>155  | 1000<br>400<br>300 | ns   |

| Clock Pulse Width                         | t <sub>WH</sub>                     | 5.0<br>10<br>15        | 300<br>150<br>115 | 100<br>45<br>30    | -<br>-<br>-        | ns   |

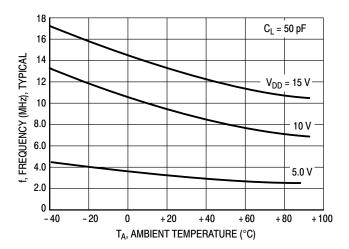

| Clock Pulse Frequency                     | f <sub>cl</sub>                     | 5.0<br>10<br>15        | -<br>-<br>-       | 3.5<br>9.5<br>13.0 | 2.1<br>5.1<br>7.8  | MHz  |

| Clock Pulse Rise and Fall Time            | t <sub>TLH</sub> , t <sub>THL</sub> | 5.0<br>10<br>15        |                   | NO LIMIT           |                    | μs   |

<sup>6.</sup> Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

## **SWITCHING WAVEFORMS**

Figure 2.

#### PIN DESCRIPTIONS

#### **INPUTS**

**P0, P1, P2, P3 (Pins 3, 4, 5, 6)** – Preset Inputs. Programmable inputs for the least significant counter. May be binary or BCD depending on the control input.

**P4, P5, P6, P7 (Pins 11, 12, 13, 14)** – Preset Inputs. Programmable inputs for the most significant counter. May be binary or BCD depending on the control input.

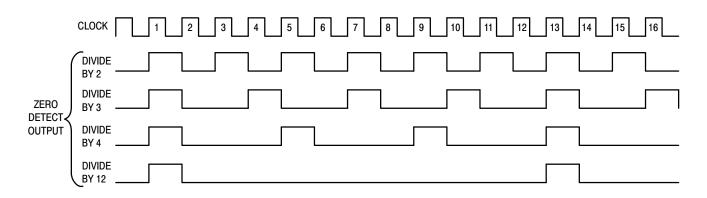

**Clock (Pin 9)** – Preset data is decremented by one on each positive transition of this signal.

#### **OUTPUTS**

**Zero Detect (Pin 1)** – This output is normally low and goes high for one clock cycle when the counter has decremented to zero.

**Q** (**Pin 15**) – Output of the last stage of the most significant counter. This output will be inactive unless the preset input P7 has been set high.

#### **CONTROLS**

Cascade Feedback (Pin 7) – This pin is normally set high. When low, loading of the preset inputs (P0 through P7) is inhibited, i.e., P0 through P7 are "don't cares." Refer to Table 1 for output characteristics.

$CTL_1$  (Pin 2) – This pin controls the counting mode of the least significant counter. When set high, counting mode is BCD. When set low, counting mode is binary.

CTL<sub>2</sub> (Pin 10) – This pin controls the counting mode of the most significant counter. When set high, counting mode is BCD. When set low, counting mode is binary.

#### **SUPPLY PINS**

$V_{SS}$  (Pin 18) – Negative Supply Voltage. This pin is usually connected to ground.

$V_{DD}$  (Pin 16) – Positive Supply Voltage. This pin is connected to a positive supply voltage ranging from 3.0 V to 18 V.

#### **OPERATING CHARACTERISTICS**

The MC14569B is a programmable divide-by-N dual 4-bit down counter. This counter may be programmed (i.e., preset) in BCD or binary code through inputs P0 to P7. For each counter, the counting sequence may be chosen independently by applying a high (for BCD count) or a low (for binary count) to the control inputs CTL<sub>1</sub> and CTL<sub>2</sub>.

The divide ratio N (N being the value programmed on the preset inputs P0 to P7) is automatically loaded into the counter as soon as the count 1 is detected. Therefore, a division ratio of one is not possible. After N clock cycles,

one pulse appears on the Zero Detect output. (See Timing Diagram.) The Q output is the output of the last stage of the most significant counter (See Tables 1 through 5, Mode Controls.)

When cascading the MC14569B to the MC14526B, the Cascade Feedback input, Q, and Zero Detect outputs must be respectively connected to "0", Clock, and Load of the following counter. If the MC14569B is used alone, Cascade Feedback must be connected to  $V_{DD}.\\$

Table 1. MODE CONTROLS (Cascade Feedback = Low)

| Counter C        | ontrol Values    | Divide Ratio |     |  |  |  |

|------------------|------------------|--------------|-----|--|--|--|

| CTL <sub>1</sub> | CTL <sub>2</sub> | Zero Detect  | Q   |  |  |  |

| 0                | 0                | 256          | 256 |  |  |  |

| 0                | 1                | 160          | 160 |  |  |  |

| 1                | 0                | 160          | 160 |  |  |  |

| 1                | 1                | 100          | 100 |  |  |  |

Data Preset Inputs (P0-P7) are "Don't Cares" while Cascade Feedback is Low.

Table 2. MODE CONTROLS ( $CTL_1 = Low, CTL_2 = Low, Cascade Feedback = High)$

|                |                |                | Preset         | Inputs         |                | Divide        | Ratio          |                |     |                      |

|----------------|----------------|----------------|----------------|----------------|----------------|---------------|----------------|----------------|-----|----------------------|

| P7             | P6             | P5             | P4             | Р3             | P2             | P1            | P0             | Zero<br>Detect | Q   | Comments             |

| 0              | 0              | 0              | 0              | 0              | 0              | 0             | 0              | 256            | 256 | Max Count            |

| 0              | 0              | 0              | 0              | 0              | 0              | 0             | 1              | X              | X   | Illegal State        |

| 0              | 0              | 0              | 0              | 0              | 0              | 1             | 0              | 2              | X   | Min Count            |

| 0              | 0              | 0              | 0              | 0              | 0              | 1             | 1              | 3              | Х   |                      |

| •              | •              | •              | •              | •              |                | •             |                | •              | Х   |                      |

| •              | •              | •              | •              | •              |                | •             |                | •              | Х   |                      |

| •              | •              | •              | •              | •              |                | •             |                | •              | Х   |                      |

| 0              | 0              | 0              | 0              | 1              | 1              | 1             | 1              | 15             | Х   |                      |

| 0              | 0              | 0              | 1              | 0              | 0              | 0             | 0              | 16             | Х   |                      |

| •              | •              | •              | •              | •              |                | •             |                | •              | Х   |                      |

| •              |                | •              | •              | •              |                |               | •              | •              | X   |                      |

| •              | •              | •              | •              | •              |                | •             |                | •              | X   |                      |

| 0              | 0              | 1              | 0              | 0              | 0              | 0             | 0              | 32             | X   |                      |

| •              |                | •              | •              | •              | •              | •             | •              | •              | X   |                      |

| •              |                | •              | •              | •              | •              | •             | •              | •              | X   |                      |

| •              |                | •              | •              | •              | •              | •             | •              | •              | X   |                      |

| 0              | 1              | 0              | 0              | 0              | 0              | 0             | 0              | 64             | X   |                      |

| •              |                | •              | •              | •              | •              | •             | •              | •              | X   |                      |

| •              |                | •              | •              | •              | •              | •             | •              | •              | X   |                      |

| •              |                | •              | •              | •              | •              | •             | •              | •              | X   |                      |

| 0              | 1              | 1              | 1              | 1              | 1              | 1             | 1              | 127            | X   |                      |

| 1              | 0              | 0              | 0              | 0              | 0              | 0             | 0              | 128            | 128 | Q Output Active      |

| •              | •              | •              | •              | •              | •              | •             | •              | •              | •   |                      |

| •              | •              | •              | •              | •              | •              | •             | •              | •              | •   |                      |

| •              | •              | •              | •              | •              | •              | •             | •              | •              | •   |                      |

| 1              | 0              | 0              | 0              | 1              | 0              | 0             | 0              | 136            | 136 |                      |

|                |                | •              | •              | •              |                |               | •              | •              |     |                      |

|                |                |                | •              | •              |                | •             |                | •              |     |                      |

|                |                | •              | •              | •              |                | •             |                | •              |     |                      |

| 1              | 1              | 1              | 1              | 1              | 1              | 1             | 1              | 255            | 255 | <b>_</b>             |

| 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 21            | 2 <sup>0</sup> |                |     |                      |

| 128            | 64             | 32             | 16             | 8              | 4              | 2             | 1              |                |     | Bit Value            |

|                | Coun<br>Bin    | ter #2<br>ary  |                |                | Coun<br>Bin    | ter #1<br>ary |                |                |     | Counting<br>Sequence |

X = No Output (Always Low)

$\textbf{Table 3. MODE CONTROLS (CTL}_1 = \textbf{High, CTL}_2 = \textbf{Low, Cascade Feedback} = \textbf{High)}$

|    |    |    | Preset |    |    |    | - r codbasi |                | Ratio |               |

|----|----|----|--------|----|----|----|-------------|----------------|-------|---------------|

| P7 | P6 | P5 | P4     | Р3 | P2 | P1 | P0          | Zero<br>Detect | Q     | Comments      |

| 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0           | 160            | 160   | Max Count     |

| 0  | 0  | 0  | 0      | 0  | 0  | 0  | 1           | Х              | X     | Illegal State |

| 0  | 0  | 0  | 0      | 0  | 0  | 1  | 0           | 2              | X     | Min Count     |

| 0  | 0  | 0  | 0      | 0  | 0  | 1  | 1           | 3              | X     |               |

| •  | •  | •  | •      | •  | •  | •  |             | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  |             | •              | Х     |               |

| •  | •  | •  | •      | •  | •  |    |             | •              | Х     |               |

| 0  | 0  | 0  | 0      | 1  | 0  | 0  | 1           | 9              | Х     |               |

| 0  | 0  | 0  | 1      | 0  | 0  | 0  | 0           | 10             | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| 0  | 0  | 0  | 1      | 1  | 0  | 0  | 1           | 19             | Х     |               |

| 0  | 0  | 1  | 0      | 0  | 0  | 0  | 0           | 20             | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| •  | •  | •  | •      | •  | •  |    |             | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  |             | •              | Х     |               |

| 0  | 0  | 1  | 1      | 0  | 0  | 0  | 0           | 30             | Х     |               |

| •  | •  | •  | •      | •  | •  | •  |             | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| 0  | 1  | 0  | 0      | 0  | 0  | 0  | 0           | 40             | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

| 0  | 1  | 0  | 1      | 0  | 0  | 0  | 0           | 50             | Х     |               |

| •  |    |    |        |    |    |    |             |                | Х     |               |

| •  |    |    |        | •  |    |    |             | •              | Х     |               |

| •  |    |    |        | •  |    |    |             | •              | Х     |               |

| 0  | 1  | 1  | 0      | 0  | 0  | 0  | 0           | 60             | Х     |               |

| •  |    |    | •      | •  |    | •  |             | •              | Х     |               |

| •  | •  |    |        |    |    |    |             |                | Х     |               |

| •  |    |    |        | •  |    |    |             | •              | Х     |               |

| 0  | 1  | 1  | 1      | 0  | 0  | 0  | 0           | 70             | Х     |               |

| •  |    |    | •      | •  |    | •  |             | •              | Х     |               |

| •  |    |    |        | •  |    |    |             | •              | Х     |               |

| •  | •  | •  | •      | •  | •  | •  | •           | •              | Х     |               |

$\textbf{Table 3. MODE CONTROLS} \ (\text{CTL}_1 = \text{High, CTL}_2 = \text{Low, Cascade Feedback} = \text{High)}$

|    |             |               | Preset | Inputs |            |              |    | Divide         | Ratio |                      |

|----|-------------|---------------|--------|--------|------------|--------------|----|----------------|-------|----------------------|

| P7 | P6          | P5            | P4     | Р3     | P2         | P1           | P0 | Zero<br>Detect | Q     | Comments             |

| 1  | 0           | 0             | 0      | 0      | 0          | 0            | 0  | 80             | 80    | Q Output Active      |

|    | •           |               | •      | •      | •          | •            |    | •              | •     |                      |

|    | •           | •             | •      | •      | •          | •            |    | •              | •     |                      |

|    | •           | •             | •      | •      | •          | •            |    | •              | •     |                      |

| 1  | 0           | 0             | 1      | 0      | 0          | 0            | 0  | 90             | 90    |                      |

|    | •           | •             | •      | •      | •          | •            |    | •              | •     |                      |

|    | •           | •             | •      | •      | •          | •            |    | •              | •     |                      |

|    | •           | •             | •      | •      | •          | •            |    | •              | •     |                      |

| 1  | 1           | 1             | 1      | 0      | 0          | 0            | 0  | 150            | 150   |                      |

| •  | •           | •             | •      | •      | •          | •            |    | •              | •     |                      |

| •  | •           |               | •      | •      | •          | •            |    | •              | •     |                      |

|    | •           | •             | •      | •      | •          | •            |    | •              | •     |                      |

| 1  | 1           | 1             | 1      | 1      | 0          | 0            | 1  | 159            | 159   |                      |

| 80 | 40          | 20            | 10     | 8      | 4          | 2            | 1  |                |       | Bit Value            |

|    | Coun<br>Bin | ter #2<br>ary |        |        | Coun<br>BC | ter #1<br>CD |    |                |       | Counting<br>Sequence |

X = No Output (Always Low)

Table 4. MODE CONTROLS ( $CTL_1 = Low, CTL_2 = High, Cascade Feedback = High)$

|    |    |    | Preset | Values |    |    |    | Divide         | Ratio |               |

|----|----|----|--------|--------|----|----|----|----------------|-------|---------------|

| P7 | P6 | P5 | P4     | Р3     | P2 | P1 | P0 | Zero<br>Detect | Q     | Comments      |

| 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 160            | 160   | Max Count     |

| 0  | 0  | 0  | 0      | 0      | 0  | 0  | 1  | X              | Х     | Illegal State |

| 0  | 0  | 0  | 0      | 0      | 0  | 1  | 0  | 2              | Х     | Min Count     |

| 0  | 0  | 0  | 0      | 0      | 0  | 1  | 1  | 3              | Х     |               |

| •  | •  |    | •      | •      |    | •  | •  |                | Х     |               |

| •  | •  |    | •      | •      |    | •  | •  |                | Х     |               |

| •  | •  |    | •      | •      |    | •  |    |                | Х     |               |

| 0  | 0  | 0  | 0      | 1      | 1  | 1  | 1  | 15             | X     |               |

| 0  | 0  | 0  | 1      | 0      | 0  | 0  | 0  | 16             | X     |               |

| •  | •  | •  | •      | •      | •  | •  | •  |                | X     |               |

| •  | •  | •  | •      | •      | •  | •  | •  | •              | X     |               |

| •  | •  | •  | •      | •      | •  | •  | •  | •              | X     |               |

| 0  | 0  | 0  | 1      | 1      | 1  | 1  | 1  | 31             | X     |               |

| 0  | 0  | 1  | 0      | 0      | 0  | 0  | 0  | 32             | X     |               |

| •  |    | •  | •      | •      | •  | •  | •  |                | X     |               |

| •  |    | •  | •      | •      | •  | •  | •  |                | X     |               |

| •  |    | •  | •      | •      | •  | •  | •  |                | X     |               |

| 0  | 0  | 1  | 1      | 0      | 0  | 0  | 0  | 48             | X     |               |

| •  |    | •  | •      | •      | •  | •  | •  |                | •     |               |

| •  | •  |    | •      | •      | •  | •  | •  |                | •     |               |

| •  | •  |    | •      | •      | •  | •  | •  |                | •     |               |

| 0  | 1  | 0  | 0      | 0      | 0  | 0  | 0  | 64             | X     |               |

| •  | •  |    | •      | •      | •  | •  | •  |                | •     |               |

| •  | •  |    | •      | •      | •  | •  | •  |                | •     |               |

| •  | •  | •  | •      | •      | •  | •  | •  | •              | •     |               |

| 0  | 1  | 0  | 1      | 0      | 0  | 0  | 0  | 80             | X     |               |

| •  |    | •  | •      | •      |    | •  | •  |                | •     |               |

| •  |    | •  | •      | •      |    | •  | •  |                | •     |               |

| •  |    | •  | •      | •      |    | •  | •  |                | •     |               |

| 0  | 1  | 1  | 1      | 0      | 0  | 0  | 0  | 112            | X     |               |

| •  | •  |    | •      | •      | •  | •  | •  |                | •     |               |

| •  |    |    | •      | •      |    | •  | •  |                | •     |               |

| •  | •  | •  | •      | •      | •  | •  | •  | •              | •     |               |

$\textbf{Table 4. MODE CONTROLS} \ (\text{CTL}_1 = \text{Low}, \ \text{CTL}_2 = \text{High}, \ \text{Cascade Feedback} = \text{High})$

|                                  |                |                | Preset         | Values         |                |    |                | Divide         | Ratio                |                 |

|----------------------------------|----------------|----------------|----------------|----------------|----------------|----|----------------|----------------|----------------------|-----------------|

| P7                               | P6             | P5             | P4             | Р3             | P2             | P1 | P0             | Zero<br>Detect | Q                    | Comments        |

| 1                                | 0              | 0              | 0              | 0              | 0              | 0  | 0              | 128            | 128                  | Q Output Active |

| •                                | •              |                | •              | •              | •              | •  | •              | •              | •                    |                 |

| •                                | •              |                | •              |                | •              | •  | •              | •              | •                    |                 |

| •                                | •              |                | •              |                | •              | •  | •              | •              | •                    |                 |

| 1                                | 0              | 0              | 1              | 0              | 0              | 0  | 0              | 144            | 144                  |                 |

| •                                | •              | •              | •              | •              | •              | •  | •              |                | •                    |                 |

| •                                | •              |                | •              |                | •              | •  | •              | •              | •                    |                 |

| •                                | •              | •              | •              | •              | •              | •  | •              | •              | •                    |                 |

| 1                                | 0              | 0              | 1              | 1              | 1              | 1  | 1              | 159            | 159                  | ↓ ↓             |

| 2 <sup>7</sup>                   | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | 2 <sup>0</sup> |                |                      |                 |

| 128                              | 64             | 32             | 16             | 8              | 4              | 2  | 1              |                |                      | Bit Value       |

| Counter #2 Counter #1 BCD Binary |                |                |                |                |                |    |                |                | Counting<br>Sequence |                 |

X = No Output (Always Low)

$\textbf{Table 5. MODE CONTROLS} \; (\text{CTL}_1 = \text{High, CTL}_2 = \text{High, Cascade Feedback} = \text{High}) \\$

|    |    |    | Preset | Values |    |    |    | Divide         | Ratio |                 |

|----|----|----|--------|--------|----|----|----|----------------|-------|-----------------|

| P7 | P6 | P5 | P4     | Р3     | P2 | P1 | P0 | Zero<br>Detect | Q     | Comments        |

| 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 100            | 100   | Max Count       |

| 0  | 0  | 0  | 0      | 0      | 0  | 0  | 1  | X              | Х     | illegal state   |

| 0  | 0  | 0  | 0      | 0      | 0  | 1  | 0  | 2              | Х     | Min Count       |

| 0  | 0  | 0  | 0      | 0      | 0  | 1  | 1  | 3              | Х     |                 |

|    |    |    |        | •      |    |    |    |                | Х     |                 |

|    |    |    |        | •      |    |    |    |                | Х     |                 |

|    |    |    |        |        |    |    |    | •              | Х     |                 |

| 0  | 0  | 0  | 0      | 1      | 0  | 0  | 1  | 9              | Х     |                 |

| 0  | 0  | 0  | 1      | 0      | 0  | 0  | 0  | 10             | Х     |                 |

| •  | •  |    |        | •      | •  | •  |    | •              | Х     |                 |

| •  | •  |    |        | •      | •  | •  |    | •              | Х     |                 |

| •  | •  |    |        | •      | •  | •  |    | •              | Х     |                 |

| 0  | 0  | 1  | 1      | 0      | 0  | 0  | 0  | 30             | Х     |                 |

| •  | •  |    |        | •      | •  | •  |    | •              | Х     |                 |

| •  | •  |    |        | •      | •  | •  |    | •              | X     |                 |

| •  | •  |    |        | •      | •  | •  |    | •              | Х     |                 |

| 0  | 1  | 0  | 0      | 0      | 0  | 0  | 0  | 40             | X     |                 |

| •  | •  |    |        | •      | •  | •  | •  | •              | X     |                 |

| •  | •  |    |        | •      | •  | •  |    | •              | X     |                 |

| •  |    | •  |        | •      | •  | •  | •  | •              | X     |                 |

| 0  | 1  | 0  | 1      | 0      | 0  | 0  | 0  | 50             | Х     |                 |

| •  |    | •  | •      | •      | •  | •  | •  | •              | X     |                 |

| •  |    | •  | •      | •      | •  | •  | •  | •              | X     |                 |

| •  |    | •  | •      | •      | •  | •  | •  | •              | X     |                 |

| 0  | 1  | 1  | 1      | 0      | 0  | 0  | 0  | 70             | X     |                 |

| •  |    | •  | •      | •      | •  | •  | •  | •              | X     |                 |

| •  |    | •  | •      | •      | •  | •  | •  | •              | X     |                 |

| •  |    | •  | •      | •      | •  | •  | •  | •              | X     |                 |

| 1  | 0  | 0  | 0      | 0      | 0  | 0  | 0  | 80             | 80    | Q Output Active |

|    |    |    |        |        | •  |    |    | •              |       |                 |

|    |    |    |        |        | •  | •  |    | •              |       |                 |

|    |    |    |        |        | •  | •  |    | •              | •     |                 |

| 1  | 0  | 0  | 1      | 0      | 0  | 0  | 0  | 90             | 90    |                 |

|    |    |    |        |        | •  |    |    | •              |       |                 |

|    |    |    |        |        | •  | •  |    | •              |       |                 |

|    |    |    |        |        | •  | •  |    | •              |       |                 |

| 1  | 0  | 0  | 1      | 1      | 0  | 0  | 1  | 99             | 99    | . ↓             |

Table 5. MODE CONTROLS ( $CTL_1$  = High,  $CTL_2$  = High, Cascade Feedback = High)

| Preset Values |                   |    |    |                   |    |    |    | Divide Ratio   |   |                      |

|---------------|-------------------|----|----|-------------------|----|----|----|----------------|---|----------------------|

| P7            | P6                | P5 | P4 | Р3                | P2 | P1 | P0 | Zero<br>Detect | Q | Comments             |

| 80            | 40                | 20 | 10 | 8                 | 4  | 2  | 1  |                |   | Bit Value            |

|               | Counter #2<br>BCD |    |    | Counter #1<br>BCD |    |    |    |                |   | Counting<br>Sequence |

X = No Output (Always Low)

#### **TIMING DIAGRAM MC14569B**

### **TYPICAL APPLICATIONS**

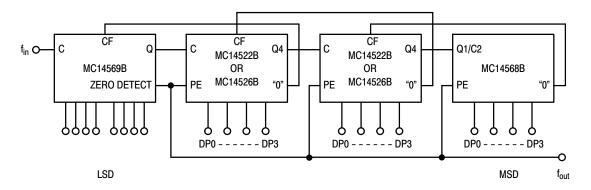

Figure 3. Cascading MC14568B and MC14522B or MC14526B with MC14569B

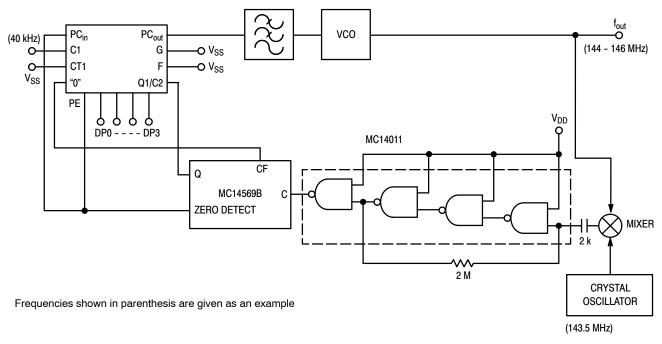

Figure 4. Frequency Synthesizer with MC14568B and MC14569B Using a Mixer (Channel Spacing 10 kHz)

# **REVISION HISTORY**

| Revision | Description of Changes                                                                                    | Date       |

|----------|-----------------------------------------------------------------------------------------------------------|------------|

| 9        | Rebranded the Data Sheet to <b>onsemi</b> format. MC14569BDWG, MC14569BDWR2G OPNs Marked as Discontinued. | 07/25/2025 |

This document has undergone updates prior to the inclusion of this revision history table. The changes tracked here only reflect updates made on the noted approval dates.

SCALE 1:1

SOIC-16 WB CASE 751G ISSUE E

**DATE 08 OCT 2021**

# **♦** 0.25**₩** B**₩** RRRR PIN 1 --INDICATOR -16X R **♦** 0.25**@**|T|AS|BS|

TOP VIEW

DETAIL A

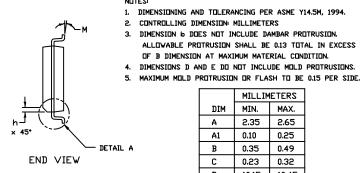

MILLIMETERS DIM MIN. MAX. 2.35 2.65 A1 0.10 0.25 В 0.35 0.49 0.23 0.32 D 10.15 10.45 7.60 7.40 Ε 1.27 BSC e Н 10.05 10.55 h 0.53 REF 0.50 0.90

ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

MOUNTING FOOTPRINT

### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42567B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SOIC-16 WB  |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales