## onsemi

## 2-Bit 20 Mb/s Dual-Supply Level Translator NLSX0102

The NLSX0102 is a 2-bit configurable dual-supply bidirectional auto sensing translator that does not require a directional control pin. The I/O V<sub>CC</sub> and I/O V<sub>L</sub> ports are designed to track two different power supply rails, V<sub>CC</sub> and V<sub>L</sub> respectively. Both the V<sub>CC</sub> and V<sub>L</sub> supply rails are configurable from 1.65 V to 5.5 V. This allows voltage logic signals on the V<sub>L</sub> side to be translated into voltage logic signals on the V<sub>CC</sub> side, and vice-versa.

The NLSX0102 translator has integrated 10 k $\Omega$  pull-up resistors on the I/O lines. The integrated pull-up resistors are used to pull-up the I/O lines to either V<sub>L</sub> or V<sub>CC</sub>. The NLSX0102 is an excellent match for open-drain applications such as the I<sup>2</sup>C communication bus.

#### Features

- Wide V<sub>CC</sub> Operating Range: V<sub>L</sub> to 5.5 V Wide V<sub>L</sub> Operating Range: 1.65 V to 5.5 V

- High-Speed with 24 Mb/s Guaranteed Date Rate

- Low Bit-to-Bit Skew

- Enable Input and I/O Pins are Overvoltage Tolerant (OVT) to 5.5 V

- Non-preferential Power-up Sequencing

- Integrated 10 k $\Omega$  Pull-up Resistors

- Small Space Saving Package

1.9 mm x 0.9 mm x 0.5 mm Flipchip8

- This is a Pb–Free Device

#### **Typical Applications**

- I<sup>2</sup>C, SMBus

- Low Voltage ASIC Level Translation

- Mobile Phones, PDAs, Cameras

#### Important Information

- ESD Protection for All Pins

- Human Body Model (HBM) > 7000 V

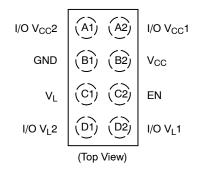

#### **PIN ASSIGNMENTS**

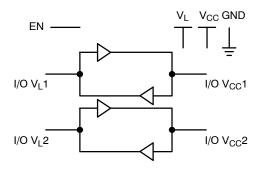

#### LOGIC DIAGRAM

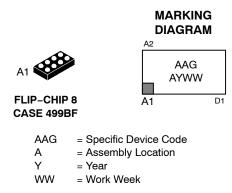

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

#### **PIN ASSIGNMENT**

| Pins                  | Description                        |  |  |  |  |

|-----------------------|------------------------------------|--|--|--|--|

| V <sub>CC</sub>       | V <sub>CC</sub> Supply Voltage     |  |  |  |  |

| VL                    | V <sub>L</sub> Supply Voltage      |  |  |  |  |

| GND                   | Ground                             |  |  |  |  |

| EN                    | Output Enable, referenced to $V_L$ |  |  |  |  |

| I/O V <sub>CC</sub> n | I/O Port, referenced to $V_{CC}$   |  |  |  |  |

| I/O V <sub>L</sub> n  | I/O Port, referenced to $V_L$      |  |  |  |  |

#### **FUNCTION TABLE**

| EN | Operating Mode      |

|----|---------------------|

| L  | Hi–Z                |

| Н  | I/O Buses Connected |

#### MAXIMUM RATINGS

| Symbol              | Parameter                                                    | Value        | Condition            | Unit |

|---------------------|--------------------------------------------------------------|--------------|----------------------|------|

| V <sub>CC</sub>     | High-side DC Supply Voltage                                  | -0.5 to +7.0 |                      | V    |

| VL                  | Low-side DC Supply Voltage                                   | -0.5 to +7.0 |                      | V    |

| I/O V <sub>CC</sub> | V <sub>CC</sub> -referenced DC Input / Output Voltage        | -0.5 to +7.0 |                      | V    |

| I/O VL              | V <sub>L</sub> -referenced DC Input / Output Voltage         | -0.5 to +7.0 |                      | V    |

| $V_{EN}$            | Enable Control Pin DC Input Voltage                          | -0.5 to +7.0 |                      | V    |

| I <sub>I/O_SC</sub> | Short–Circuit Duration (I/O $V_L$ and I/O $V_{CC}$ to GND)   | ±50          | Continuous           | mA   |

| I <sub>I/OK</sub>   | Input / Output Clamping Current (I/O $V_L$ and I/O $V_{CC})$ | -50          | V <sub>I/O</sub> < 0 | mA   |

| T <sub>STG</sub>    | Storage Temperature                                          | -65 to +150  |                      | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol              | Parameter                                                                               | Min  | Мах | Unit |

|---------------------|-----------------------------------------------------------------------------------------|------|-----|------|

| V <sub>CC</sub>     | High-side Positive DC Supply Voltage                                                    | VL   | 5.5 | V    |

| VL                  | Low-side Positive DC Supply Voltage                                                     | 1.65 | 5.5 | V    |

| V <sub>EN</sub>     | Enable Control Pin Voltage                                                              | GND  | 5.5 | V    |

| V <sub>IO</sub>     | I/O Pin Voltage                                                                         | GND  | 5.5 | V    |

| $\Delta t/\Delta V$ | Input Transition Rise and Fall Rate I/O $V_L$ and I/O $V_{CC}$ Ports, Push–Pull Driving |      | 10  | ns/V |

|                     | Control Input                                                                           |      | 10  |      |

| T <sub>A</sub>      | Operating Temperature Range                                                             | -40  | +85 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

|                     |                                                         |                                                                                     |                |                          | -                        |                            |                          |      |

|---------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------|----------------|--------------------------|--------------------------|----------------------------|--------------------------|------|

| Symbol              | Parameter                                               | Test Conditions<br>(Note 1)                                                         | VL             | v <sub>cc</sub>          | Min                      | <b>Typ</b><br>(Notes 1, 2) | Max                      | Unit |

| V <sub>IHC</sub>    | I/O V <sub>CC</sub> Input HIGH Voltage                  |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 | V <sub>CC</sub> –<br>0.4 |                            | -                        | V    |

| V <sub>ILC</sub>    | I/O V <sub>CC</sub> Input LOW Voltage                   |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 0.15                     | V    |

| V <sub>IHL</sub>    | I/O V <sub>L</sub> Input HIGH Voltage                   |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 | $V_L - 0.4$              |                            | -                        | V    |

| V <sub>ILL</sub>    | I/O V <sub>L</sub> Input LOW Voltage                    |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 0.15                     | V    |

| V <sub>IH</sub>     | Control Pin Input HIGH Voltage                          |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 | 0.75 *<br>V <sub>L</sub> |                            | -                        | V    |

| V <sub>IL</sub>     | Control Pin Input LOW Voltage                           |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 0.25 *<br>V <sub>L</sub> | V    |

| V <sub>OHC</sub>    | I/O V <sub>CC</sub> Output HIGH Voltage                 | I/O V <sub>CC</sub> source<br>current = –20 μA                                      | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 | 2/3 *<br>V <sub>CC</sub> |                            | -                        | V    |

| V <sub>OLC</sub>    | I/O V <sub>CC</sub> Output LOW Voltage                  | I/O V <sub>CC</sub> sink current =<br>1 mA                                          | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 0.4                      | V    |

| V <sub>OHL</sub>    | I/O V <sub>L</sub> Output HIGH Voltage                  | $I/O V_L$ source current<br>= -20 $\mu A$                                           | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 | 2/3 * V <sub>L</sub>     |                            | -                        | V    |

| V <sub>OLL</sub>    | I/O V <sub>L</sub> Output LOW Voltage                   | I/O V <sub>L</sub> sink current =<br>1 mA                                           | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 0.4                      | V    |

| I <sub>QVL</sub>    | V <sub>L</sub> Supply Current<br>Supply Current         | I/O V <sub>CC</sub> and I/O V <sub>L</sub> unconnected, V <sub>EN</sub> =           | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 2.4                      | μA   |

|                     |                                                         | VL                                                                                  | 5.5            | 0                        |                          |                            | 2.4                      |      |

| IQVCC               | V <sub>L</sub> Supply Current<br>Supply Current         | I/O V <sub>CC</sub> and I/O V <sub>L</sub><br>unconnected,                          | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 2.4                      | μA   |

|                     |                                                         | $V_{EN} = V_{L}$                                                                    | 0              | 5.5                      |                          |                            | 2.4                      |      |

| I <sub>TS-VCC</sub> | V <sub>CC</sub> Tri-state Output Mode                   | I/O V <sub>CC</sub> and I/O V <sub>L</sub><br>unconnected,<br>V <sub>EN</sub> = GND | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 1.0                      | μΑ   |

| I <sub>TS-VL</sub>  | V <sub>L</sub> Tri-state Output Mode Supply<br>Current  | I/O V <sub>CC</sub> and I/O V <sub>L</sub> unconnected, $V_{EN} = GND$              | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 1.0                      | μΑ   |

| lj –                | Enable Pin Input Leakage Current                        |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 1.0                      | μA   |

| I <sub>OZ</sub>     | I/O Tri-state Output Mode Leakage<br>Current            |                                                                                     | 1.65 to<br>5.5 | V <sub>L</sub> to<br>5.5 |                          |                            | 1.0                      | μA   |

| R <sub>PU</sub>     | Pull–Up Resistors I/O V <sub>L</sub> and V <sub>C</sub> |                                                                                     |                |                          |                          | 10                         |                          | kΩ   |

#### DC ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = -40 to +85 $^{\circ}$ C, unless otherwise specified)

1. Typical values are for  $V_{CC} = +3.3 \text{ V}$ ,  $V_L = +1.8 \text{ V}$  and  $T_A = +25^{\circ}\text{C}$ . 2. All units are production tested at  $T_A = +25^{\circ}\text{C}$ . Limits over the operating temperature range are guaranteed by design. Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

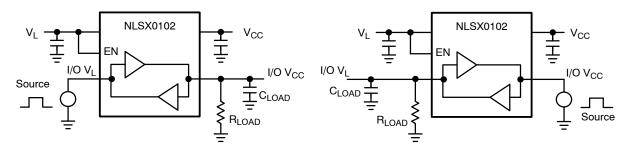

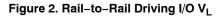

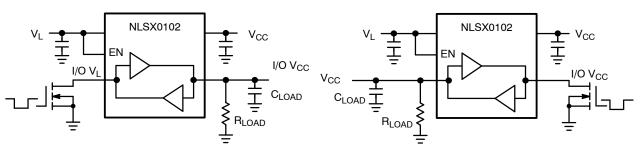

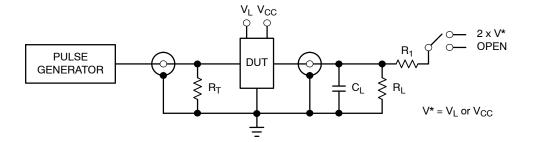

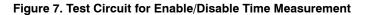

$\label{eq:characteristics} \begin{array}{l} \textbf{Timing Characteristics} - \textbf{Rail-to-Rail Driving Configuration} \\ (I/O \ test \ circuits \ of \ Figures \ 2, \ 3 \ and \ 7, \ C_{LOAD} = 15 \ pF, \ driver \ output \ impedance \ \leq 50 \ \Omega, \ R_{LOAD} = 1 \ M\Omega, \ unless \ otherwise \ specified) \\ \end{array}$

|                             |                                                             |            | -40°C to +85°C       |            |                       |                                |     |            |      |

|-----------------------------|-------------------------------------------------------------|------------|----------------------|------------|-----------------------|--------------------------------|-----|------------|------|

|                             |                                                             |            | V <sub>CC</sub> = 2. | 3 to 2.7 V | V <sub>CC</sub> = 3.0 | V <sub>CC</sub> = 3.0 to 3.6 V |     | 5 to 5.5 V |      |

| Symbol                      | Parameter                                                   | Conditions | Min                  | Мах        | Min                   | Max                            | Min | Max        | Unit |

| V <sub>L</sub> = 1.65 to 1  | .95 V                                                       | •          |                      |            |                       |                                |     |            |      |

| t <sub>RVL</sub>            | I/O V <sub>L</sub> Rise Time                                | Figure 8   | 0.6                  | 17.0       | 2.3                   | 14.0                           | 0.8 | 12.9       | nS   |

| t <sub>RVCC</sub>           | I/O V <sub>CC</sub> Rise Time                               | Figure 8   | 4.0                  | 10.8       | 2.2                   | 9.1                            | 2.7 | 7.6        | nS   |

| t <sub>FVL</sub>            | I/O V <sub>L</sub> Fall Time                                | Figure 8   | 2.0                  | 9.7        | 1.9                   | 8.1                            | 1.7 | 13.3       | nS   |

| t <sub>FVCC</sub>           | I/O V <sub>CC</sub> Fall Time                               | Figure 8   | 2.9                  | 13.8       | 2.8                   | 16.2                           | 2.8 | 16.2       | nS   |

| t <sub>PHL-VL-VCC</sub>     | Propagation Delay                                           | Figure 2   |                      | 7.2        |                       | 7.1                            |     | 10.0       | nS   |

| t <sub>PLH-VL-VCC</sub>     | (Driving I/O $V_L$ , $V_L$ to $V_{CC}$ )                    |            |                      | 6.5        |                       | 7.1                            |     | 7.4        |      |

| t <sub>PHL-VCC-VL</sub>     | Propagation Delay                                           | Figure 3   |                      | 6.0        |                       | 5.3                            |     | 6.7        | nS   |

| t <sub>PLH-VCC-VL</sub>     | (Driving I/O $V_{CC}$ , $V_{CC}$ to $V_L$ )                 |            |                      | 8.0        |                       | 7.6                            |     | 7.1        |      |

| t <sub>EN</sub>             | Enable Time                                                 | Figure 7   | 1                    | 50         |                       | 40                             |     | 35         | nS   |

| t <sub>DIS</sub>            | Disable Time                                                | Figure 7   |                      | 390        |                       | 365                            |     | 710        | nS   |

| tPPSKEW                     | Part-to-Part Skew                                           |            |                      | 0.7        |                       | 0.7                            |     | 0.7        | nS   |

| MDR                         | Maximum Data Rate                                           |            | 21                   |            | 22                    |                                | 24  |            | Mbps |

| V <sub>L</sub> = 2.3 to 2.7 | 7 V                                                         | •          |                      |            |                       |                                |     |            |      |

| t <sub>RVL</sub>            | I/O V <sub>L</sub> Rise Time                                | Figure 8   | 2.8                  | 8.6        | 2.6                   | 8.1                            | 1.8 | 10.3       | nS   |

| t <sub>RVCC</sub>           | I/O V <sub>CC</sub> Rise Time                               | Figure 8   | 3.2                  | 9.2        | 2.9                   | 8.8                            | 1.9 | 7.7        | nS   |

| t <sub>FVL</sub>            | I/O V <sub>L</sub> Fall Time                                | Figure 8   | 1.9                  | 8.3        | 1.9                   | 7.8                            | 1.8 | 7.4        | nS   |

| t <sub>FVCC</sub>           | I/O V <sub>CC</sub> Fall Time                               | Figure 8   | 2.2                  | 8.3        | 2.4                   | 8.0                            | 2.6 | 10.0       | nS   |

| t <sub>PHL-VL-VCC</sub>     | Propagation Delay                                           | Figure 2   |                      | 4.8        |                       | 5.2                            |     | 6.5        | nS   |

| t <sub>PLH-VL-VCC</sub>     | (Driving I/O $V_L$ , $V_L$ to $V_{CC}$ )                    |            |                      | 5.4        |                       | 5.3                            |     | 6.0        |      |

| t <sub>PHL-VCC-VL</sub>     | Propagation Delay                                           | Figure 3   |                      | 5.0        |                       | 3.9                            |     | 5.4        | nS   |

| t <sub>PLH-VCC-VL</sub>     | (Driving I/O V <sub>CC</sub> , $V_{CC}$ to V <sub>L</sub> ) |            |                      | 5.5        |                       | 5.0                            |     | 5.5        |      |

| t <sub>EN</sub>             | Enable Time                                                 | Figure 7   |                      | 100        |                       | 40                             |     | 35         | nS   |

| t <sub>DIS</sub>            | Disable Time                                                | Figure 7   |                      | 320        |                       | 305                            |     | 430        | nS   |

| <b>t</b> PPSKEW             | Part-to-Part Skew                                           |            | 1                    | 0.7        |                       | 0.7                            |     | 0.7        | nS   |

| MDR                         | Maximum Data Rate                                           |            | 20                   |            | 22                    | İ                              | 24  |            | Mbps |

#### Timing Characteristics – Rail-to-Rail Driving Configuration

(I/O test circuits of Figures 2, 3 and 7,  $C_{LOAD}$  = 15 pF, driver output impedance  $\leq$  50  $\Omega$ ,  $R_{LOAD}$  = 1 M $\Omega$ , unless otherwise specified)

|                             |                                             |                                                                                                | –40°C to +85°C                 |     |                                |     |                                |      |      |

|-----------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------|-----|--------------------------------|-----|--------------------------------|------|------|

|                             |                                             |                                                                                                | V <sub>CC</sub> = 2.3 to 2.7 V |     | V <sub>CC</sub> = 3.0 to 3.6 V |     | V <sub>CC</sub> = 4.5 to 5.5 V |      | 1    |

| Symbol                      | Parameter                                   | Conditions                                                                                     | Min                            | Max | Min                            | Max | Min                            | Max  | Unit |

| V <sub>L</sub> = 3.0 to 3.6 | 5 V                                         |                                                                                                |                                |     |                                |     | -                              |      |      |

| t <sub>RVL</sub>            | I/O V <sub>L</sub> Rise Time                | Figure 8                                                                                       |                                |     | 2.3                            | 6.5 | 1.9                            | 8.0  | nS   |

| t <sub>RVCC</sub>           | I/O V <sub>CC</sub> Rise Time               | Figure 8                                                                                       |                                |     | 2.5                            | 6.5 | 2.1                            | 7.4  | nS   |

| t <sub>FVL</sub>            | I/O V <sub>L</sub> Fall Time                | Figure 8                                                                                       |                                |     | 1.3                            | 7.2 | 1.6                            | 11.0 | nS   |

| t <sub>FVCC</sub>           | I/O V <sub>CC</sub> Fall Time               | Figure 8                                                                                       |                                |     | 1.7                            | 8.0 | 1.3                            | 9.3  | nS   |

| t <sub>PHL-VL-VCC</sub>     | Propagation Delay                           | Propagation Delay Figure 2<br>Driving I/O V <sub>L</sub> , V <sub>L</sub> to V <sub>CC</sub> ) |                                |     |                                | 3.9 |                                | 4.6  | nS   |

| t <sub>PLH-VL-VCC</sub>     | (Driving I/O $v_L$ , $v_L$ to $v_{CC}$ )    |                                                                                                |                                |     |                                | 3.8 |                                | 3.8  |      |

| t <sub>PHL-VCC-VL</sub>     | Propagation Delay                           | Figure 3                                                                                       |                                |     |                                | 3.8 |                                | 4.6  | nS   |

| t <sub>PLH-VCC-VL</sub>     | (Driving I/O $V_{CC}$ , $V_{CC}$ to $V_L$ ) |                                                                                                |                                |     |                                | 4.3 |                                | 5.8  |      |

| t <sub>EN</sub>             | Enable Time                                 | Figure 7                                                                                       |                                |     |                                | 80  |                                | 35   | nS   |

| t <sub>DIS</sub>            | Disable Time                                | Figure 7                                                                                       |                                |     |                                | 260 |                                | 385  | nS   |

| <b>t</b> PPSKEW             | Part-to-Part Skew                           |                                                                                                |                                |     |                                | 0.7 |                                | 0.7  | nS   |

| MDR                         | Maximum Data Rate                           |                                                                                                |                                |     | 23                             |     | 24                             |      | Mbps |

$\label{eq:constraint} \begin{array}{l} \textbf{Timing Characteristics} - \textbf{Open Drain Driving Configuration} \\ (I/O \ test \ circuits \ of \ Figures \ 4, \ 5 \ and \ 7, \ C_{LOAD} \ = \ 15 \ pF, \ driver \ output \ impedance \ \leq \ 50 \ \Omega, \ R_{LOAD} \ = \ 1 \ M\Omega, \ unless \ otherwise \ specified) \\ \end{array}$

|                            |                                             |            | -40°C to +85°C        |            |                       |            |                       |            |      |

|----------------------------|---------------------------------------------|------------|-----------------------|------------|-----------------------|------------|-----------------------|------------|------|

|                            |                                             |            | V <sub>CC</sub> = 2.3 | 3 to 2.7 V | V <sub>CC</sub> = 3.0 | 0 to 3.6 V | V <sub>CC</sub> = 4.5 | 5 to 5.5 V |      |

| Symbol                     | Parameter                                   | Conditions | Min                   | Max        | Min                   | Max        | Min                   | Max        | Unit |

| V <sub>L</sub> = 1.65 to 1 | .95 V                                       |            |                       |            |                       |            |                       |            |      |

| t <sub>RVL</sub>           | I/O V <sub>L</sub> Rise Time                | Figure 8   | 38                    | 340        | 30                    | 245        | 22.0                  | 134        | nS   |

| t <sub>RVCC</sub>          | I/O V <sub>CC</sub> Rise Time               | Figure 8   | 34                    | 330        | 23                    | 218        | 10.0                  | 120        | nS   |

| t <sub>FVL</sub>           | I/O V <sub>L</sub> Fall Time                | Figure 8   | 4.4                   | 11.1       | 4.3                   | 12.0       | 4.2                   | 14.2       | nS   |

| t <sub>FVCC</sub>          | I/O V <sub>CC</sub> Fall Time               | Figure 8   | 6.9                   | 11         | 7.5                   | 16.2       | 7.0                   | 16.2       | nS   |

| t <sub>PHLVL-VCC</sub>     | Propagation Delay                           | Figure 2   | 2.3                   | 27         | 2.4                   | 20.0       | 2.6                   | 23.0       | nS   |

| t <sub>PLHVL-VCC</sub>     | (Driving I/O $V_L$ , $V_L$ to $V_{CC}$ )    |            | 45                    | 260        | 36.0                  | 208        | 27.0                  | 208        |      |

| t <sub>PHLVCC-VL</sub>     | Propagation Delay                           | Figure 3   | 1.9                   | 22         | 1.1                   | 22.0       | 1.2                   | 22.0       | nS   |

| t <sub>PLHVCC-VL</sub>     | (Driving I/O $V_{CC}$ , $V_{CC}$ to $V_L$ ) |            | 45.0                  | 200        | 36                    | 150        | 27.0                  | 112        |      |

| t <sub>EN</sub>            | Enable Time                                 | Figure 7   |                       | 80         |                       | 70         |                       | 35         | nS   |

| t <sub>DIS</sub>           | Disable Time                                | Figure 7   |                       | 250        |                       | 277        |                       | 290        | nS   |

| t <sub>PPSKEW</sub>        | Part-to-Part Skew                           |            |                       | 0.7        |                       | 0.7        |                       | 0.7        | nS   |

| MDR                        | Maximum Data Rate                           |            | 2                     |            | 2                     |            | 2                     |            | Mbps |

$\label{eq:constraint} \begin{array}{l} \textbf{Timing Characteristics - Open Drain Driving Configuration} \\ (I/O test circuits of Figures 4, 5 and 7, C_{LOAD} = 15 \text{ pF}, driver output impedance} \leq 50 \ \Omega, \ R_{LOAD} = 1 \ M\Omega, unless otherwise specified) \end{array}$

|                             |                                                                   |              | –40°C to +85°C                                      |      |      |            |                                |      |      |

|-----------------------------|-------------------------------------------------------------------|--------------|-----------------------------------------------------|------|------|------------|--------------------------------|------|------|

|                             |                                                                   |              | V <sub>CC</sub> = 2.3 to 2.7 V V <sub>CC</sub> = 3. |      |      | 0 to 3.6 V | V <sub>CC</sub> = 4.5 to 5.5 V |      |      |

| Symbol                      | Parameter                                                         | Conditions   | Min                                                 | Max  | Min  | Max        | Min                            | Max  | Unit |

| V <sub>L</sub> = 2.3 to 2.3 | 7 V                                                               |              |                                                     |      |      |            |                                |      |      |

| t <sub>RVL</sub>            | I/O V <sub>L</sub> Rise Time                                      | Figure 8     | 34                                                  | 400  | 28.0 | 300        | 24.0                           | 208  | nS   |

| t <sub>RVCC</sub>           | I/O V <sub>CC</sub> Rise Time                                     | Figure 8     | 35.0                                                | 352  | 24.0 | 280        | 12.0                           | 180  | nS   |

| t <sub>FVL</sub>            | I/O V <sub>L</sub> Fall Time                                      | Figure 8     | 4.4                                                 | 6.9  | 4.3  | 6.2        | 4.2                            | 7.8  | nS   |

| t <sub>FVCC</sub>           | I/O V <sub>CC</sub> Fall Time                                     | Figure 8     | 4.3                                                 | 8.8  | 4.9  | 9.4        | 5.4                            | 10.4 | nS   |

| t <sub>PHLVL-VCC</sub>      | Propagation Delay                                                 | <b>F</b> i o | 1.7                                                 | 14.0 | 2.0  | 14.0       | 2.1                            | 14.0 | -    |

| t <sub>PLHVL-VCC</sub>      | (Driving I/O V <sub>L</sub> , V <sub>L</sub> to V <sub>CC</sub> ) | Figure 2     | 43.0                                                | 250  | 36.0 | 210        | 27.0                           | 210  | nS   |

| t <sub>PHLVCC-VL</sub>      | Propagation Delay                                                 | _            | 1.8                                                 | 13.0 | 2.6  | 13.0       | 1.2                            | 13.0 | -    |

| t <sub>PLHVCC-VL</sub>      | (Driving I/O V <sub>CC</sub> , $V_{CC}$ to V <sub>L</sub> )       | Figure 3     | 44.0                                                | 225  | 37.0 | 180        | 27.0                           | 144  | nS   |

| t <sub>EN</sub>             | Enable Time                                                       | Figure 7     |                                                     | 50   |      | 40         |                                | 35   | nS   |

| t <sub>DIS</sub>            | Disable Time                                                      | Figure 7     |                                                     | 265  |      | 230        |                                | 215  | nS   |

| t <sub>PPSKEW</sub>         | Part-to-Part Skew                                                 |              |                                                     | 0.7  |      | 0.7        |                                | 0.7  | nS   |

| MDR                         | Maximum Data Rate                                                 |              | 2                                                   |      | 2    |            | 2                              |      | Mbps |

| V <sub>L</sub> = 3.0 to 3.0 | 5 V                                                               |              |                                                     |      | •    | •          |                                |      |      |

| t <sub>RVL</sub>            | I/O V <sub>L</sub> Rise Time                                      | Figure 8     |                                                     |      | 25.0 | 400        | 19.0                           | 278  | nS   |

| t <sub>RVCC</sub>           | I/O V <sub>CC</sub> Rise Time                                     | Figure 8     |                                                     |      | 26.0 | 375        | 14.0                           | 247  | nS   |

| t <sub>FVL</sub>            | I/O V <sub>L</sub> Fall Time                                      | Figure 8     |                                                     |      | 2.8  | 6.1        | 2.6                            | 5.7  | nS   |

| t <sub>FVCC</sub>           | I/O V <sub>CC</sub> Fall Time                                     | Figure 8     |                                                     |      | 2.6  | 7.6        | 3.1                            | 8.3  | nS   |

| t <sub>PHLVL-VCC</sub>      | Propagation Delay                                                 | <b>F</b> i o |                                                     |      | 1.3  | 10.0       | 1.4                            | 8.0  | -    |

| t <sub>PLHVL-VCC</sub>      | (Driving I/O V <sub>L</sub> , V <sub>L</sub> to V <sub>CC</sub> ) | Figure 2     |                                                     |      | 36.0 | 255        | 28.0                           | 243  | nS   |

| t <sub>PHLVCC-VL</sub>      | Propagation Delay                                                 | <b>F</b>     |                                                     |      | 1.0  | 124        | 1.0                            | 97.0 | 6    |

| t <sub>PLHVCC-VL</sub>      | (Driving I/O $V_{CC}$ , $V_{CC}$ to $V_L$ )                       | Figure 3     |                                                     |      | 3.0  | 185        | 3.0                            | 136  | nS   |

| t <sub>EN</sub>             | Enable Time                                                       | Figure 7     |                                                     |      |      | 40         |                                | 35   | nS   |

| t <sub>DIS</sub>            | Disable Time                                                      | Figure 7     |                                                     |      |      | 250        |                                | 205  | nS   |

| t <sub>PPSKEW</sub>         | Part-to-Part Skew                                                 |              |                                                     |      |      | 0.7        |                                | 0.7  | nS   |

| MDR                         | Maximum Data Rate                                                 |              |                                                     |      | 2    |            | 2                              |      | Mbps |

#### **TEST SETUPS**

Figure 3. Rail-to-Rail Driving I/O V<sub>CC</sub>

Figure 4. Open–Drain Driving I/O VL

Figure 5. Open–Drain Driving I/O V<sub>CC</sub>

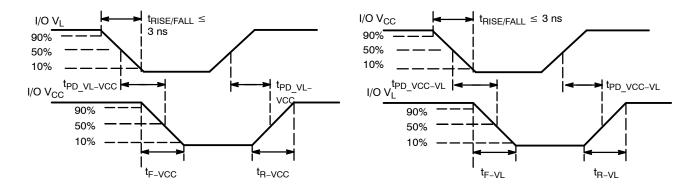

Figure 6. Definition of Timing Specification Parameters

| Test                                | Switch |

|-------------------------------------|--------|

| t <sub>PZH</sub> , t <sub>PHZ</sub> | Open   |

| t <sub>PZL</sub> , t <sub>PLZ</sub> | 2 x V* |

$C_L$  = 15 pF or equivalent (Includes jig and probe capacitance)  $R_L$  =  $R_1$  = 50 k $\Omega$  or equivalent

$R_T = Z_{OUT}$  of pulse generator (typically 50  $\Omega$ ) V\* = V<sub>L</sub> or V<sub>CC</sub> for I/O\_VL or I/O\_VCC measurements,

respectively.

Figure 8. Timing Definitions for Propagation Delays and Enable/Disable Measurement

#### **APPLICATIONS INFORMATION**

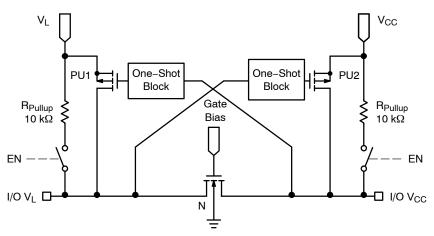

#### Level Translator Architecture

The NLSX0102 auto sense translator provides bi-directional voltage level shifting to transfer data in multiple supply voltage systems. This device has two supply voltages,  $V_L$  and  $V_{CC}$ , which set the logic levels on the input and output sides of the translator. When used to transfer data from the  $V_L$  to the  $V_{CC}$  ports, input signals referenced to the  $V_L$  supply are translated to output signals with a logic level matched to  $V_{CC}$ . In a similar manner, the  $V_{CC}$  to  $V_L$ translation shifts input signals with a logic level compatible to  $V_{CC}$  to an output signal matched to  $V_L$ .

The NLSX0102 consists of two bi-directional channels that independently determine the direction of the data flow without requiring a directional pin. The one-shot circuits are used to detect the rising or falling input signals. In addition, the one shots decrease the rise and fall time of the output signal for high-to-low and low-to-high transitions. Each input/output channel has an internal 10 k $\Omega$  pull-up. The magnitude of the pull-up resistors can be reduced by connecting external resistors in parallel to the internal 10 k $\Omega$  resistors.

#### **Input Driver Requirements**

The rise  $(t_R)$  and fall  $(t_F)$  timing parameters of the open drain outputs depend on the magnitude of the pull-up resistors. In addition, the propagation times  $(t_{PD})$ , skew  $(t_{PSKEW})$  and maximum data rate depend on the impedance of the device that is connected to the translator. The timing parameters listed in the data sheet assume that the output impedance of the drivers connected to the translator is less than 50 k $\Omega$ .

#### Enable Input (EN)

The NLSX0102 has an Enable pin (EN) that provides tri-state operation at the I/O pins. Driving the Enable pin to a low logic level minimizes the power consumption of the device and drives the I/O  $V_{CC}$  and I/O  $V_L$  pins to a high impedance state. Normal translation operation occurs when the EN pin is equal to a logic high signal. The EN pin is referenced to the  $V_L$  supply and has Overvoltage Tolerant (OVT) protection.

#### **Power Supply Guidelines**

During normal operation, supply voltage  $V_L$  must be less than or equal to  $V_{CC}$ . The sequencing of the power supplies will not damage the device during the power up operation. For optimal performance, 0.01  $\mu$ F to 0.1  $\mu$ F decoupling capacitors should be used on the  $V_L$  and  $V_{CC}$  power supply pins. Ceramic capacitors are a good design choice to filter and bypass any noise signals on the voltage lines to the ground plane of the PCB. The noise immunity will be maximized by placing the capacitors as close as possible to the supply and ground pins, along with minimizing the PCB connection traces.

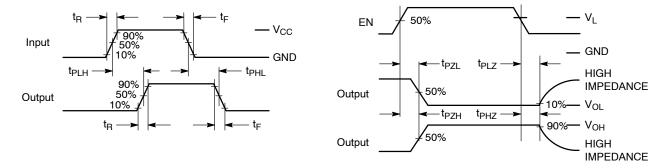

| <b>ORDERING I</b> | NFORMATION |

|-------------------|------------|

|-------------------|------------|

| Device         | Package                  | Shipping <sup>†</sup>                          |

|----------------|--------------------------|------------------------------------------------|

| NLSX0102FCT1G  | Flip–Chip 8<br>(Pb–Free) | 3000 / Tape & Reel                             |

| NLSX0102FCT2G  | Flip–Chip 8<br>(Pb–Free) | 3000 / Tape & Reel<br>(4mm Pitch Carrier Tape) |

| NLSX0102FC2T2G | Flip–Chip 8<br>(Pb–Free) | 3000 / Tape & Reel<br>(2mm Pitch Carrier Tape) |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# ONSEM<sup>1</sup>.

© Semiconductor Components Industries, LLC, 2019

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>