**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

## A Guide to Choosing the Right Ultra - Low I<sub>Q</sub> Low Dropout Linear Voltage Regulators

## **ON Semiconductor®**

http://onsemi.com

## APPLICATION NOTE

#### **Factors to Consider**

Introduction One of the most important challenges today in designing electronic applications is to minimize the power consumption of the system. To accomplish this, most systems utilize various low power modes which help to minimize the overall power consumption. When utilizing various modes of operation, system supply currents can easily vary from single µA or even fractions of µA in sleep to tenths or hundreds of mA in full power mode. Low Dropout Linear Voltage Regulators (popularly referred to as LDOs) are common building blocks in any power system and the choice of linear regulator can have an important impact on the overall system power consumption. To complicate this choice, it is often required that the LDO not only feature ultra-low quiescent current but should additionally provide good dynamic performance to assure stable, noise-free voltage rail, suitable for sensitive circuits. These requirements are often mutually exclusive and unveil a real challenge for the IC designers. As a consequence not many LDOs on the market can satisfy both these requirements simultaneously.

The following paper discusses the tradeoffs between achieving low  $I_Q$  and good dynamic performance when choosing an LDO, and some techniques that are now used to achieve an acceptable balance.

When choosing a linear regulator for a low power application, engineers predominantly search for ultra-low I<sub>O</sub> LDOs<sup>1</sup> meeting their input voltage and output current requirements. Whereas making a selection according to the I<sub>O</sub> specification gives some good initial information about the LDO's current consumption, two devices with equal or very similar IO can dramatically differ in terms of dynamic performance. Io can become rather a virtual parameter if we recall that it defines the ground current consumption without any load applied. In practical cases it may be more appropriate to look at the ground current consumption at very light loads from single  $\mu A$  to tenths or hundreds of  $\mu A$ . It is interesting to note that after evaluating different LDO products from different manufacturers, it was not uncommon to find that the I<sub>O</sub> specification given in the datasheet was for the perfect no load condition, and not the more realistic output load of 10  $\mu$ A to 100  $\mu$ A. Sometimes it may also be relevant to know the ground current behavior with respect to the input voltage or temperature. Apparently the ground current of some regulators available on the market increases considerably if the input voltage decreases and the LDO enters into its dropout region. This may be an important factor in choosing a product for battery operated equipment. Additional unexpected current consumption can have a negative impact on a product by considerably shortening its battery life. These undesired effects can be especially severe if the application spends most of the time in idle or sleep state drawing a minimum current. The designer should always read the datasheet notes for the  $I_{O}$ specification and where possible, examine the associated graphs of I<sub>O</sub> vs. I<sub>LOAD</sub> before making the decision to choose a particular LDO.

1. By specifying ultra–low  $I_Q$  here we refer to regulators with  $I_Q < 15\mu$ A.

### **Dynamic Parameters**

There are two main factors which influencing the dynamic performance of an Ultra-Low IO LDO regulator. The first is the technology process being used. The majority of ON Semiconductor's Ultra-Low IO LDOs are implemented using advanced CMOS or BiCMOS technologies with specific process flow options optimized for low power consumption, high speed Power Management ICs. Although the proper technology choice is essential it obviously doesn't guarantee in itself good dynamic parameters for LDO regulators. The second very important factor determining the final performance are the design techniques implemented in the design of the LDO, and this comes from design experience in this field. ON Semiconductor has over 40 years of experience in this field, and the latest generation of devices features ultra-low noise, good PSRR and ultra-low I<sub>O</sub> at the same time. To dip into the details let us review different types of regulators with respect to the dynamic performance.

#### **Constant Bias LDO Regulators**

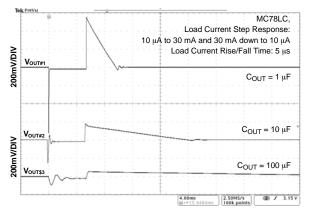

Traditionally Ultra–Low  $I_Q$  CMOS LDOs used constant biasing scheme. This means that ground current consumption was kept relatively constant across the available range of output currents. Examples of such devices are the MC78LC or NCP551 featuring an  $I_{GND}$  (or  $I_Q$ ) of 1.5  $\mu$ A and 4  $\mu$ A respectively. These devices are very well suited for battery powered applications with less demanding performance requirements. Their primary disadvantage is relatively poor dynamic performance, namely load and line transients, PSRR or output noise. Often it is possible to tweak this dynamic performance by using larger output capacitors. Figure 1 shows how the MC78LC load transient overshoot and undershoot are improved by increasing the  $C_{OUT}$  from 1  $\mu$ F to 100  $\mu$ F.

Figure 1. MC78LC Load Transient Improvement

Table 1 below summarizes these results. As can be seen the transient amplitude was greatly reduced due to a larger  $C_{OUT}$ .

#### Table 1. MC78LC LOAD TRANSIENT AMPLITUDE

|            | Output Capacitor, C <sub>OUT</sub> |         |         |  |

|------------|------------------------------------|---------|---------|--|

|            | 1 μF                               | 10 μF   | 100 μF  |  |

| Overshoot  | +560 mV                            | +180 mV | +80 mV  |  |

| Undershoot | –720 mV                            | –240 mV | –100 mV |  |

Unfortunately while the transient amplitude decreased, the settling time increased at the same time. It should also be noted that when using large output capacitors it may be necessary to provide an external reverse protection diode between the  $V_{IN}$  and  $V_{OUT}$  pins. This will protect the regulator from the excessive reverse current which could otherwise flow through internal PMOS body diode during a sudden fall of the input voltage. Increasing  $C_{OUT}$  does not always achieve the desired performance. Furthermore it can be troublesome either due to the necessity of including the external protection diode or in applications requiring fast settling time, small solution size or small inrush currents. In such cases it is recommended to use some of the newer LDOs which are presented in the next sections.

#### **Proportional Bias LDO Regulators**

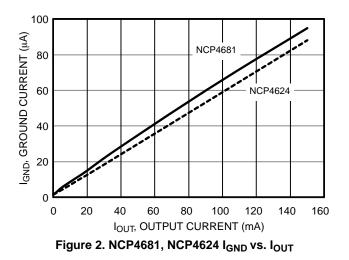

To improve the relatively poor dynamic behavior of the constant bias (constant  $I_{GND}$ ) LDOs, in newer devices ground current changes proportionally to the output current. Examples of such LDOs are the NCP4681 and NCP4624 featuring typical quiescent current of 1  $\mu$ A and 2  $\mu$ A respectively. Figure 2 demonstrates the concept used in the proportional  $I_{GND}$  LDOs. These devices are designed so that the  $I_{GND}$  starts to rise at  $I_{OUT} > 2$  mA.

It assures that the LDO current consumption at light loads is practically constant and corresponds very well with the  $I_Q$ specification given in the datasheet. The comparison between NCP4681 and MC78LC PSRR at 100 Hz and  $I_{OUT}$ = 30 mA shows about 15 dB improvement from 38 dB to 53 dB. As will be discussed later, the improvement in load transient response is even more noticeable. Although the proportional bias technique provides improved dynamic parameters with respect to constant  $I_{GND}$  LDOs, in highly demanding, precision applications requiring very clean power supply rail and ultra–low  $I_Q$  this performance may still be insufficient.

#### Adaptive Bias LDO Regulators

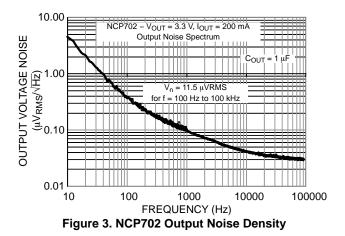

To provide excellent dynamic parameters and ultra–low  $I_Q$  at the same time the newest generation of ON Semiconductor LDOs implement a technique called adaptive ground current. These regulators use special techniques to boost the ground current at a certain level of output current without compromising light load efficiency. Due to this, the end application can benefit from good load/line transients, PSRR and output noise. Examples of ICs featuring the adaptive ground current technique are the NCP4587/9 and NCP702 having an I<sub>Q</sub> of 1.5  $\mu$ A and 9  $\mu$ A respectively. The NCP702 is additionally optimized in terms of noise featuring typ. 11.5  $\mu$ V<sub>RMS</sub> in 100 Hz to 100 kHz noise bandwidth. It is very well suited for powering sensitive Analog, RF circuitry in environments requiring long battery life and small solution size.

#### **Comparison of the Three LDO Types**

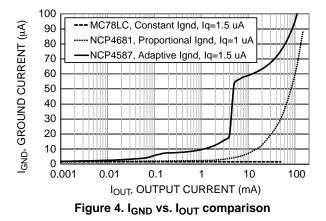

Figure 4 shows the ground current versus output current comparison for the three types of ultra-low  $I_Q$  LDOs described above. All regulators used in the comparison feature very similar quiescent current specification of 1  $\mu$ A to 1.5  $\mu$ A. Their ground current dependence on the output current is very different. As a consequence the dynamic performance of these regulators also differs considerably.

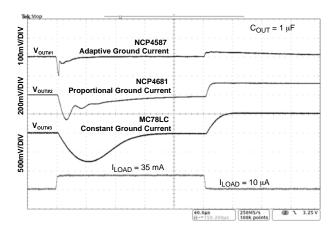

The load transient performance advantage of NCP4587, an adaptively biased LDO as illustrated on Figure 5 is evident. The transient amplitudes are summarized in Table 2.

Figure 5. Load Transient Comparison

|            | Ultra–Low I <sub>Q</sub> LDO |         |         |  |

|------------|------------------------------|---------|---------|--|

|            | MC78LC                       | NCP4681 | NCP4587 |  |

| Overshoot  | +560 mV                      | +120 mV | +30 mV  |  |

| Undershoot | –750 mV                      | –260 mV | –100 mV |  |

# Table 2. ULTRA-LOW IQ LDO LOAD TRANSIENT AMPLITUDE

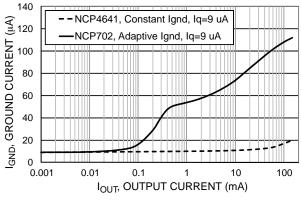

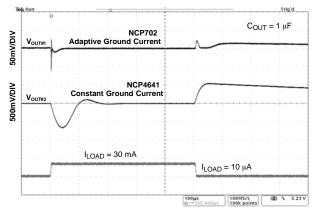

Similarly to the previous comparison Figures 6 and 7 presents  $I_{GND}$  and corresponding load transient comparison between NCP702 (an adaptive type LDO) and NCP4641 (a constant bias LDO). Both ICs feature an  $I_Q$  of 9  $\mu$ A but again the transient performance is notably better in the case of the adaptive voltage regulator.

Figure 6. I<sub>GND</sub> vs. I<sub>OUT</sub> comparison

Figure 7. Load Transient Comparison

#### **AE Pin Functionality**

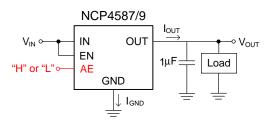

Another feature deserving of mention which may be used to improve the dynamic parameters of Ultra–Low  $I_Q$  regulators is commonly called Auto–ECO functionality (Figure 8).

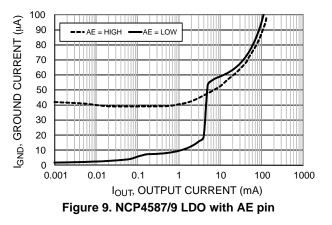

Figure 8. NCP4587/9 LDO with AE pin

Setting the additional AE pin to a logic low level allows the user to configure the regulator as an adaptive ground current Ultra–Low  $I_O$  LDO. Pulling the AE pin to a high logic level the ground current consumption at low output current is raised to approximately 40  $\mu$ A which substantially improves the load transient response from very light to large loads. At higher load currents the I<sub>GND</sub> in both modes of operation is approximately equal and there is basically no difference in the dynamic performance. Figure 9 shows how the AE pin state influences the ground current consumption of the regulator.

The AE pin becomes helpful in applications where the system is periodically brought from sleep mode to full-power mode. If the transition between these two states is very fast, large undershoots could be experienced. Although NCP4587/9 features very good load transient response in comparison to other LDOs, by connecting the AE pin with a MCU I/O line (for example) and then indicating ahead of time an increase in load current demand via the I/O line, the undershoot can be further optimized. As a practical example, many GPS receiver chipsets are equipped with an external WAKEUP signal to indicate ahead of time a switching of the GPS from a hibernate state. This signal is usually connected to an external active antenna supply and can also be used in conjunction with the regulator powering the GPS chipset. In this way the regulator will be manually set to higher ground current consumption mode before the GPS transition from hibernate to full-power mode, improving its dynamic performance.

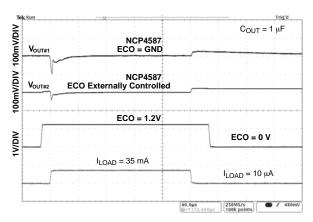

Figure 10. NCP4587 Load Transient improvement

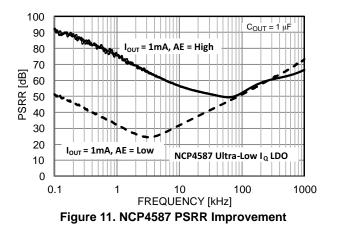

Figure 10 shows the transient improvement by using the AE pin function. The top most waveform (V<sub>OUT#1</sub>) was registered for the condition that AE pin was permanently connected to GND. The waveform below (VOUT#2) shows the improved load transient where the AE was manually set to a logic high state approximately 20 µs before the high load current demand occurred. Generally it is sufficient, that the AE logic high is set 1  $\mu$ s – 2  $\mu$ s before the load transient event occurs. Yet another situation where the ECO function can prove to be useful is where the application requires ultra-low I<sub>O</sub> for very light load currents but already at 1 mA - 3 mA demands very good PSRR and line/load transient characteristics. Figure 11 shows that more than 40 dB improvement in PSRR at 1 kHz, I<sub>OUT</sub> = 1 mA to 3 mA is possible, if the AE pin is switched from a low to a high logic state.

#### **Quiescent Current Specifications**

Next, we will take a closer look at datasheet quiescent current specifications vs. actual measurements. As we will see in some cases the number stated on the datasheet title page can be very different from the actual measured value. We will identify some parameters to look at in order to avoid unexpected current consumption.

#### **Quiescent Current – A Case Study**

As an example let us consider two very similar LDOs, both with adaptive ground current configurations: the NCP702 with typical  $I_Q = 10 \,\mu\text{A}$  and a competitor LDO with typical  $I_Q = 11 \,\mu\text{A}$ . Tables 3 and 4 show the datasheet value of the quiescent current ( $I_{OUT} = 0 \,\mu\text{A}$ ) and actual ground current consumption measured for  $I_{OUT} = 10 \,\mu\text{A}$  and 50  $\mu\text{A}$ .

LDO1: NCP702 - V<sub>OUT</sub> = 3.3 V, V<sub>IN</sub> = 3.6 V

#### Table 3. NCP702 MEASUREMENT VS. SPECIFICATION

| Datasheet:<br>I <sub>Q</sub> , I <sub>OUT</sub> =<br>0 μΑ | Measured:<br>I <sub>GND</sub> at I <sub>OUT</sub> =<br>10 μΑ | Measured:<br>I <sub>GND</sub> at I <sub>OUT</sub> = 50 μA |  |

|-----------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------|--|

| Тур. 10 μА                                                | 9.2 μA                                                       | 11.5 μA                                                   |  |

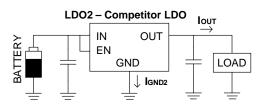

LDO2: Competitor LDO –  $V_{OUT} = 3.3 \text{ V}, V_{IN} = 3.6 \text{ V}$

## Table 4. COMPETITOR MEASUREMENT VS. DATASHEET

| Datasheet:<br>I <sub>Q</sub> , I <sub>OUT</sub> =<br>0 μΑ | Measured:<br>I <sub>GND</sub> at I <sub>OUT</sub> =<br>10μ Α | Measured:<br>I <sub>GND</sub> at I <sub>OUT</sub> = 50 μA |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Тур. 11 μА                                                | 16.4 μA                                                      | 22.1 μA                                                   |  |  |

In the case of the NCP702 the measured  $I_{GND}$  at  $I_{OUT} = 10 \ \mu$ A matches very closely to the datasheet value of  $I_Q$ . In the case of the competitor LDO at  $I_{OUT} = 10 \ \mu$ A the actual result is 49% higher than what we could predict from the datasheet. There are two reasons for that. The first is that the competitor  $I_Q$  specification does not include the EN (Enable) pin input current which flows through an internal pull–down resistor to ground. Measurements show that this internal pull–down resistance is in the order of 1 MQ. If the EN pin is connected to the  $V_{in}$  pin, the ground current will be heavily influenced by the input voltage. In this case the input voltage is 3.6 V so there is additional 3.6  $\mu$ A of current consumption due to pull–down resistance. By contrast, the NCP702 has internal 100 nA pull–down current source and the enable current is independent on the input voltage.

The second reason why the  $I_Q$  spec. doesn't match with reality is that the adaptive ground current used in the competitive LDO is set in such a way that the  $I_{GND}$  starts to increase at very low output currents, much lower than the NCP702 threshold

It may be of interest to designers to note that the NCP702 can be offered with a customized adaptive ground current curve. On request, the NCP702 can be configured at the factory so that the I<sub>GND</sub> consumption is held at ultra–low level, matching the I<sub>Q</sub> specification up to I<sub>OUT</sub>  $\approx$  2 mA. For the available options please contact your local sales office.

# Quiescent Current Differences and the Impact on Battery Life

We could ask ourselves if the ground current difference measured and discussed previously really matters and could seriously impact the battery life performance. Unfortunately the answer to this question isn't straightforward and it depends on the specific end application where the LDO is being used.

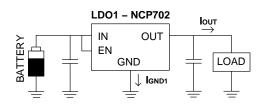

As an example let us consider the basic application shown on Figures 12 and 13 where the LDO is used to down–convert the battery voltage and provide a current to the load.

Figure 12. Basic Application using the NCP702

# Figure 13. Basic Application Using the Competitor LDO

The battery life for the application shown on Figures 12 and 13 can be described by a general formula:

Battery Life (h) =

$$\frac{\text{Battery Capacity (mAh)}}{\text{Average Current (mA)}}$$

Examining the case of the NCP702 (LDO1) we have:

Battery Life 1 =

$$\frac{\text{Battery Capacity}}{I_{\text{OUT}} + I_{\text{GND1}}}$$

For the competitor LDO (LDO2) we have:

Battery Life 2 =

$$\frac{\text{Battery Capacity}}{I_{OUT} + I_{OUD2}}$$

From the two equations shown above we can calculate the battery life saving offered by NCP702 over the competitive solution:

Battery Life Saving % =

$$\frac{I_{GND2} - I_{GND1}}{I_{OUT} + I_{GND1}}$$

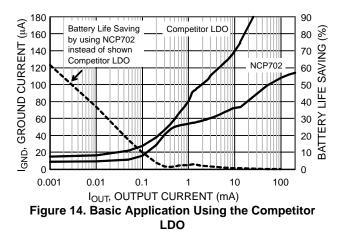

The resulting equation becomes meaningful after plugging—in the measured ground current vs. output current values for the two LDOs considered. Figure 14 illustrates the Battery Life Saving and the two LDO  $I_{GND}$  plotted against the output current.

What we can see is that the savings will be roughly 20% for light load,  $I_{OUT} = 40 \ \mu$ A. At larger loads, as the LDO ground current becomes less prominent in comparison with the output current drawn from the battery there is no evident advantage in the battery life between the two solutions.

Generally in applications where other large current contributions exist, the battery life saving can be less severe than the calculated one. Nevertheless it may pay–off to apply the basic calculations and check the results before making the final selection of an Ultra–Low  $I_O$  LDO.

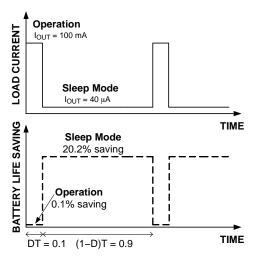

#### Battery Life Impact of a Variable Load Current

Since it is quite seldom that the LDO output current is constant (as we assumed in the above example) we may want to extend the considerations and include the case of a changing load. Usually it is much more often the case that the circuitry being powered by the regulator transitions between sleep and operation. As an example Figure 15 shows the load current profile of an application working with a 10% duty cycle. The load draws 40  $\mu$ A in sleep and 100 mA in operation. At I<sub>OUT</sub> = 40  $\mu$ A the NCP702 will add 11.1  $\mu$ A of its own ground current yielding a total battery current of 51.1  $\mu$ A. In the case of competitor LDO it will add 21.4  $\mu$ A yielding a total current of 61.4  $\mu$ A. If we express this current difference in percents the result shows–up 20.2%. This number represents the battery life saving in the sleep mode.

Figure 15. Example Load Current Profile

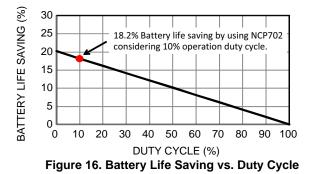

Figure 16 shows the battery life saving vs. the duty cycle. For the particular case of 10% duty cycle there is still 18.2% lifetime benefit of NCP702.

#### Ground Current in the Dropout Region

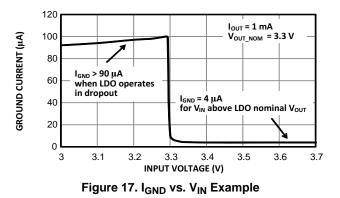

Another important, but often overlooked parameter of the LDO is the ground current consumption if it enters a dropout condition. In Li–Ion or Li–Poly battery powered products it is common to regulate the power supply with reasonably high efficiency using LDOs to produce a 3.3 V or 3.1 V output voltage. However, as the battery discharges and its' voltage decays, the  $V_{IN}$  of the LDO may approach  $V_{OUT}$  to the point where the regulator enters its dropout region. In such cases, most of the Ultra–Low I<sub>O</sub> LDOs available on the

market will start to draw significantly higher ground current than what could be expected relying solely on the datasheet values stated in the electrical table. To illustrate the problem, Figure 17 shows the  $I_{GND}$  vs.  $V_{IN}$  for a typical Ultra–Low  $I_O$  LDO

In the dropout region the regulator starts to draw up to  $100 \,\mu$ A. To tackle this problem in power conscious applications it may be advisable to add a very low power supervisor with adjustable hysteresis to account for the battery voltage recovery after the load is removed. In some cases where the hysteresis is insufficient other voltage detectors with a latched output may be better suited. This will however result in the necessity to clear the latch using either a push button or the information from the battery charge controller.

The latest generation of ON Semiconductor Ultra–Low  $I_Q$  LDOs incorporates an integrated dropout condition detector which will prevent the ground current increase during low input voltage conditions. Examples of devices incorporating this idea are the NCP702 and the NCP4681.

#### Summary

Traditionally, improving the current consumption of an LDO meant sacrificing dynamic performance. With newer process technologies and design techniques, there are now LDOs available which now make these compromises less dramatic. However, the application designer needs to pay careful attention to the LDO datasheet to understand the operation of the device and to select their solution according to the key requirements of their application.

## AND9089/D

| Part Number   | Ground Current           | Typ. I <sub>Q</sub> | Max. V <sub>IN</sub> | Rated I <sub>OUT</sub> | Package                                              | Special Feature                            | Note     |

|---------------|--------------------------|---------------------|----------------------|------------------------|------------------------------------------------------|--------------------------------------------|----------|

| NCP4681/2/4/5 | Proportional             | 1 μΑ                | 6 V                  | 150 mA                 | SC-88A-5 , SC-70-5,<br>SOT-323-5<br>SC-82AB-4, UDFN4 | Soft–Start, Enable Pin                     | Obsolete |

| MC78LC        | Constant                 | 1.5 μA              | 12 V                 | 80 mA                  | SOT-89, TSOP-5                                       | -                                          |          |

| NCP4587/9*    | Adaptive/Constant        | 1.5 μA              | 6 V                  | 150/300 mA             | SOT-23-5, XDFN6                                      | Foldback current limit, Enable Pin         | Obsolete |

| NCP4624       | Proportional             | 2 μΑ                | 12 V                 | 150 mA                 | SC-88A-5, SC-70-5,<br>SOT-323-5<br>SOT-23-5, UDFN4   | Reverse current protection                 | Obsolete |

| NCP698        | Constant                 | 2.5 μΑ              | 6 V                  | 150 mA                 | SC-82AB-4                                            | Enable Pin                                 |          |

| NCV662/3      | Constant                 | 2.5 μΑ              | 6 V                  | 100 mA                 | SC-82AB-4                                            | Enable Pin                                 |          |

| NCV553        | Constant                 | 2.8 μA              | 12 V                 | 80 mA                  | SC-82AB-4                                            | Enable Pin                                 |          |

| NCP551        | Constant                 | 4 μΑ                | 12 V                 | 150 mA                 | TSOP-5, SOT23-5                                      | Enable Pin                                 |          |

| NCP4623       | Constant                 | 5 μΑ                | 24 V                 | 150 mA                 | SOT23–5, XDFN6                                       | Foldback current limit, Enable Pin         | Obsolete |

| NCP4626*      | Proportional<br>Low/High | 6 μΑ                | 18 V                 | 300 mA                 | SOT23–5, XDFN6                                       | Reverse current protection,<br>Enable Pin  | Obsolete |

| NCP702        | Adaptive                 | 9 µA                | 5.5V                 | 200 mA                 | SOT23–5, XDFN6,<br>TSOP–5                            | Ultra-Low Noise, Soft-Start,<br>Enable Pin |          |

| NCP4640/1     | Constant                 | 9 μA                | 50 V                 | 50/150 mA              | SOT-89-5                                             | Enable pin                                 | Obsolete |

| NCP4588       | Proportional             | 9.5 μA              | 5.3 V                | 200 mA                 | SC-88A-5,<br>SC-70-5,SOT-323-5<br>XDFN6              | Capacitor-less LDO, Enable Pin             | Obsolete |

| NCP715        | Constant                 | 4.7 μΑ              | 24 V                 | 50 mA                  | XDFN6, SC-88A                                        | Fixed output voltage, current limit        | New      |

| NCP716        | Constant                 | 4.7 μΑ              | 24 V                 | 80 mA                  | WDFN6                                                | Fixed output voltage, current limit        | New      |

| NCP718        | Proportional             | 4 μΑ                | 24 V                 | 300 mA                 | SOT23-5, WDFN6                                       | Adjustable output voltage                  | New      |

| NCP170        | Proportional             | 0.5 μA              | 5.5 V                | 150 mA                 | SOT-563, XDFN4                                       | Enable Pin                                 | New      |

#### Table 5. ON SEMICONDUCTOR ULTRA-LOW IQ LDO PRODUCTS OFFERING:

\*Modes of operation are selectable through the external AE pin.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdt/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor "Typical" parameters which may be provided in ON Semiconductor dates the and or each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products harmeds, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application. Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against a

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

ON Semiconductor Website: www.onsemi.com Order Literature: http://www.onsemi.com/orderlit

Europe, Middle East and Africa Technical Support: C Phone: 421 33 790 2910

For additional information, please contact your local Sales Representative