# onsemi

## 6-Channel LED Driver with I<sup>2</sup>C Interface

### **CAT3626**

#### Description

The CAT3626 is a high efficiency 1x/1.5x fractional charge pump with programmable dimming current in six LED channels. To ensure uniform brightness in LCD backlight applications, each LED channel delivers an accurate regulated current.

Low noise and input ripple is achieved by operating at a constant switching frequency of 1 MHz which allows the use of small external ceramic capacitors. The 1x/1.5x fractional charge pump supports a wide range of input voltages from 3 V to 5.5 V with efficiency up to 91%, and is ideal for Li–Ion battery powered devices.

The LED channels are configured into three independent pairs, each containing 2 matched channels. Each pair can be separately programmed from zero to 32 mA, in 0.5 mA resolution steps, using the  $I^2C$  serial interface. Any individual channel can be disabled while others remain active. When the enable input (EN) is low, the device is in shutdown mode drawing zero current.

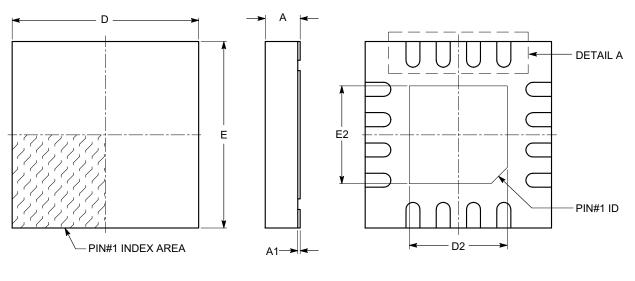

The device is available in a 16-pad TQFN package with a max height of 0.8 mm.

#### Features

- Drives 6 LED Channels

- Independent Current on 3 Pairs of LEDs

- I<sup>2</sup>C Serial Interface Programming

- Adjustable Current to 32 mA in 0.5 mA Step

- Power Efficiency up to 91%

- Fractional Pump 1x/1.5x

- Low Noise Input Ripple

- Fixed High Frequency Operation 1 MHz

- "Zero" Current Shutdown Mode

- Soft Start and Current Limiting

- Short Circuit Protection

- Thermal Shutdown Protection

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### Applications

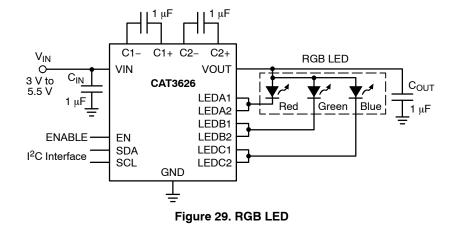

- RGB LEDs

- LCD and Keypad Backlighting

- Cellular Phones, PDAs

- Digital Cameras

TQFN-16 HV4 SUFFIX CASE 510AE

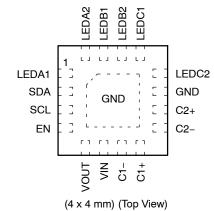

#### **PIN CONNECTIONS**

#### MARKING DIAGRAMS

| G626 | CDAJ |

|------|------|

| AXXX | AXXX |

| YMCC | YMCC |

G626 = CAT3626HV4-T2

CDAJ = CAT3626HV4-GT2

A = Assembly Location

XXX = Last Three Digits of Assembly Lot Number

- Y = Production Year (Last Digit)

- M = Production Month (1-9, A, B, C)

- CC = Country of Origin (Two Digit)

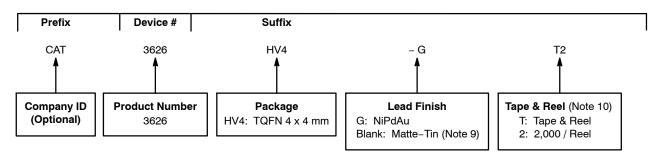

#### **ORDERING INFORMATION**

| Device         | Package   | Shipping <sup>†</sup> |  |  |

|----------------|-----------|-----------------------|--|--|

| CAT3626HV4-GT2 | TQFN-16   | 2,000/                |  |  |

| (Note 2)       | (Pb-Free) | Tape & Reel           |  |  |

#### **DISCONTINUED** (Note 3)

| (Note 1) (Pb-Fre | ee) Tape & Reel |

|------------------|-----------------|

- †For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

- 1. Matte-Tin Plated Finish (RoHS-compliant).

- 2. NiPdAu Plated Finish (RoHS-compliant).

- 3. **DISCONTINUED:** This device is not recommended for new design. Please contact your **onsemi** representative for information. The most current information on this device may be available on <u>www.onsemi.com</u>.

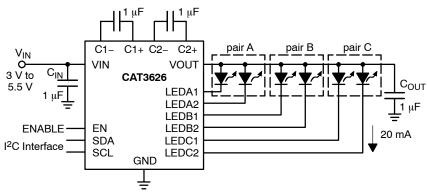

Figure 1. Typical Application Circuit

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameters                 | Ratings     | Units |

|----------------------------|-------------|-------|

| VIN, LEDxx voltage         | 6           | V     |

| VOUT, C1±, C2± voltage     | 7           | V     |

| EN, SDA, SCL voltage       | VIN + 0.7 V | V     |

| Storage Temperature Range  | -65 to +160 | °C    |

| Junction Temperature Range | -40 to +150 | °C    |

| Lead Temperature           | 300         | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Table 2. RECOMMENDED OPERATING CONDITIONS

| Parameter                    | Range      | Units |

|------------------------------|------------|-------|

| VIN                          | 3 to 5.5   | V     |

| Ambient Temperature Range    | -40 to +85 | °C    |

| LED forward voltage          | Up to 4.2  | V     |

| I <sub>LED</sub> per LED pin | 0 to 32    | mA    |

NOTE: Typical application circuit with external components is shown above.

VIN = 3.6 V, EN = High, ambient temperature of 25°C (over recommended operating conditions unless specified otherwise)

| Symbol                                                      | Parameter                                                                            | Test Conditions                                                                            | Min                   | Тур        | Max                   | Units        |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|------------|-----------------------|--------------|--|

| lQ                                                          | Quiescent Current                                                                    | Quiescent Current 1x mode, all LEDs Off<br>1x mode, all LEDs On<br>1.5x mode, all LEDs Off |                       |            |                       | mA           |  |

| I <sub>QSHDN</sub>                                          | Shutdown Current                                                                     | V <sub>EN</sub> = 0 V                                                                      |                       | 0          | 1                     | μA           |  |

| I <sub>LED</sub>                                            | LED Current Range with 6 LEDs                                                        |                                                                                            | 0                     |            | 32                    | mA           |  |

| I <sub>LED-ACC</sub>                                        | LED Current Accuracy                                                                 | $1 \text{ mA} \leq I_{\text{LED}} \leq 31 \text{ mA}$                                      |                       | ±3         |                       | %            |  |

| I <sub>LED-DEV</sub>                                        | LED Channel Matching                                                                 | (I <sub>LED</sub> – I <sub>LEDAVG</sub> ) / I <sub>LEDAVG</sub>                            |                       | ±3         |                       | %            |  |

| R <sub>OUT</sub>                                            | Output Resistance (open loop)                                                        | 1x mode, I <sub>OUT</sub> = 120 mA<br>1.5x mode, I <sub>OUT</sub> = 120 mA                 |                       | 0.5<br>2.8 |                       | Ω            |  |

| F <sub>OSC</sub>                                            | Charge Pump Frequency                                                                |                                                                                            | 0.8                   | 1          | 1.3                   | MHz          |  |

| I <sub>SC_MAX</sub>                                         | Output short circuit Current Limit                                                   | V <sub>OUT</sub> < 0.5 V                                                                   |                       | 60         |                       | mA           |  |

| I <sub>IN_MAX</sub>                                         | Input Current Limit                                                                  | 1x mode, V <sub>OUT</sub> > 1 V                                                            |                       | 300        |                       | mA           |  |

| I <sub>EN</sub><br>V <sub>HI-EN</sub><br>V <sub>LO-EN</sub> | EN Pin<br>– Input Leakage<br>– Logic High Level<br>– Logic Low Level                 |                                                                                            | -1<br>1.3             |            | 1<br>0.4              | μΑ<br>V<br>V |  |

| V <sub>HI</sub><br>V <sub>LO</sub>                          | I <sup>2</sup> C SDA, SCL<br>– High Level Input Voltage<br>– Low Level Input Voltage |                                                                                            | 0.7 x V <sub>IN</sub> |            | 0.3 x V <sub>IN</sub> | V<br>V       |  |

| T <sub>SD</sub>                                             | Thermal Shutdown                                                                     |                                                                                            |                       | 165        |                       | °C           |  |

| T <sub>HYS</sub>                                            | Thermal Hysteresis                                                                   |                                                                                            |                       | 20         | 1                     | °C           |  |

| V <sub>UVLO</sub>                                           | Under-voltage lock out (UVLO) threshold                                              |                                                                                            |                       | 2          |                       | V            |  |

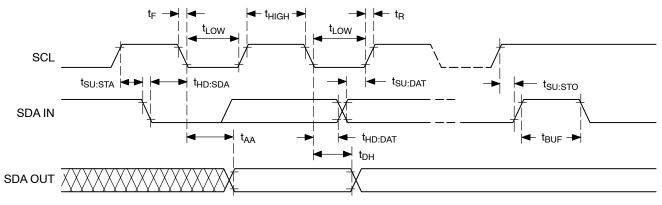

| Symbol              | Parameter                                             | Min | Тур | Max | Unit |

|---------------------|-------------------------------------------------------|-----|-----|-----|------|

| f <sub>SCL</sub>    | Clock Frequency                                       |     |     | 400 | kHz  |

| t <sub>AA</sub>     | SCL Low to SDA Data Out and ACK Out                   |     |     | 0.9 | μs   |

| t <sub>BUF</sub>    | Bus Free Time Before a New Transmission Can Start     | 1.2 |     |     | μs   |

| t <sub>HD:STA</sub> | Start Condition Hold Time                             | 0.6 |     |     | μs   |

| t <sub>LOW</sub>    | Clock Low Period                                      | 1.2 |     |     | μs   |

| t <sub>HIGH</sub>   | Clock High Period                                     | 0.6 |     |     | μs   |

| t <sub>SU:STA</sub> | Start Condition Setup Time (For a Repeated Condition) | 0.6 |     |     | μs   |

| t <sub>HD:DAT</sub> | Data In Hold Time                                     | 0   |     |     | ns   |

| t <sub>SU:DAT</sub> | Data In Setup Time                                    | 100 |     |     | ns   |

| t <sub>R</sub>      | SDA and SCL Rise Time                                 |     |     | 0.3 | μs   |

| t <sub>F</sub>      | SDA and SCL Fall Time                                 |     |     | 300 | ns   |

| t <sub>SU:STO</sub> | Stop Condition Setup Time                             | 0.6 |     |     | μs   |

| t <sub>DH</sub>     | Data Out Hold Time                                    | 50  |     |     | ns   |

**Table 4. A.C. CHARACTERISTICS**For 3 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, over full ambient temperature range -40°C to +125°C(over recommended operating conditions unless specified otherwise).

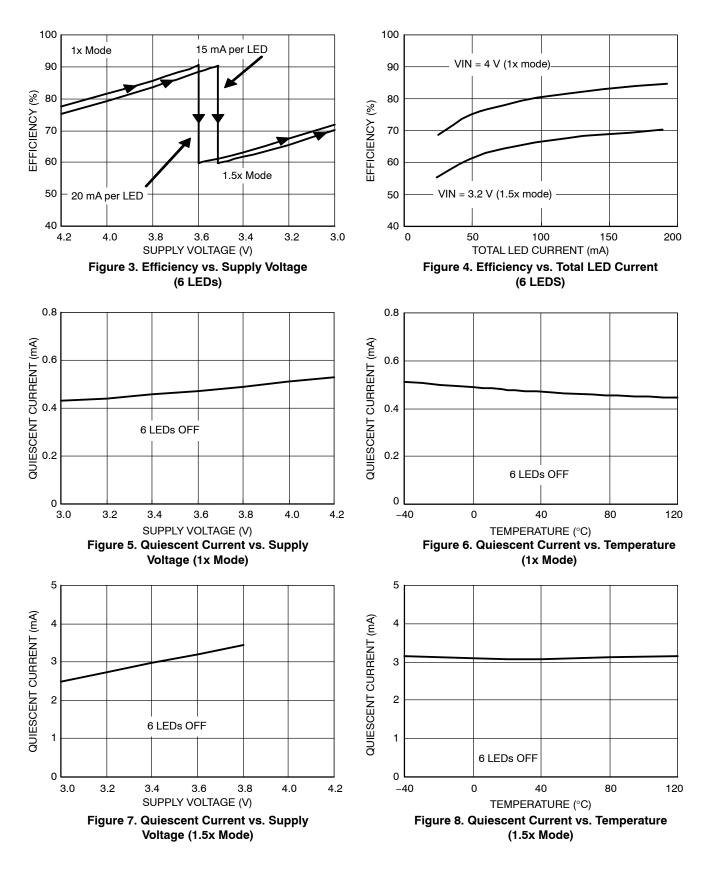

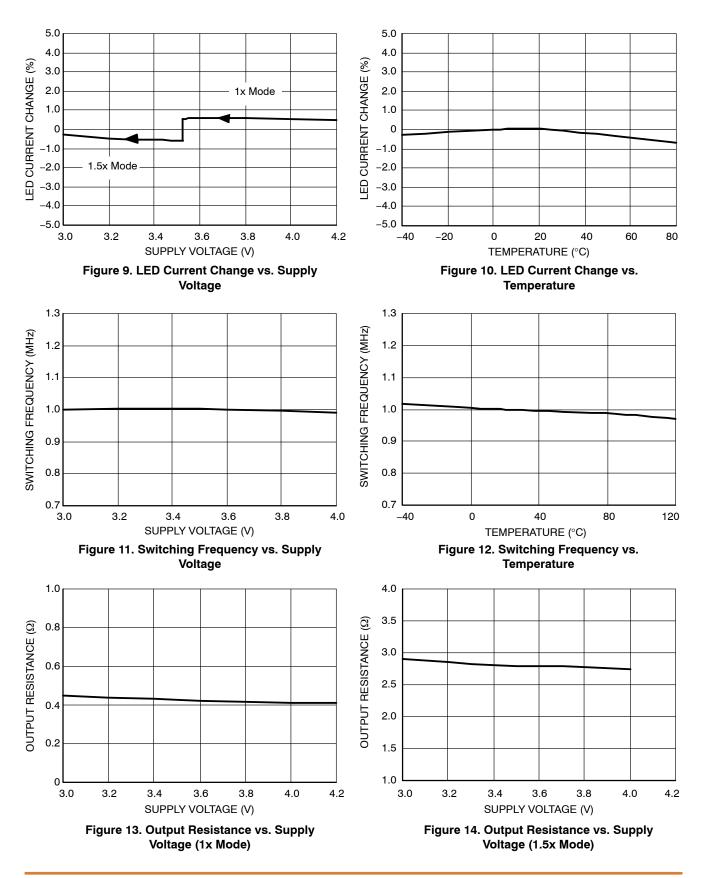

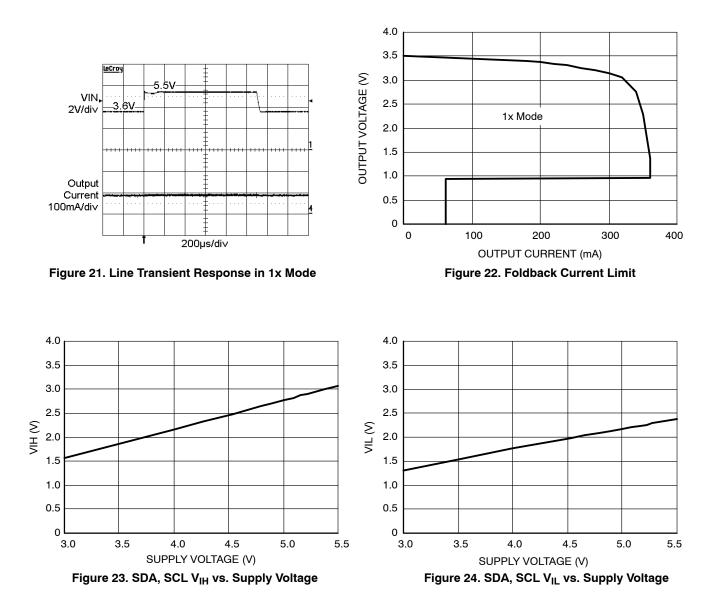

#### **TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS**

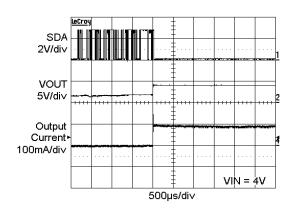

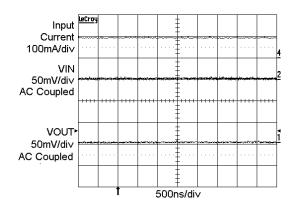

(V<sub>IN</sub> = 3.6 V, I<sub>OUT</sub> = 90 MA (6 LEDS AT 15 MA), EN =  $V_{IN}$ ,  $C_{IN} = C_1 = C_2 = C_{OUT} = 1$  MF,  $T_{AMB} = 25^{\circ}C$ , UNLESS OTHERWISE SPECIFIED.)

#### **TYPICAL CHARACTERISTICS**

$(V_{IN} = 3.6 \text{ V}, I_{OUT} = 90 \text{ MA} \text{ (6 LEDS AT 15 MA)}, \text{ EN} = V_{IN}, C_{IN} = C_1 = C_2 = C_{OUT} = 1 \text{ MF}, T_{AMB} = 25^{\circ}\text{C}, \text{ UNLESS OTHERWISE} \text{ SPECIFIED.})$

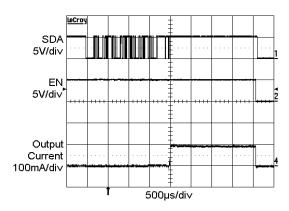

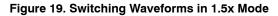

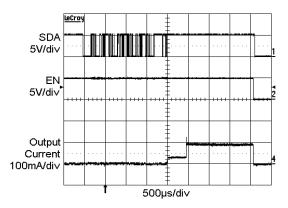

Figure 17. Enable Power Down (1x Mode)

Figure 16. Power Up with 6 LEDs at 15 mA (1.5x Mode)

Figure 18. Enable Power Down (1.5x Mode)

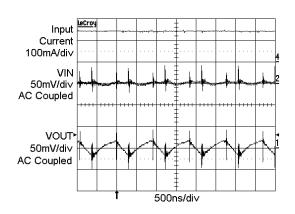

Figure 20. Operating Waveforms in 1x Mode

#### **TYPICAL CHARACTERISTICS**

(V<sub>IN</sub> = 3.6 V, I<sub>OUT</sub> = 90 MA (6 LEDS AT 15 MA), EN = V<sub>IN</sub>,  $C_{IN} = C_1 = C_2 = C_{OUT} = 1$  MF,  $T_{AMB} = 25^{\circ}C$ , UNLESS OTHERWISE SPECIFIED.)

| Pin # | Name  | Function                                       |

|-------|-------|------------------------------------------------|

| 1     | LEDA1 | Cathode terminal of LED A1                     |

| 2     | SDA   | I <sup>2</sup> C Serial data input/output      |

| 3     | SCL   | I <sup>2</sup> C Serial clock input            |

| 4     | EN    | Enable input                                   |

| 5     | VOUT  | Charge pump output connected to the LED anodes |

| 6     | VIN   | Supply voltage                                 |

| 7     | C1-   | Bucket capacitor 1 terminal                    |

| 8     | C1+   | Bucket capacitor 1 terminal                    |

| 9     | C2-   | Bucket capacitor 2 terminal                    |

| 10    | C2+   | Bucket capacitor 2 terminal                    |

| 11    | GND   | Ground reference                               |

| 12    | LEDC2 | Cathode terminal of LED C2                     |

| 13    | LEDC1 | Cathode terminal of LED C1                     |

| 14    | LEDB2 | Cathode terminal of LED B2                     |

| 15    | LEDB1 | Cathode terminal of LED B1                     |

| 16    | LEDA2 | Cathode terminal of LED A2                     |

|       | TAB   | Connect to Ground on PCB                       |

#### Table 5. PIN DESCRIPTIONS

#### **PIN FUNCTION**

**VIN** is the supply pin for the charge pump. A small  $1 \mu F$  ceramic bypass capacitor is required between the VIN pin and ground near the device. The operating input voltage range is from 2.2 V to 5.5 V. Whenever the input supply falls below the undervoltage threshold (2 V), all LEDs channels will be automatically disabled.

**EN** is the enable logic input for the driver. Guaranteed levels of logic high and logic low are set at 1.3 V and 0.4 V respectively. When EN is initially taken high, the device becomes enabled and all LED currents remain at 0 mA. To place the device into zero current shutdown mode, the EN pin must be held low.

**SDA** is the I<sup>2</sup>C serial data line. This is a bidirectional line allowing data to be written into and read from the four registers in the driver. Registers RegA/B/C set the LED current in each pair of channels, while RegEn sets the On/Off state independently of each channel.

**SCL** is the I<sup>2</sup>C serial clock input.

**VOUT** is the charge pump output that is connected to the LED anodes. A small 1  $\mu$ F ceramic bypass capacitor is required between the VOUT pin and ground near the device.

**GND** is the ground reference for the charge pump. The pin must be connected to the ground plane on the PCB.

C1+, C1– are connected to each side of the 1  $\mu$ F ceramic bucket capacitor C1.

C2+, C2– are connected to each side of the 1  $\mu$ F ceramic bucket capacitor C2.

**LEDxx** provide the internally regulated current to the six LED cathodes. These pins enter a high–impedance zero–current state whenever the device is placed in shutdown mode. In applications using less than six LEDs, the unused channels should be disabled through the RegEn register.

**TAB** is the exposed pad underneath the package. For best thermal performance, the tab should be soldered to the PCB and connected to the ground plane.

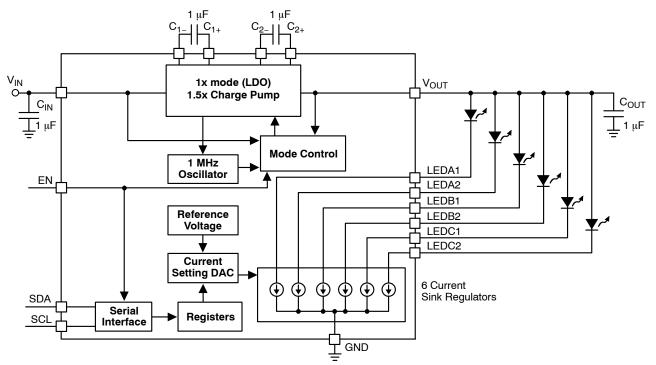

#### **BLOCK DIAGRAM**

Figure 25. CAT3626 Functional Block Diagram

#### **BASIC OPERATION**

At power–up, the CAT3626 starts operating in 1x mode where the output will be approximately equal to the input supply voltage (less any internal voltage losses). If the output voltage is sufficient to regulate all LEDs currents the device remains in 1x operating mode.

If the input voltage is insufficient or falls to a level where the regulated currents cannot be maintained, the device automatically switches (after a fixed time of  $400 \ \mu s$ ) into 1.5 x mode.

In 1.5x mode, the output is approximately equal to 1.5 times the input supply voltage (less any internal voltage losses).

The above sequence is repeated each and every time the chip is either powered-up or taken out of shutdown (via EN pin), or the RegEn register is accessed by write cycle.

#### LED CURRENT SETTING

The LED current setting is programmed via the I<sup>2</sup>C serial interface and is stored in four 8-bit registers RegA, RegB, RegC and RegEn as follows:

- RegA stores the LED current for group A (LEDA1 and LEDA2 channels),

- RegB stores the LED current for group B (LEDB1 and LEDB2 channels),

- RegC stores the LED current for group C (LEDC1 and LEDC2 channels),

- RegEn selects the on/off state of each of the 6 LED channels.

At each write access to RegEn, the driver automatically reconfigures to the mode (1x or 1.5x) that provides the highest efficiency.

| Register | Register<br>Address | Bit Pattern |       |                               |                   |                   |                   |                   |                   |

|----------|---------------------|-------------|-------|-------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Name     |                     | Bit 7       | Bit 6 | Bit 5                         | Bit 4             | Bit 3             | Bit 2             | Bit 1             | Bit 0             |

| RegA     | 0                   | Х           | Х     |                               |                   |                   |                   |                   |                   |

| RegB     | 1                   | Х           | Х     | See Table 7 for values        |                   |                   |                   |                   |                   |

| RegC     | 2                   | Х           | Х     |                               |                   |                   |                   |                   |                   |

|          |                     |             |       | LEDC2 LEDC1 LEDB2 LEDB1 LEDA2 |                   |                   |                   |                   |                   |

| RegEn    | 3                   | 3 X         | Х     | On = 1<br>Off = 0             | On = 1<br>Off = 0 | On = 1<br>Off = 0 | On = 1<br>Off = 0 | On = 1<br>Off = 0 | On = 1<br>Off = 0 |

Table 6. REGISTER ADDRESS AND DATA CONFIGURATION (Note 4)

4. X = not used, 1 = logic high, 0 = logic low

The Table 7 lists the various LED currents with the associated RegA, RegB, and RegC register values.

| LED<br>Current<br>(mA) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Dec |

|------------------------|----|----|----|----|----|----|----|----|-----|

| 0.5                    | х  | х  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

| 1.0                    | Х  | х  | 0  | 0  | 0  | 0  | 0  | 1  | 1   |

| 1.5                    | х  | х  | 0  | 0  | 0  | 0  | 1  | 0  | 2   |

| 2.0                    | х  | х  | 0  | 0  | 0  | 0  | 1  | 1  | 3   |

| 2.5                    | х  | х  | 0  | 0  | 0  | 1  | 0  | 0  | 4   |

| 3.0                    | х  | х  | 0  | 0  | 0  | 1  | 0  | 1  | 5   |

| 3.5                    | х  | х  | 0  | 0  | 0  | 1  | 1  | 0  | 6   |

| 4.0                    | х  | х  | 0  | 0  | 0  | 1  | 1  | 1  | 7   |

| 4.5                    | Х  | Х  | 0  | 0  | 1  | 0  | 0  | 0  | 8   |

| 5.0                    | Х  | Х  | 0  | 0  | 1  | 0  | 0  | 1  | 9   |

| 5.5                    | Х  | Х  | 0  | 0  | 1  | 0  | 1  | 0  | 10  |

| 6.0                    | х  | х  | 0  | 0  | 1  | 0  | 1  | 1  | 11  |

| 6.5                    | х  | х  | 0  | 0  | 1  | 1  | 0  | 0  | 12  |

| 7.0                    | х  | х  | 0  | 0  | 1  | 1  | 0  | 1  | 13  |

| 7.5                    | х  | х  | 0  | 0  | 1  | 1  | 1  | 0  | 14  |

| 8.0                    | х  | х  | 0  | 0  | 1  | 1  | 1  | 1  | 15  |

| 8.5                    | х  | х  | 0  | 1  | 0  | 0  | 0  | 0  | 16  |

| 9.0                    | х  | х  | 0  | 1  | 0  | 0  | 0  | 1  | 17  |

| 9.5                    | х  | х  | 0  | 1  | 0  | 0  | 1  | 0  | 18  |

| 10.0                   | х  | х  | 0  | 1  | 0  | 0  | 1  | 1  | 19  |

| 10.5                   | х  | х  | 0  | 1  | 0  | 1  | 0  | 0  | 20  |

| 11.0                   | х  | х  | 0  | 1  | 0  | 1  | 0  | 1  | 21  |

| 11.5                   | Х  | Х  | 0  | 1  | 0  | 1  | 1  | 0  | 22  |

| 12.0                   | Х  | Х  | 0  | 1  | 0  | 1  | 1  | 1  | 23  |

| 12.5                   | Х  | Х  | 0  | 1  | 1  | 0  | 0  | 0  | 24  |

| 13.0                   | Х  | Х  | 0  | 1  | 1  | 0  | 0  | 1  | 25  |

| 13.5                   | Х  | Х  | 0  | 1  | 1  | 0  | 1  | 0  | 26  |

| 14.0                   | Х  | Х  | 0  | 1  | 1  | 0  | 1  | 1  | 27  |

| 14.5                   | Х  | Х  | 0  | 1  | 1  | 1  | 0  | 0  | 28  |

| 15.0                   | Х  | Х  | 0  | 1  | 1  | 1  | 0  | 1  | 29  |

| 15.5                   | Х  | Х  | 0  | 1  | 1  | 1  | 1  | 0  | 30  |

| 16.0                   | Х  | х  | 0  | 1  | 1  | 1  | 1  | 1  | 31  |

| Table 7. LED CURRENT SELECTION AND REGISTER VALUE (Note | ; 5) |

|---------------------------------------------------------|------|

|---------------------------------------------------------|------|

| LED<br>Current<br>(mA) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Dec |

|------------------------|----|----|----|----|----|----|----|----|-----|

| 16.5                   | х  | Х  | 1  | 0  | 0  | 0  | 0  | 0  | 32  |

| 17.0                   | х  | Х  | 1  | 0  | 0  | 0  | 0  | 1  | 33  |

| 17.5                   | х  | х  | 1  | 0  | 0  | 0  | 1  | 0  | 34  |

| 18.0                   | х  | х  | 1  | 0  | 0  | 0  | 1  | 1  | 35  |

| 18.5                   | х  | х  | 1  | 0  | 0  | 1  | 0  | 0  | 36  |

| 19.0                   | х  | х  | 1  | 0  | 0  | 1  | 0  | 1  | 37  |

| 19.5                   | х  | х  | 1  | 0  | 0  | 1  | 1  | 0  | 38  |

| 20.0                   | х  | х  | 1  | 0  | 0  | 1  | 1  | 1  | 39  |

| 20.5                   | х  | х  | 1  | 0  | 1  | 0  | 0  | 0  | 40  |

| 21.0                   | х  | х  | 1  | 0  | 1  | 0  | 0  | 1  | 41  |

| 21.5                   | х  | х  | 1  | 0  | 1  | 0  | 1  | 0  | 42  |

| 22.0                   | х  | х  | 1  | 0  | 1  | 0  | 1  | 1  | 43  |

| 22.5                   | х  | х  | 1  | 0  | 1  | 1  | 0  | 0  | 44  |

| 23.0                   | х  | х  | 1  | 0  | 1  | 1  | 0  | 1  | 45  |

| 23.5                   | х  | х  | 1  | 0  | 1  | 1  | 1  | 0  | 46  |

| 24.0                   | х  | х  | 1  | 0  | 1  | 1  | 1  | 1  | 47  |

| 24.5                   | х  | х  | 1  | 1  | 0  | 0  | 0  | 0  | 48  |

| 25.0                   | х  | х  | 1  | 1  | 0  | 0  | 0  | 1  | 49  |

| 25.5                   | х  | х  | 1  | 1  | 0  | 0  | 1  | 0  | 50  |

| 26.0                   | х  | х  | 1  | 1  | 0  | 0  | 1  | 1  | 51  |

| 26.5                   | х  | х  | 1  | 1  | 0  | 1  | 0  | 0  | 52  |

| 27.0                   | х  | х  | 1  | 1  | 0  | 1  | 0  | 1  | 53  |

| 27.5                   | х  | х  | 1  | 1  | 0  | 1  | 1  | 0  | 54  |

| 28.0                   | х  | х  | 1  | 1  | 0  | 1  | 1  | 1  | 55  |

| 28.5                   | х  | х  | 1  | 1  | 1  | 0  | 0  | 0  | 56  |

| 29.0                   | х  | х  | 1  | 1  | 1  | 0  | 0  | 1  | 57  |

| 29.5                   | х  | х  | 1  | 1  | 1  | 0  | 1  | 0  | 58  |

| 30.0                   | Х  | Х  | 1  | 1  | 1  | 0  | 1  | 1  | 59  |

| 30.5                   | х  | Х  | 1  | 1  | 1  | 1  | 0  | 0  | 60  |

| 31.0                   | Х  | Х  | 1  | 1  | 1  | 1  | 0  | 1  | 61  |

| 31.5                   | Х  | Х  | 1  | 1  | 1  | 1  | 1  | 0  | 62  |

| 32.0                   | Х  | Х  | 1  | 1  | 1  | 1  | 1  | 1  | 63  |

5. X = not used, 1 = logic high, 0 = logic low

#### I<sup>2</sup>C INTERFACE

The LED driver is interfaced through a 2-wire serial  $I^2C$ -bus in order to control the state and the current in each of the six LED channels. The SDA and SCL lines comply with the  $I^2C$  electrical specification and should be terminated with pull-up resistors. When the bus is not used, both lines are high. The device supports the maximum bus speed of 400 kbit/s. The serial bit sequence is shown below

for read and write operations into the registers. Read and write instructions are initiated by the master controller/CPU and acknowledged by the slave LED driver. The I<sup>2</sup>C address of the driver is internally fixed to the binary value 1100110. The protocol requires that the start bit and the device address are both repeated. For further details on the I<sup>2</sup>C protocol, please refer to the I<sup>2</sup>C–Bus Specification, document number 9398 393 40011, from Philips Semiconductors.

#### • Read operation:

| S       Slave address       W       A       Register address       A       S       Slave address       R       A       Data       A*       P         • Write operation:       S       Slave address       V       A       Register address       A       Data       A       P         S       Slave address       W       A       Register address       A       Data       A       P         S       Slave address       W       A       Register address       A       Data       A       P         S       Slave address       W       A       Register address       A       Data       A       P         S       Slave address       W       A       Register address       D       Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • R6                                                                                                                                                                                              | ead operation: |         |         |                    |         |       |               |        |       |       |       |      |   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|---------|--------------------|---------|-------|---------------|--------|-------|-------|-------|------|---|--|

| S       Size address       W       A       Register address       A       Data       A       P         S:       Start condition       R, W:       Read bit (1), Wite bit (0)       A:       Acknowledge sent by the slave LED driver (SDA high)         A:       Not Acknowledge sent by the master microcontroller (SDA low)       P:       Stop condition         Begister address:       Device address of address of bits       Data       Data         Data       Data       Data       Data       Data         Start       Dot       T       A6 AST Address       Data         Data       Data       Data       Data       Data       Stop         Start       D       T       A6 AST Address       Data       Data       Data       Stop         Start       D       T       O       T       A6 AST Address       Data       D7 D6 D5 D4 D3 D2 D1 D0       Stop         Start       Start       D       T       O       T       O       AST Address       Register Address       Data       D3 D2 D1 D0       Stop         Start       Start       Start       Start Address       Register Address       Register Address       Register Address       Start Address       Register Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S                                                                                                                                                                                                 | Slave address  | W       | Α       | Register address   | А       | S     | Slave address |        | R     | А     | Data  | A*   | Р |  |

| S       Size address       W       A       Register address       A       Data       A       P         S:       Start condition       R, W:       Read bit (1), Write bit (0)       A:       Acknowledge sent by the slave LED driver (SDA high)       A:       Not Acknowledge sent by the slave LED driver (SDA high)         M:       Read bit (1), Write bit (0)       A:       Acknowledge sent by the master microcontroller (SDA low)         P:       Stop condition       P:       Stop condition         Register address:       Device address of address is 1100110).       Register address is 100110).       Register address is 1100110.         Register address:       Device address address is 1100110.       Register address is 1100100.       Data       Data         START       START       Diat is 0 0 1 1 0 0       AT #6 A5 A4 #A3 #A2 #A1 #A0       D7 D6 D5 D4 103 D2 D1 D0       STOP         START       START       Stave Address       W       Register Address = RegB = 1       Data = 39 (20mA)         1 1 0 0 1 1 0 0       AT #6 A5 #A #A3 #A2 #A1 #A0       D7 D6 D5 D4 103 D2 D1 D0       START         START       Stare       Address       Register Address = RegB = 1       Data = 39 (20mA)         1 1 0 0 1 1 0 0       AT #6 A5 #A #A3 #A2 #A1 #A0       D7 D6 D5 D4 103 D2 D1 D0         START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| Size Address W Register Address Data<br>Size Address W Register Address Data Data Size LED and LEDB2<br>Start<br>Start 0 0 1 1 0 0 ACK 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                   | -              |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | S                                                                                                                                                                                                 |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R, W: Read bit (1), Write bit (0)                                                                                                                                                                 |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| Slave Address: Device address 2 bits (MSB first, slave address is 1100110).<br>Register address: Device register address 8 bits<br>Data to read or write 8 bits<br>Slave Address W Register Address Data<br>1 1 0 0 1 1 0 0 Ack (N27) (A5) (A5) (A1) (A3) (A2) (A1) (A3) (A2) (A1) (A3) (A2) (A1) (A3) (A2) (D7) (D5) (D4) (D3) (D2) (D1) (D3) (A2) (A3) (A2) (A1) (A3) (A2) (D1) (D3) (D2) (D1) (D3) (D3) (D2) (D1) (D3) (D2) (D1) (D3) (D2) (D1) (D3) (D2) (D1) (D3) (D1) (D1) (D1) (D1) (D1) (D1) (D1) (D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A*: Not Acknowledge sent by the master microcontroller (SDA low)                                                                                                                                  |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| Data: Data to read or write 8 bits<br>$\frac{1}{10001100} = \frac{1}{1000} + $                                                              |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| $\frac{1}{10001100} = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 10000 = 1000 = 10000 = 1000 = 1000 = 1000 = 1000 = 1000 = 1000 = 10$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Register address: Device register address 8 bits                                                                                                                                                  |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| $\frac{1}{10001100} = \frac{1}{1000} =$                                                  | Slave Address W Register Address Data                                                                                                                                                             |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| sbal       1       0       1       0       Ack(ATX AB) ASX AAX A3X A2X ATX ABX ACK (DTX CB) (DTX C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1     1     0     0     1     1     0     0       A7     A6     A5     A4     A3     A2     A1     A0     D7     D6     D5     D4     D3     D2     D1     D0                                     |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| Figure 26. Write Instruction Sequence<br>I = I = I = I = I = I = I = I = I = I =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| $\frac{Slave Address}{1 1 0 0 1 1 1 0 0} W \frac{Register Address = RegB = 1}{AT A6 A5 A4 A3 A2 A1 A0} DT D6 D5 D4 03 D2 D1 D0$ $\frac{START}{SDA 1 1 0 0 1 1 0 0 ACK 0 0 0 0 0 0 0 ACK X 1 0 0 1 1 ACK 0 STOP}$ $Scl_{23}A_{5}G_{6}G_{7}B_{1}B_{1}G_{1}G_{2}G_{1}G_{1}G_{1}G_{1}G_{1}G_{1}G_{1}G_{1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| $\frac{1}{1001100}$ $\frac{1}{100}$ | Figure 26. Write Instruction Sequence                                                                                                                                                             |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| $\frac{1}{1001100}$ $\frac{1}{100}$ |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| START $SDA = 1 + 0 + 0 + 0 + 0 + 0 + 0 + 0 + 0 + 0 +$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Slave Address W Register Address = RegB = 1 Data = 39 (20mA)                                                                                                                                      |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| SDA 1 1 0 0 1 1 0 0 ACK 0 0 0 0 0 0 0 0 0 1 ACK $\times \times 1$ 0 0 1 1 1 ACK SCL 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1       1       0       1       1       0       0       A7       A6       A5       A4       A3       A2       A1       A0       D7       D6       D5       D4       D3       D2       D1       D0 |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| Figure 27. Write Instruction Example Setting 20 mA Current in LEDB1 and LEDB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| SDA<br>SDA<br>SDA<br>SCL<br>SCL<br>START<br>Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| SCL 1-7 8 9 1-7 8 9 1-7 8 9 1-7 8 9 1-7 A 8 9 1-7 A 8 9 1-7 A 8 9 1-7 A 8 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                   | Figure         | e 27. V | Vrite I | nstruction Example | e Setti | ng 20 | mA Cu         | ırrent | in LE | DB1 a | and L | EDB2 |   |  |

| SCL 1-7 8 9 1-7 8 9 1-7 8 9 1-7 8 9 1-7 A 8 9 1-7 A 8 9 1-7 A 8 9 1-7 A 8 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                   |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |

| SCL C C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SDA                                                                                                                                                                                               |                |         |         |                    |         |       |               |        |       |       |       |      |   |  |