# IntelliMAX<sup>™</sup> Dual-Input Single-Output Advanced Power Switch with True Reverse-Current Blocking

## FPF1320, FPF1321

#### **Description**

The FPF1320/21 is a Dual-Input Single-Output (DISO) load switch consisting of two sets of slew-rate controlled, low on-resistance, P-channel MOSFET switches and integrated analog features. The slew-rate-controlled turn-on characteristic prevents inrush current and the resulting excessive voltage droop on the power rails. The input voltage range operates from 1.5 V to 5.5 V to align with the requirements of low-voltage portable device power rails. FPF1320/21 performs seamless power-source transitions between two input power rails using the SEL pin with advanced break-before-make operation.

FPF1320/21 has a TRCB function to block unwanted reverse current from output to input during ON/OFF states. The switch is controlled by logic inputs of the SEL and EN pins, which are capable of interfacing directly with low-voltage control signals (GPIO).

FPF1321 has 65  $\Omega$  on–chip load resistor for output quick discharge when EN is LOW.

FPF1320/21 is available in 1.0 mm x 1.5 mm WLCSP, 6-bump, with 0.5 mm pitch. FPF1321B is available in 1.0 mm x 1.5 mm WLCSP, 6-bump, 0.5 mm pitch with backside laminate.

#### **Features**

- DISO Load Switches

- Input Supply Operating Range: 1.5 V ~ 5.5 V

- $R_{ON}$  50 m $\Omega$  at  $V_{IN}$  = 3.3 V Per Channel (Typical)

- True Reverse Current Blocking (TRCB)

- Fixed Slew Rate Controlled 130  $\mu$ s for < 1  $\mu$ F C<sub>OUT</sub>

- I<sub>SW</sub>: 1.5 A Per Channel (Maximum)

- Quick Discharge Feature on FPF1321

- Logic CMOS IO Meets JESD76 Standard for GPIO Interface and Related Power Supply Requirements

- ESD Protected:

- ♦ Human Body Model: > 6 kV

- ◆ Charged Device Model: > 1.5 kV

- IEC 61000-4-2 Air Discharge: > 15 kV

- ◆ IEC 61000-4-2 Contact Discharge: > 8 kV

- These are Pb-Free and Halide Free Devices

#### **Applications**

- Smart Phones / Tablet PCs

- Portable Devices

- Near Field Communication (NFC) Capable SIM Card Power Supply

#### ON Semiconductor®

www.onsemi.com

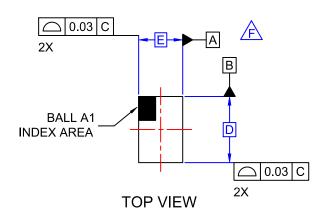

WLCSP-6 CASE 567RM

#### **MARKING DIAGRAM**

Qx&K &.&2&Z

Qx = Specific Device Code

x = S or T

&K = Traceability Code

&. = Pin one dot &2 = Date Code

&Z = Assembly plant code

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 12 of this data sheet.

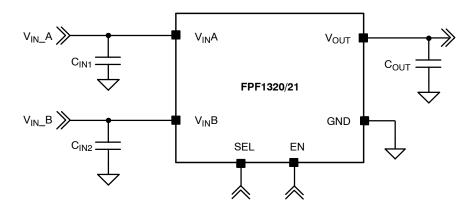

#### **APPLICATION DIAGRAM**

Figure 1. Typical Application

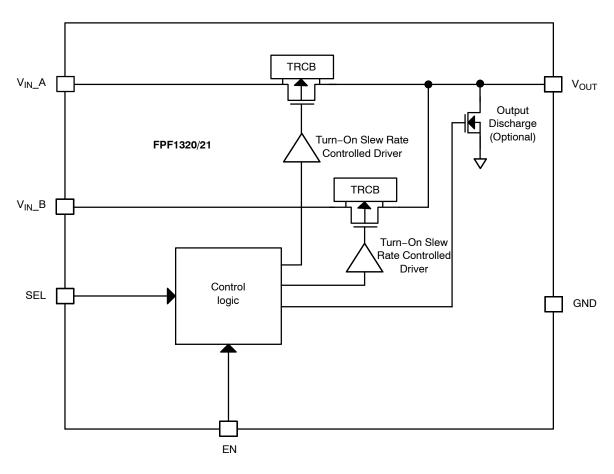

#### **BLOCK DIAGRAM**

Figure 2. Functional Block Diagram (Output Discharge Path for FPF1321 Only)

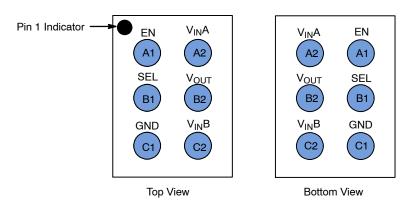

#### **PIN CONFIGURATION**

Figure 3. Pin Assignments

#### **PIN DESCRIPTION**

| Pin# | Name              | Description                                                                                            |

|------|-------------------|--------------------------------------------------------------------------------------------------------|

| A1   | EN                | Enable input. Active HIGH. There is an internal pull-down resistor at the EN pin.                      |

| B1   | SEL               | Input power selection inputs. See Truth Table. There are internal pull-down resistors at the SEL pins. |

| A2   | V <sub>IN</sub> A | Supply Input. Input to the power switch A.                                                             |

| B2   | V <sub>OUT</sub>  | Switch output                                                                                          |

| C1   | GND               | Ground                                                                                                 |

| C2   | V <sub>IN</sub> B | Supply Input. Input to power switch B.                                                                 |

#### **TRUTH TABLE**

| SEL  | EN   | Switch A | Switch B | V <sub>OUT</sub>                        | Status                     |

|------|------|----------|----------|-----------------------------------------|----------------------------|

| Low  | High | ON       | OFF      | V <sub>IN</sub> A                       | V <sub>IN</sub> A Selected |

| High | High | OFF      | ON       | V <sub>IN</sub> B                       | V <sub>IN</sub> B Selected |

| Х    | Low  | OFF      | OFF      | Floating for FPF1320<br>GND for FPF1321 | Both Switches are OFF      |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Pa                                                                                                | Min                                                                                        | Max         | Unit         |    |

|------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|--------------|----|

| V <sub>IN</sub>  | V <sub>IN</sub> A, V <sub>IN</sub> B, V <sub>SEL</sub> , V <sub>EN</sub> , V <sub>OUT</sub> to GN | -0.3                                                                                       | 6           | V            |    |

| I <sub>SW</sub>  | Maximum Continuous Switch Curre                                                                   | Maximum Continuous Switch Current per Channel                                              |             |              | Α  |

| P <sub>D</sub>   | Total Power Dissipation at T <sub>A</sub> = 25°0                                                  | С                                                                                          | -           | 1.2          | W  |

| T <sub>STG</sub> | Operating and Storage Junction Ter                                                                | -65                                                                                        | 150         | °C           |    |

| $\Theta_{JA}$    | Thermal Resistance, Junction-to-A                                                                 | -                                                                                          | 85 (Note 1) | °C/W         |    |

|                  | (1 in. <sup>2</sup> Pad of 2–oz. Copper)                                                          |                                                                                            | -           | 110 (Note 2) |    |

| ESD              | Electrostatic Discharge Capability                                                                | Human Body Model, JESD22-A114                                                              | 6.0         | -            | kV |

|                  |                                                                                                   | Charged Device Model, JESD22-C101                                                          | 1.5         | -            |    |

|                  |                                                                                                   | Air Discharge (V <sub>IN</sub> A, V <sub>IN</sub> B to GND),<br>IEC61000-4-2 System Level  | 15.0        | -            |    |

|                  |                                                                                                   | Contact Discharge (V <sub>IN</sub> A, V <sub>IN</sub> B to GND), IEC61000-4-2 System Level | 8.0         | -            |    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Measured using 2S2P JEDEC std. PCB.

- 2. Measured using 2S2P JEDEC PCB cold-plate method.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameters                                            | Min | Max | Unit |

|-----------------|-------------------------------------------------------|-----|-----|------|

| V <sub>IN</sub> | Input Voltage on V <sub>IN</sub> A, V <sub>IN</sub> B | 1.5 | 5.5 | ٧    |

| T <sub>A</sub>  | Ambient Operating Temperature                         | -40 | 85  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ELECTRICAL CHARACTERISTICS** $V_{IN}A = V_{IN}B = 1.5$ to 5.5 V, $T_A = -40$ to 85°C unless otherwise noted. Typical values are at $V_{IN}A = V_{IN}B = 3.3$ V, $T_A = 25$ °C

| Symbol                            | Parameter                                                                                                 | Test Conditions                                                                                                                                                             | Min  | Тур | Max  | Unit |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|--|--|--|

| BASIC OPERATION                   |                                                                                                           |                                                                                                                                                                             |      |     |      |      |  |  |  |

| $V_{IN}A, V_{IN}B$                | Input Voltage                                                                                             | 1.5                                                                                                                                                                         | -    | 5.5 | V    |      |  |  |  |

| I <sub>SD</sub>                   | Shutdown Current                                                                                          | SEL = HIGH or LOW, EN = GND,<br>$V_{OUT}$ = GND, $V_{IN}$ A = $V_{IN}$ B = 5.5 V                                                                                            | -    | _   | 5    | μΑ   |  |  |  |

| ΙQ                                | Quiescent Current                                                                                         | $I_{OUT}$ = 0 mA, SEL = HIGH or<br>LOW, EN = HIGH,<br>$V_{IN}A$ = $V_{IN}B$ = 5.5 V                                                                                         | -    | 12  | 22   | μΑ   |  |  |  |

|                                   | On-Resistance                                                                                             | V <sub>IN</sub> A = V <sub>IN</sub> B = 5.5 V,<br>I <sub>OUT</sub> = 200 mA, T <sub>A</sub> = 25°C                                                                          | -    | 42  | 60   | mΩ   |  |  |  |

| R <sub>ON</sub>                   |                                                                                                           | $V_{IN}A = V_{IN}B = 3.3 \text{ V},$<br>$I_{OUT} = 200 \text{ mA}, T_A = 25^{\circ}\text{C}$                                                                                | _    | 50  | -    |      |  |  |  |

|                                   |                                                                                                           | $V_{IN}A = V_{IN}B = 1.8 \text{ V},$<br>$I_{OUT} = 200 \text{ mA}, T_A = 25^{\circ}\text{C to } 85^{\circ}\text{C}$                                                         | -    | 80  | -    |      |  |  |  |

|                                   |                                                                                                           | $V_{IN}A = V_{IN}B = 1.5 \text{ V},$<br>$I_{OUT} = 200 \text{ mA}, T_A = 25^{\circ}\text{C}$                                                                                | _    | _   | 170  |      |  |  |  |

| V <sub>IH</sub>                   | SEL, EN Input Logic High Voltage                                                                          | V <sub>IN</sub> A, V <sub>IN</sub> B = 1.5 V – 5.5 V                                                                                                                        | 1.15 | -   | -    | V    |  |  |  |

| $V_{IL}$                          | SEL, EN Input Logic Low Voltage                                                                           | $V_{IN}A$ , $V_{IN}B = 1.8 V - 5.5 V$                                                                                                                                       | -    | -   | 0.65 | V    |  |  |  |

|                                   | SEL, EN Input Logic Low Voltage                                                                           | V <sub>IN</sub> A, V <sub>IN</sub> B = 1.5 V – 1.8 V                                                                                                                        | -    | -   | 0.60 |      |  |  |  |

| V <sub>DROOP</sub> _OUT           | Output Voltage Droop while Channel<br>Switching from Higher Input Voltage<br>Lower Input Voltage (Note 3) | $\begin{split} &V_{IN}A=3.3 \text{ V, } V_{IN}B=5 \text{ V,} \\ &\text{Switching from } V_{IN}A \rightarrow V_{IN}B, \\ &R_L=150 \Omega, C_{OUT}=1 \mu\text{F} \end{split}$ | -    | -   | 100  | mV   |  |  |  |

| I <sub>SEL</sub> /I <sub>EN</sub> | Input Leakage at SEL and EN Pin                                                                           | -                                                                                                                                                                           | -    | _   | 1.2  | μΑ   |  |  |  |

**ELECTRICAL CHARACTERISTICS**  $V_{IN}A = V_{IN}B = 1.5$  to 5.5 V,  $T_A = -40$  to 85°C unless otherwise noted. Typical values are at  $V_{IN}A = V_{IN}B = 3.3$  V,  $T_A = 25$ °C (continued)

| Symbol                                      | Parameter                                                 | Test Conditions                                                                                                             | Min | Тур | Max | Unit |

|---------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| BASIC OPERA                                 | ATION (continued)                                         |                                                                                                                             |     |     |     |      |

| R <sub>SEL_PD</sub> /<br>R <sub>EN_PD</sub> | Pull-Down Resistance at SEL or EN Pin                     | -                                                                                                                           | -   | 7   | _   | МΩ   |

| R <sub>PD</sub>                             | Output Pull-Down Resistance                               | SEL = HIGH or LOW, EN = GND, $I_{FORCE}$ = 20 mA, $T_A$ = 25°C, FPF1321                                                     | -   | 65  | -   | Ω    |

| TRUE REVERS                                 | SE CURRENT BLOCKING                                       |                                                                                                                             |     |     |     |      |

| V <sub>T_RCB</sub>                          | RCB Protection Trip Point                                 | V <sub>OUT</sub> – V <sub>IN</sub> A or V <sub>IN</sub> B                                                                   | -   | 45  | -   | mV   |

| V <sub>R_RCB</sub>                          | RCB Protection Release Trip Point                         | V <sub>IN</sub> A or V <sub>IN</sub> B –V <sub>OUT</sub>                                                                    | -   | 25  | -   | mV   |

| I <sub>RCB</sub>                            | V <sub>IN</sub> A or V <sub>IN</sub> B Current During RCB | V <sub>OUT</sub> = 5.5 V,<br>V <sub>IN</sub> A or V <sub>IN</sub> B = Short to GND                                          | -   | 9   | 15  | μΑ   |

| t <sub>RCB_ON</sub>                         | RCB Response Time w hen Device is ON (Note 3)             | $V_{IN}A$ or $V_{IN}B = 5$ V,<br>$V_{OUT}V_{IN}A,B = 100$ mV                                                                | _   | 5   | -   | μs   |

| DYNAMIC CHA                                 | ARACTERISTICS                                             |                                                                                                                             |     |     |     |      |

| t <sub>DON</sub>                            | Turn-On Delay (Note 4)                                    | $V_{IN}A$ or $V_{IN}B = 3.3 \text{ V}$ , $R_L = 150 \Omega$ ,                                                               | -   | 120 | _   | μs   |

| t <sub>R</sub>                              | V <sub>OUT</sub> Rise Time (Note 4)                       | C <sub>L</sub> = 1 $\mu$ F, T <sub>A</sub> = 25°C, SEL: HIGH,<br>EN: LOW $\rightarrow$ HIGH                                 | -   | 130 | _   |      |

| t <sub>ON</sub>                             | Turn-On Time (Note 6)                                     |                                                                                                                             | -   | 250 | _   |      |

| t <sub>DOFF</sub>                           | Turn-Off Delay (Note 4)                                   | $V_{IN}A$ or $V_{IN}B = 3.3 \text{ V}$ , $R_L = 150 \Omega$ ,                                                               | -   | 15  | _   | μs   |

| t <sub>F</sub>                              | V <sub>OUT</sub> Fall Time (Note 4)                       | C <sub>L</sub> = 1 $\mu$ F, T <sub>A</sub> = 25°C, SEL: HIGH,<br>EN: HIGH $\rightarrow$ LOW                                 | -   | 320 | _   |      |

| t <sub>OFF</sub>                            | Turn-Off Time (Note 7)                                    |                                                                                                                             | -   | 335 | _   |      |

| t <sub>DOFF</sub>                           | Turn-Off Delay (Note 4, Note 5)                           | $V_{IN}A$ or $V_{IN}B = 3.3 \text{ V}$ , $R_L = 150 \Omega$ ,                                                               | -   | 6   | _   | μs   |

| t <sub>F</sub>                              | V <sub>OUT</sub> Fall Time (Note 4, Note 5)               | C <sub>L</sub> = 1 $\mu$ F, T <sub>A</sub> = 25°C, SEL: HIGH,<br>EN: HIGH $\rightarrow$ LOW,                                | -   | 110 | _   |      |

| t <sub>OFF</sub>                            | Turn-Off Time (Note 5, Note 7)                            | Output Discharge Mode, FPF1321                                                                                              | -   | 116 | -   |      |

| t <sub>TRANR</sub>                          | Transition Time LOW → HIGH (Note 4)                       | $V_{IN}A = 3.3 \text{ V}, V_{IN}B = 5 \text{ V},$<br>Switching from $V_{IN}A \rightarrow V_{IN}B$ ,                         | -   | 3   | _   | μs   |

| t <sub>SLH</sub>                            | Switch-Over Rising Delay (Note 4)                         | SEL: LOW $\rightarrow$ HIGH, EN: HIGH,<br>R <sub>L</sub> = 150 $\Omega$ , C <sub>L</sub> = 1 $\mu$ F, T <sub>A</sub> = 25°C | _   | 1   | _   |      |

| t <sub>TRANF</sub>                          | Transition Time HIGH $\rightarrow$ LOW (Note 4)           | $V_{IN}A = 3.3 \text{ V}, V_{IN}B = 5 \text{ V},$<br>Switching from $V_{IN}B \rightarrow V_{IN}A$ ,                         | -   | 45  | _   | μs   |

| t <sub>SHL</sub>                            | Switch-Over Falling Delay (Note 4)                        | SEL: HIĞH $\rightarrow$ LÖW, EN: HIĞH,<br>R <sub>L</sub> = 150 $\Omega$ , C = 1 $\mu$ F, T <sub>A</sub> = 25°C              | -   | 5   | _   |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>3.</sup> This parameter is guaranteed by design and characterization; not production tested.

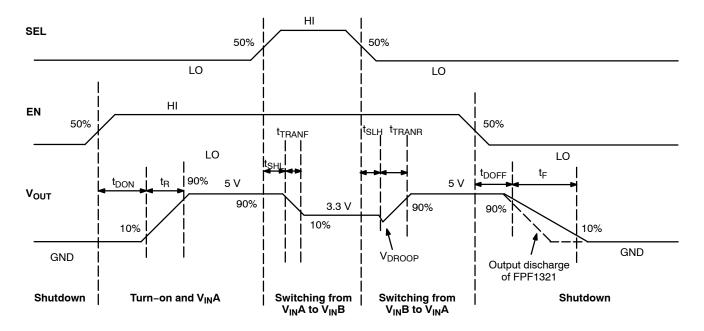

4. t<sub>DON</sub>/t<sub>DOFF</sub>/t<sub>R</sub>/t<sub>F</sub>/t<sub>TRANR</sub>/t<sub>TRANF</sub>/t<sub>SLH</sub>/t<sub>SHL</sub> are defined in Figure 4.

5. FPF1321 output discharge is enabled during off.

<sup>6.</sup> t<sub>ON</sub> = t<sub>R</sub> + t<sub>DON</sub> 7. t<sub>OFF</sub> = t<sub>F</sub> + t<sub>DOFF</sub>

#### **TIMING DIAGRAM**

| V <sub>IN</sub> A | 5 V   |

|-------------------|-------|

|                   |       |

| V <sub>IN</sub> B | 3.3 V |

Figure 4. Dynamic Behavior Timing Diagram

#### **TYPICAL CHARACTERISTICS**

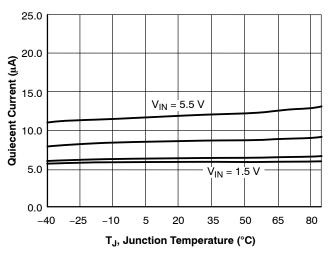

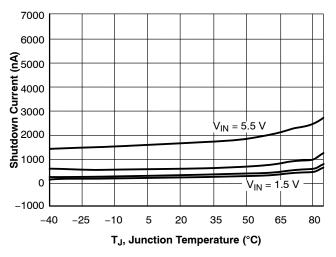

Figure 5. Supply Current vs. Temperature

Figure 6. Supply Current vs. Supply Voltage

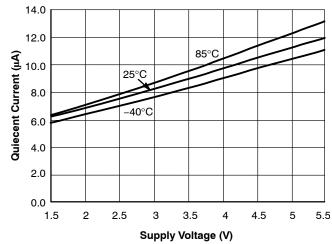

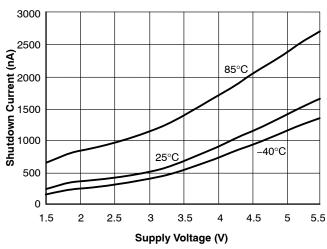

Figure 7. Shutdown Current vs. Temperature

Figure 8. Shutdown Current vs. Supply Voltage

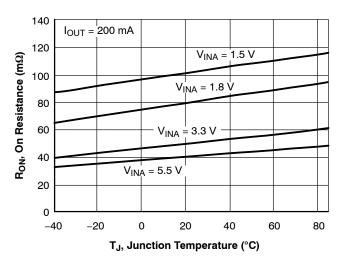

Figure 9. R<sub>ON</sub> vs. Temperature

Figure 10.  $R_{ON}$  vs. Supply Voltage

#### TYPICAL CHARACTERISTICS (continued)

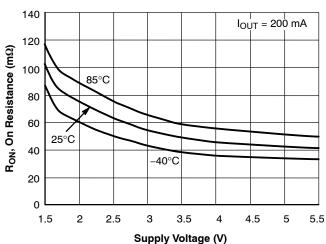

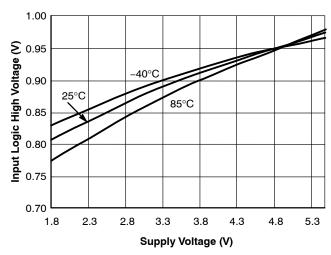

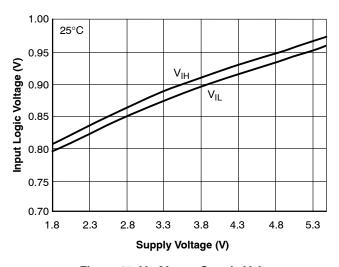

Figure 11. V<sub>IL</sub> vs. Temperature

Figure 12. V<sub>IL</sub> vs. Supply Voltage

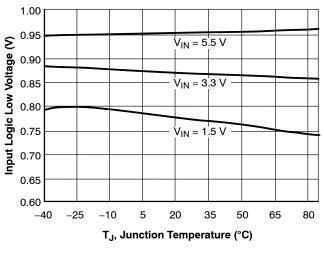

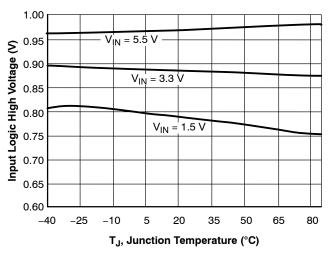

Figure 13.  $V_{IH}$  vs. Temperature

Figure 14. V<sub>IH</sub> vs. Supply Voltage

Figure 15.  $V_{IH}/V_{IL}$  vs. Supply Voltage

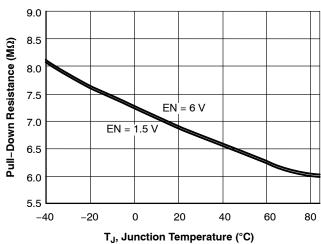

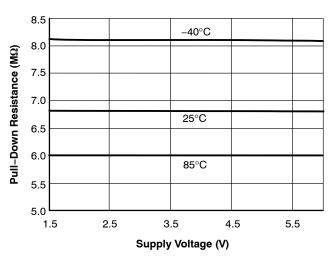

Figure 16.  $R_{\mbox{\footnotesize SEL\_PD}}$  and  $R_{\mbox{\footnotesize EN\_PD}}$  vs. Temperature

#### TYPICAL CHARACTERISTICS (continued)

179  $V_{IN} = 3.3 \text{ V}$  $C_L = 1 \mu F$   $R_L = 150 \Omega$ 159 139 On/Off Delay Time (μs) t<sub>DON</sub> 119 99 79 59 39 t<sub>DOFF</sub> 19 -40 -15 60 85 T<sub>J</sub>, Junction Temperature (°C)

Figure 17.  $R_{SEL\ PD}$  and  $R_{EN\ PD}$  vs. Supply Voltage

Figure 18.  $t_{DON}$  and  $t_{DOFF}$  vs. Temperature

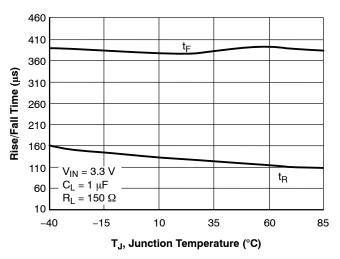

Figure 19.  $t_R$  and  $t_F$  with FPF1320 vs. Temperature

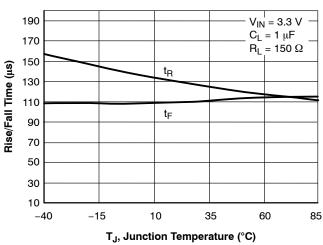

Figure 20. t<sub>R</sub> and t<sub>F</sub> with FPF1321 vs. Temperature

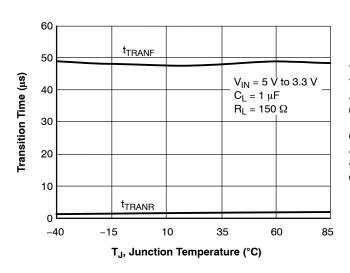

Figure 21. Transition Time vs. Temperature

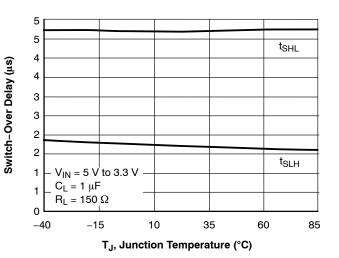

Figure 22. Switch Over Time vs. Temperature

#### TYPICAL CHARACTERISTICS (continued)

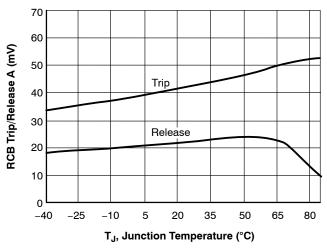

Figure 23. TRCB Trip and Release vs. Temperature

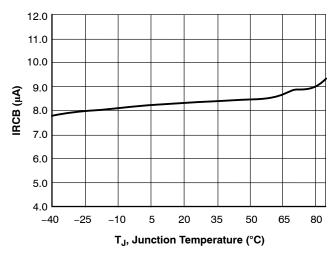

Figure 24. I<sub>RCB</sub> vs. Temperature

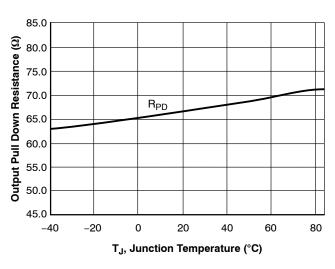

Figure 25. R<sub>PD</sub> with FPF1321 vs. Temperature

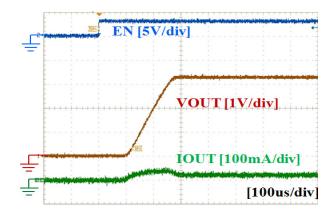

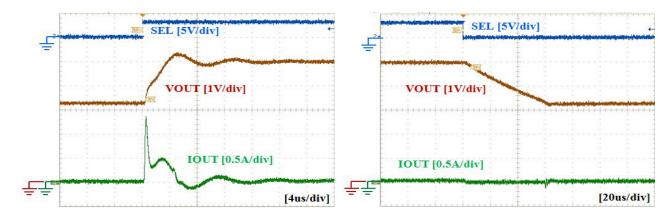

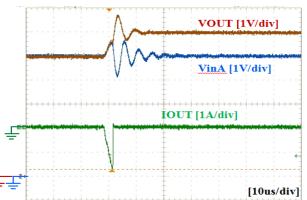

Figure 26. Turn–On Response (V<sub>IN</sub>A = 3.3 V, C<sub>IN</sub> = 1  $\mu$ F, C<sub>OUT</sub> = 1  $\mu$ F, R<sub>L</sub> = 150  $\Omega$ , SEL = LOW)

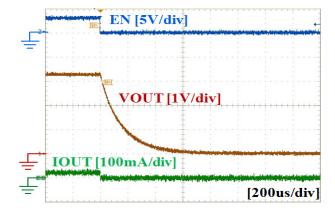

Figure 27. Turn–Off Response with FPF1320 (V<sub>IN</sub>A = 3.3 V, C<sub>IN</sub> = 1  $\mu$ F, C<sub>OUT</sub> = 1  $\mu$ F, R<sub>L</sub> = 150  $\Omega$ , SEL = LOW)

Figure 28. Turn–Off Response with FPF1321 (V<sub>IN</sub>A = 3.3 V, C<sub>IN</sub> = 1  $\mu$ F, C<sub>OUT</sub> = 1  $\mu$ F, R<sub>L</sub> = 150  $\Omega$ , SEL = LOW)

#### TYPICAL CHARACTERISTICS (continued)

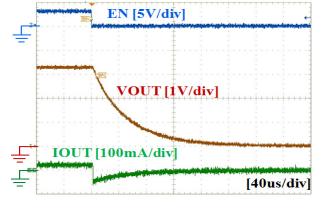

Figure 29. Power Source Transition from 3.3 V to 5 V (V<sub>IN</sub>A = 3.3 V, V<sub>IN</sub>B = 5 V, C<sub>IN</sub> = 1  $\mu$ F, C<sub>OUT</sub> = 1  $\mu$ F, R<sub>L</sub> = 150  $\Omega$ )

Figure 30. Power Source Transition from 5 V to 3.3 V (V<sub>IN</sub>A = 3.3 V, V<sub>IN</sub>B = 5 V, C<sub>IN</sub> = 1  $\mu$ F, C<sub>OUT</sub> = 1  $\mu$ F, R<sub>L</sub> = 150  $\Omega$ )

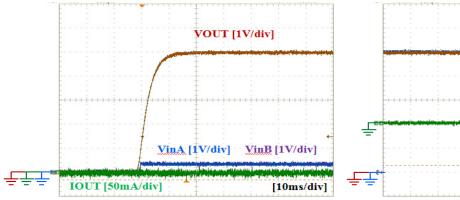

$Figure~31.~TRCB~During~Off\\ (V_{IN}A=V_{IN}B=Floating,~V_{OUT}=5~V,~C_{IN}=1~\mu F,\\ C_{OUT}=1~\mu F,~EN=LOW,~No~R_L)$

Figure 32. TRCB During On (V<sub>IN</sub>A = 5 V, V<sub>OUT</sub> = 6 V, C<sub>IN</sub> = 1  $\mu$ F, C<sub>OUT</sub> = 1  $\mu$ F, EN = HIGH, No R<sub>I</sub> )

#### **OPERATION AND APPLICATION DESCRIPTION**

The FPF1320 and FPF1321 are dual–input single–output power multiplexer switches with controlled turn–on and seamless power source transition. The core is a 50 m $\Omega$  P–channel MOSFET and controller capable of functioning over a wide input operating range of 1.5 V to 5.5 V per channel. The EN and SEL pins are active–HIGH, GPIO/CMOS–compatible input. They control the state of the switch and input power source selection, respectively. TRCB functionality blocks unwanted reverse current during both ON and OFF states when higher  $V_{OUT}$  than  $V_{IN}A$  or  $V_{IN}B$  is applied. FPF1321 has a 65  $\Omega$  output discharge path during off.

#### **Input Capacitor**

To limit the voltage drop on the input supply caused by transient inrush current when the switch turns on into a discharged load capacitor; a capacitor must be placed between the  $V_{IN}A$  or  $V_{IN}B$  pins to the GND pin. At least 1  $\mu F$  ceramic capacitor,  $C_{IN}$ , placed close to the pins, is usually sufficient. Higher–value  $C_{IN}$  can be used to reduce more the voltage drop.

#### **Inrush Current**

Inrush current occurs when the device is turned on. Inrush current is dependent on output capacitance and slew rate control capability, as expressed by:

$$I_{INRUSH} = C_{OUT} \times \frac{V_{IN} - V_{INITIAL}}{t_{R}} + I_{LOAD}$$

(eq. 1)

where:

C<sub>OUT</sub>: Output capacitance;

t<sub>R</sub>: Slew rate or rise time at V<sub>OUT</sub>; V<sub>IN</sub>: Input voltage, V<sub>IN</sub>A or V<sub>IN</sub>B;

V<sub>INITIAL</sub>: Initial voltage at C<sub>OUT</sub>, usually GND; and

I<sub>LOAD</sub>: Load current.

Higher inrush current causes higher input voltage drop, depending on the distributed input resistance and input capacitance. High inrush current can cause problems.

FPF1320/1 has a 130  $\mu s$  of slew rate capability under 3.3  $V_{IN}$  at 1  $\mu F$  of  $C_{OUT}$  and 150  $\Omega$  of  $R_L$  so inrush current and input voltage drop can be minimized.

#### **Power Source Selection**

Input power source selection can be controlled by the SEL pin. When SEL is LOW, output is powered from  $V_{IN}A$  while SEL is HIGH,  $V_{IN}B$  is powering output. The SEL signal is ignored during device OFF.

#### **Output Voltage Drop During Transition**

Output voltage drop usually occurs during input power source transition period from low voltage to high voltage. The drop is highly dependent on output capacitance and load current.

FPF1320/1 adopts an advanced break-before-make control, which can result in minimized output voltage drop during the transition time.

#### **Output Capacitor**

Capacitor  $C_{OUT}$  of at least 1  $\mu F$  is highly recommended between the  $V_{OUT}$  and GND pins to achieve minimized output voltage drop during input power source transition. This capacitor also prevents parasitic board inductance.

#### True Reverse-Current Blocking

The true reverse-current blocking feature protects the input source against current flow from output to input regardless of whether the load switch is on or off.

#### **Board Layout**

For best performance, all traces should be as short as possible. To be most effective, the input and output capacitors should be placed close to the device to minimize the effect that parasitic trace inductance on normal and short–circuit operation. Wide traces or large copper planes for power pins ( $V_{IN}A$ ,  $V_{IN}B$ ,  $V_{OUT}$  and GND) minimize the parasitic electrical effects and the thermal impedance.

#### **ORDERING INFORMATION**

| Part Number | Top<br>Mark | Channel | Switch Per<br>Channel (Typ.)<br>at 3.3 V <sub>IN</sub> | Reverse<br>Current<br>Blocking | Output<br>Discharge | Rise Time<br>(t <sub>R</sub> ) | Package                                                                                                         |

|-------------|-------------|---------|--------------------------------------------------------|--------------------------------|---------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------|

| FPF1320UCX  | QS          | DISO    | 50 mΩ                                                  | Yes                            | NA                  | 130 μs                         | 1.0 mm × 1.5 mm<br>Wafer-Level Chip-Scale                                                                       |

| FPF1321UCX  | QT          | DISO    | 50 mΩ                                                  | Yes                            | 65 Ω                | 130 μs                         | Package (WLCSP)<br>6-Bumps, 0.5 mm Pitch                                                                        |

| FPF1321BUCX | QT          | DISO    | 50 mΩ                                                  | Yes                            | 65 Ω                | 130 μs                         | 1.0 mm × 1.5 mm<br>Wafer-Level Chip-Scale<br>Package (WLCSP)<br>6-Bumps, 0.5 mm Pitch<br>with Backside Laminate |

#### PRODUCT-SPECIFIC DIMENSIONS

| Product     | D              | E             | Х      | Υ      |

|-------------|----------------|---------------|--------|--------|

| FPF1320UCX  | 1460 μm ±30 μm | 960 μm ±30 μm | 230 μm | 230 μm |

| FPF1321UCX  | 1460 μm ±30 μm | 960 μm ±30 μm | 230 μm | 230 μm |

| FPF1321BUCX | 1460 μm ±30 μm | 960 μm ±30 μm | 230 μm | 230 μm |

IntelliMAX is a trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

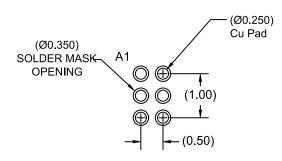

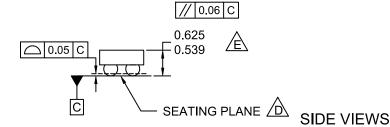

#### WLCSP6 1.46x0.96x0.582 CASE 567RM ISSUE O

**DATE 30 NOV 2016**

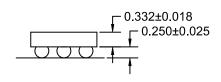

RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

# Ø0.005(W) C A B Ø0.315 +/- .025 6X C 1.00 0.50 B (Y) ±0.018 BOTTOM VIEW

#### NOTES:

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER ASMEY14.5M, 1994.

DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

PACKAGE NOMINAL HEIGHT IS 582 MICRONS ±43 MICRONS (539-625 MICRONS).

FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

| DOCUMENT NUMBER: | 98AON16579G            | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | WLCSP6 1.46x0.96x0.582 |                                                                                                                                                                               | PAGE 1 OF 1 |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales