# **Optical Image Stabilization** (OIS) Controller & Driver

# **CMOS LSI**

# LC898121XA

#### Overview

The LC898121XA is a system LSI integrating a digital signal processing function for Optical Image Stabilization (OIS) and a saturation–driven H bridge driver function.

#### Features

Digital Signal Processing

- Built-in Digital Servo Circuit

- Built-in Gyro Filter

- AD Converter

- 12 Bit

- Input 3ch

- Equipped with a Sample-hold Circuit

- DA Converter

- 8 Bit

- Output 2ch

- Built–in Serial I/F Circuit (4–wire SPI or 2–wire I<sup>2</sup>C–Bus Interface)

- Built-in Hall Bias Circuit

- Built-in Hall Amp

- Built-in OSC (Oscillator)

- Typ. 48 MHz

- Built-in LDO (Low Drop-Out Regulator)

Generation Logic Power (Typ 1.8 V)

- Digital Gyro I/F for the Companies (Please Refer for the Details)

#### Motor Driver

- Saturation–drive H Bridge x2ch

- I<sub>O</sub> max: 300 mA

#### Package

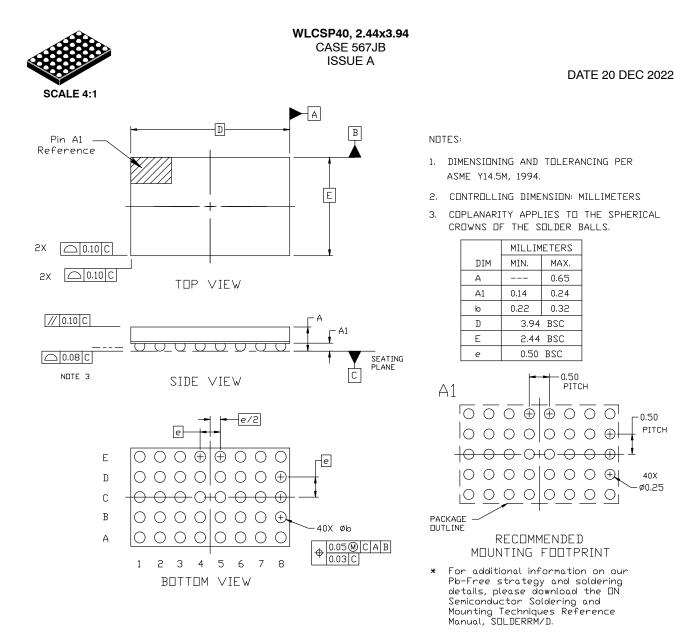

- WLCSP40, 2.44 mm x 3.94 mm, Thickness Max 0.65 mm

- This is a Pb–Free and Halogen Free Device

#### Power Supply Voltage

- DA/VGA: DAOPVDD = 2.6 V to 3.6 V

- AD: ADVDD = 2.6 V to 3.6 V

- IO/OSC/LDO: DVDD30 = 2.6 V to 3.6 V

- Driver: VM = 2.6 V to 5.5 V

- Core Logic: Use built–in LDO/External VDD: DVDD18 = 1.8 V ±10%

WLCSP40, 2.44 x 3.94 CASE 567JB

#### MARKING DIAGRAM

8121 = Specific Device Code

- = Year

- M = Month

Υ

- X = Assembly Location

- ## = Conversion Character Representing Assembly Lot

#### **ORDERING INFORMATION**

| Device        | Package       | Shipping <sup>†</sup> |

|---------------|---------------|-----------------------|

| LC898121XA-MH | WLCSP40,      | 4000 / Tape           |

|               | 2.44 x 3.94   | & Reel                |

|               | (Pb–Free /    |                       |

|               | Halogen Free) |                       |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

## LC898121XA

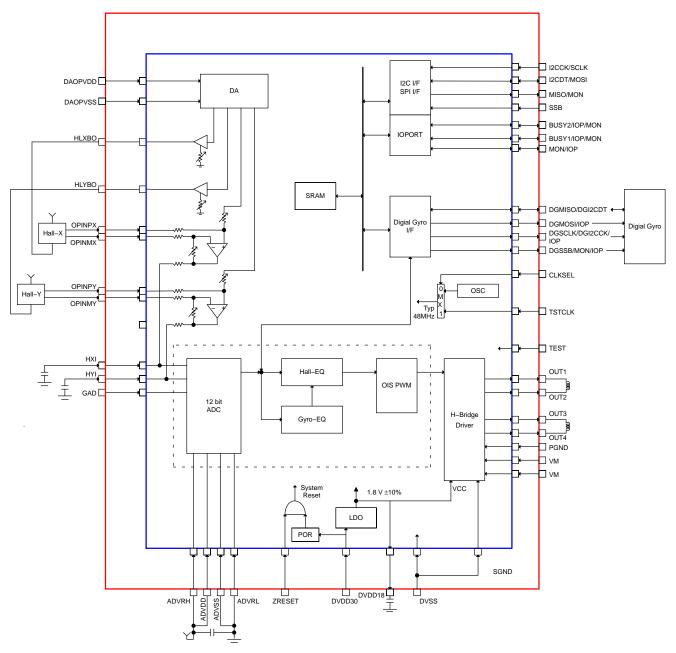

#### **BLOCK DIAGRAM**

Figure 1. Example of Wiring Diagram [Hall] in LC898121XA (WLP40)

## LC898121XA

### **PIN ASSIGNMENT**

|   | Е      | E D C B |         | А       |        |

|---|--------|---------|---------|---------|--------|

| 8 | OPINPX | OPINMY  | ADVDD   | ADVSS   | НХІ    |

|   | OPINMX | OPINPY  | ADVRH   | ADVRL   | HYI    |

| 6 | HLXBO  | HLYBO   | DAOPVDD | DAOPVSS | I2CCK  |

| 5 | DGSCLK | DGMOSI  | GAD     | MISO    | I2CDT  |

| 4 | DGMISO | DGSSB   | MON     | SSB     | DVDD18 |

| 3 | DVSS   | CLKSEL  | TSTCLK  | TEST    | DVDD30 |

| 2 | VM     | BUSY2   | BUSY1   | ZRESET  | VM     |

| - | OUT4   | OUT3    | PGND    | OUT2    | OUT1   |

| I |        |         |         |         |        |

Figure 2. WLP40 Bottom View

# LC898121XA

| Ball No | Pin Name | Туре | Description                                                                                            |  |

|---------|----------|------|--------------------------------------------------------------------------------------------------------|--|

| A1      | OUT1     | 0    | Driver Output                                                                                          |  |

| A2      | VM       | Р    | Driver VDD (2.6 V to 5.5 V)                                                                            |  |

| A3      | DVDD30   | Р    | Logic 3 V VDD (2.6 V to 3.6 V)                                                                         |  |

| A4      | DVDD18   | Р    | LDO Power supply out (Logic Core VDD (typ 1.8 V))                                                      |  |

| A5      | I2CDT    | В    | I2C_IF data (B) / SPI IF data (I)                                                                      |  |

| A6      | I2CCK    | I    | I2C_IF clock / SPI IF clock                                                                            |  |

| A7      | HYI      | I    | Hall-Y AD input                                                                                        |  |

| A8      | HXI      | I    | Hall–X AD input                                                                                        |  |

| B1      | OUT2     | 0    | Driver output                                                                                          |  |

| B2      | ZRESET   | I    | HardWafer Reset                                                                                        |  |

| B3      | TEST     | I    | SPI & External clock case sets [1]. other cases set [0]                                                |  |

| B4      | SSB      | В    | SPI I/F Chip Select (I) / General–purpose IOPORT(B) / inner signal monitor (O)                         |  |

| B5      | MISO     | В    | SPI I/F data (O) / inner signal monitor / General-purpose IOPORT                                       |  |

| B6      | DAOPVSS  | Р    | DA&OpAmp VSS                                                                                           |  |

| B7      | ADVRL    | I    | ADC ReferenceVoltage Low input                                                                         |  |

| B8      | ADVSS    | Ι    | AD GND                                                                                                 |  |

| C1      | PGND     | Р    | Driver GND                                                                                             |  |

| C2      | BUSY1    | В    | BUSY1 (O) / General-purpose IOPORT (B) / inner signal monitor (O)                                      |  |

| C3      | TSTCLK   | -    | CLKSEL = 1: External Clock, CLKSEL = 0: change pin of I <sup>2</sup> C (0) and SPI (1)                 |  |

| C4      | MON      | В    | inner signal monitor / general-purpose IOPORT                                                          |  |

| C5      | GAD      | -    | General AD input                                                                                       |  |

| C6      | DAOPVDD  | Р    | DA&OpAmp VDD (2.6 V to 3.6 V)                                                                          |  |

| C7      | ADVRH    | -    | ADC ReferenceVoltage High input                                                                        |  |

| C8      | ADVDD    | Р    | AD VDD (2.6 V to 3.6 V)                                                                                |  |

| D1      | OUT3     | 0    | Driver output                                                                                          |  |

| D2      | BUSY2    | В    | BUSY2 (O) / General-purpose IOPORT (B) / inner signal monitor (O)                                      |  |

| D3      | CLKSEL   | -    | change pin of OSC (0) and External clock (1)                                                           |  |

| D4      | DGSSB    | В    | Digital Gyro SPI IF Chip Select (O) / inner signal monitor (O) / General-purpose IOPORT (B)            |  |

| D5      | DGMOSI   | В    | Digital Gyro (4-wire) IF data (O) / General-purpose IOPORT (B)                                         |  |

| D6      | HLYBO    | 0    | Hall–Y Bias (Current drive)                                                                            |  |

| D7      | OPINPY   | I    | Hall-Y OpAmp input+                                                                                    |  |

| D8      | OPINMY   | I    | Hall-Y OpAmp input-                                                                                    |  |

| E1      | OUT4     | 0    | Driver output                                                                                          |  |

| E2      | VM       | Р    | Driver VDD (2.6 V to 5.5 V)                                                                            |  |

| E3      | DVSS     | Р    | Logic GND                                                                                              |  |

| E4      | DGMISO   | В    | Digital Gyro SPI IF data( I ) / Digital Gyro I <sup>2</sup> C IF data (B)                              |  |

| E5      | DGSCLK   | В    | Digtal Gyro SPI IF clock (O) / Digital Gyro I <sup>2</sup> C IF clock (O) / General purpose IOPORT (B) |  |

| E6      | HLXBO    | 0    | Hall–Y Bias (Current drive)                                                                            |  |

| E7      | OPINMX   | I    | Hall–X OpAmp input–                                                                                    |  |

| E8      | OPINPX   | I    | Hall-X OpAmp input+                                                                                    |  |

# semi

Electronic versions are uncontrolled except when accessed directly from the Document Repository. **DOCUMENT NUMBER:** 98AON77763F Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. **DESCRIPTION:** WLCSP40, 2.44X3.94 PAGE 1 OF 1

onsemi and OnSemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

0.50

PITCH

40X

Ø0.25

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>