# **Silicon Power Transistors MJ21195G - PNP MJ21196G - NPN**

The MJ21195G and MJ21196G utilize Perforated Emitter technology and are specifically designed for high power audio output, disk head positioners and linear applications.

#### **Features**

- Total Harmonic Distortion Characterized

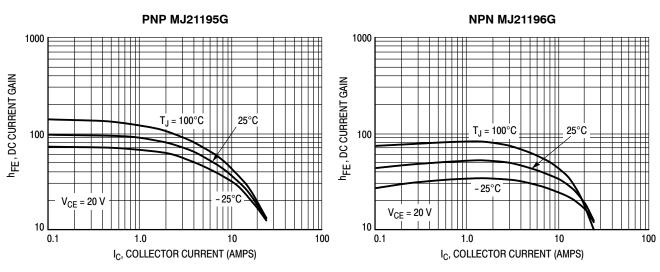

- High DC Current Gain

- Excellent Gain Linearity

- High SOA

- These Devices are Pb-Free and are RoHS Compliant\*

#### **MAXIMUM RATINGS**

| Rating                                                                | Symbol                            | Value       | Unit      |

|-----------------------------------------------------------------------|-----------------------------------|-------------|-----------|

| Collector-Emitter Voltage                                             | V <sub>CEO</sub>                  | 250         | Vdc       |

| Collector-Base Voltage                                                | V <sub>CBO</sub>                  | 400         | Vdc       |

| Emitter-Base Voltage                                                  | V <sub>EBO</sub>                  | 5           | Vdc       |

| Collector-Emitter Voltage - 1.5V                                      | V <sub>CEX</sub>                  | 400         | Vdc       |

| Collector Current - Continuous                                        | I <sub>C</sub>                    | 16          | Adc       |

| Collector Current - Peak (Note 1)                                     | I <sub>CM</sub>                   | 30          | Adc       |

| Base Current - Continuous                                             | I <sub>B</sub>                    | 5           | Adc       |

| Total Device Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C | P <sub>D</sub>                    | 250<br>1.43 | W<br>W/°C |

| Operating and Storage Junction<br>Temperature Range                   | T <sub>J</sub> , T <sub>stg</sub> | -65 to +200 | °C        |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Pulse Test: Pulse Width = 5 μs, Duty Cycle ≤ 10%.

### THERMAL CHARACTERISTICS

| Characteristics                      | Symbol          | Max | Unit |

|--------------------------------------|-----------------|-----|------|

| Thermal Resistance, Junction-to-Case | $R_{\theta JC}$ | 0.7 | °C/W |

# 16 AMPERES COMPLEMENTARY SILICON-POWER TRANSISTORS **250 VOLTS, 250 WATTS**

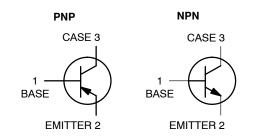

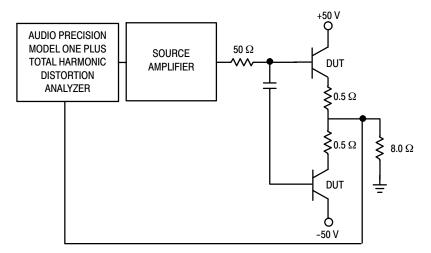

#### **SCHEMATIC**

TO-204AA (TO-3) **CASE 1-07** STYLE 1

#### **MARKING DIAGRAM**

MJ2119x = Device Code x = 5 or 6

= Pb-Free Package G = Assembly Location Α Year

WW Work Week MEX = Country of Origin

# ORDERING INFORMATION

| Device   | Package             | Shipping         |

|----------|---------------------|------------------|

| MJ21195G | TO-204<br>(Pb-Free) | 100 Units / Tray |

| MJ21196G | TO-204<br>(Pb-Free) | 100 Units / Tray |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

1

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **ELECTRICAL CHARACTERISTICS** ( $T_C = 25^{\circ}C \pm 5^{\circ}C$ unless otherwise noted)

| Characteristic                                                                                                                                                                        | Symbol                | Min      | Typical | Max      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------|----------|------|

| OFF CHARACTERISTICS                                                                                                                                                                   |                       |          |         |          |      |

| Collector–Emitter Sustaining Voltage $(I_C = 100 \text{ mAdc}, I_B = 0)$                                                                                                              | V <sub>CEO(sus)</sub> | 250      | -       | -        | Vdc  |

| Collector Cutoff Current (V <sub>CE</sub> = 200 Vdc, I <sub>B</sub> = 0)                                                                                                              | I <sub>CEO</sub>      | -        | -       | 100      | μAdc |

| Emitter Cutoff Current (V <sub>CE</sub> = 5 Vdc, I <sub>C</sub> = 0)                                                                                                                  | I <sub>EBO</sub>      | -        | -       | 100      | μAdc |

| Collector Cutoff Current<br>(V <sub>CE</sub> = 250 Vdc, V <sub>BE(off)</sub> = 1.5 Vdc)                                                                                               | I <sub>CEX</sub>      | -        | -       | 100      | μAdc |

| SECOND BREAKDOWN                                                                                                                                                                      |                       |          |         |          |      |

| Second Breakdown Collector Current with Base Forward Biased $(V_{CE} = 50 \text{ Vdc}, t = 1 \text{ s (non-repetitive)}$ $(V_{CE} = 80 \text{ Vdc}, t = 1 \text{ s (non-repetitive)}$ | I <sub>S/b</sub>      | 5<br>2.5 | 1 1     | -<br>-   | Adc  |

| ON CHARACTERISTICS                                                                                                                                                                    |                       |          |         |          |      |

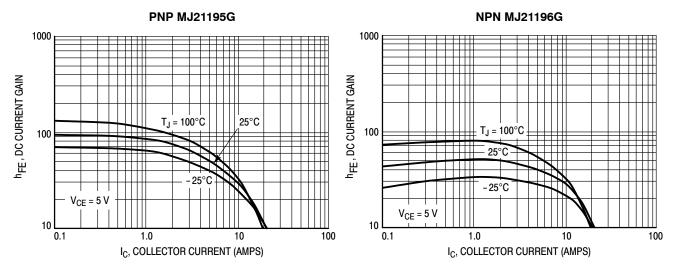

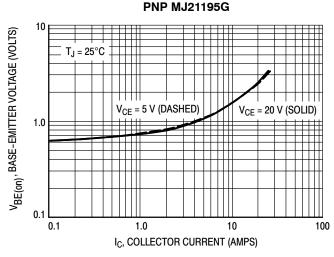

| DC Current Gain ( $I_C = 8$ Adc, $V_{CE} = 5$ Vdc) ( $I_C = 16$ Adc, $V_{CE} = 5$ Vdc)                                                                                                | h <sub>FE</sub>       | 25<br>8  | - 1     | 75       | -    |

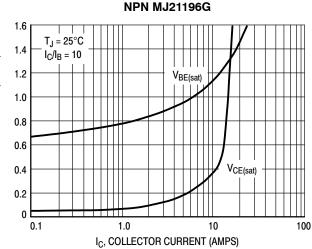

| Base–Emitter On Voltage ( $I_C = 8$ Adc, $V_{CE} = 5$ Vdc)                                                                                                                            | V <sub>BE(on)</sub>   | -        | -       | 2.2      | Vdc  |

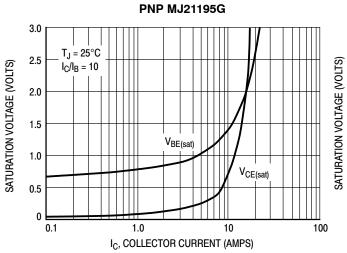

| Collector–Emitter Saturation Voltage ( $I_C = 8$ Adc, $I_B = 0.8$ Adc) ( $I_C = 16$ Adc, $I_B = 3.2$ Adc)                                                                             | V <sub>CE(sat)</sub>  | -<br>-   | -<br>-  | 1.4<br>4 | Vdc  |

| DYNAMIC CHARACTERISTICS                                                                                                                                                               |                       |          |         |          |      |

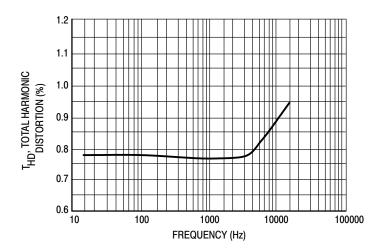

| Total Harmonic Distortion at the Output  V <sub>RMS</sub> = 28.3 V, f = 1 kHz, P <sub>LOAD</sub> = 100 W <sub>RMS</sub> h <sub>FE</sub> unmatched                                     | T <sub>HD</sub>       | _        | 0.8     | _        | %    |

| (Matched pair h <sub>FE</sub> = 50 @ 5 A/5 V) h <sub>FE</sub> matched                                                                                                                 |                       | -        | 0.08    | _        |      |

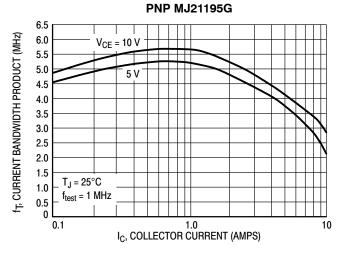

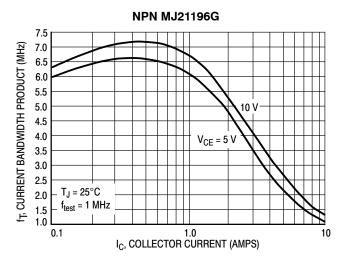

| Current Gain Bandwidth Product<br>(I <sub>C</sub> = 1 Adc, V <sub>CE</sub> = 10 Vdc, f <sub>test</sub> = 1 MHz)                                                                       | f <sub>T</sub>        | 4        | -       | _        | MHz  |

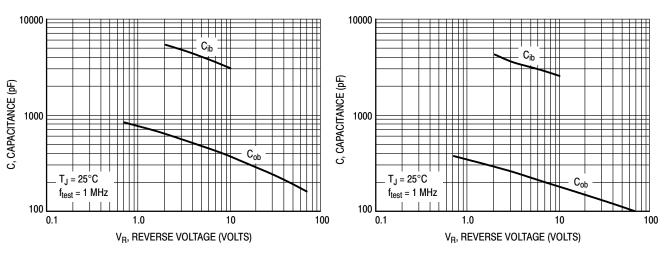

| Output Capacitance<br>(V <sub>CB</sub> = 10 Vdc, I <sub>E</sub> = 0, f <sub>test</sub> = 1 MHz)                                                                                       | C <sub>ob</sub>       | -        | -       | 500      | pF   |

<sup>2.</sup> Pulse Test: Pulse Width = 300  $\mu$ s, Duty Cycle  $\leq$ 2%

Figure 1. Typical Current Gain Bandwidth Product

Figure 2. Typical Current Gain Bandwidth Product

# **TYPICAL CHARACTERISTICS**

Figure 3. DC Current Gain, V<sub>CE</sub> = 20 V

Figure 4. DC Current Gain, V<sub>CE</sub> = 20 V

Figure 5. DC Current Gain, V<sub>CE</sub> = 5 V

30

25

20

15

10

5.0

0 0

I<sub>C</sub>, COLLECTOR CURRENT (A)

**PNP MJ21195G NPN MJ21196G** 30  $I_B = 2 A$  $I_B = 2 A$ 1.5 A 25 1.5 A I<sub>C</sub>, COLLECTOR CURRENT (A) 1 A 1 A 20 0.5 A 0.5 A 15 10 5.0  $T_J = 25^{\circ}C$  $T_J = 25^{\circ}C$ 0 25 0 25 V<sub>CE</sub>, COLLECTOR-EMITTER VOLTAGE (VOLTS) V<sub>CE</sub>, COLLECTOR-EMITTER VOLTAGE (VOLTS)

Figure 7. Typical Output Characteristics

Figure 8. Typical Output Characteristics

Figure 6. DC Current Gain, V<sub>CE</sub> = 5 V

# TYPICAL CHARACTERISTICS

Figure 9. Typical Saturation Voltages

Figure 10. Typical Saturation Voltages

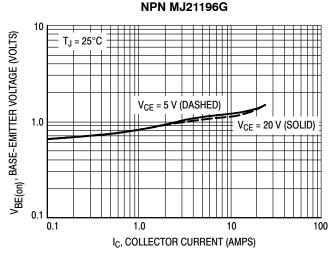

Figure 11. Typical Base-Emitter Voltage

Figure 12. Typical Base-Emitter Voltage

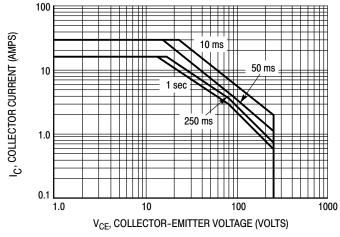

Figure 13. Active Region Safe Operating Area

There are two limitations on the power handling ability of a transistor; average junction temperature and secondary breakdown. Safe operating area curves indicate  $I_C - V_{CE}$  limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

The data of Figure 13 is based on  $T_{J(pk)} = 200^{\circ} C$ ;  $T_{C}$  is variable depending on conditions. At high case temperatures, thermal limitations will reduce the power than can be handled to values less than the limitations imposed by second breakdown.

Figure 14. MJ21195 Typical Capacitance

Figure 15. MJ21196 Typical Capacitance

Figure 16. Typical Total Harmonic Distortion

Figure 17. Total Harmonic Distortion Test Circuit

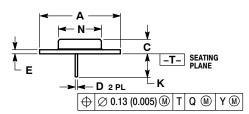

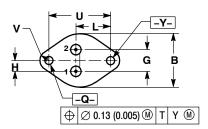

TO-204 (TO-3) CASE 1-07 ISSUE Z

**DATE 10 MAR 2000**

# SCALE 1:1

CASE: COLLECTOR

CASE: CATHODE

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCH.

3. ALL RULES AND NOTES ASSOCIATED WITH

REFERENCED TO-204AA OUTLINE SHALL APPLY.

|     | INCHES    |           | MILLIN    | IETERS |

|-----|-----------|-----------|-----------|--------|

| DIM | MIN       | MAX       | MIN       | MAX    |

| Α   | 1.550     | 1.550 REF |           | REF    |

| В   |           | 1.050     |           | 26.67  |

| C   | 0.250     | 0.335     | 6.35      | 8.51   |

| D   | 0.038     | 0.043     | 0.97      | 1.09   |

| Е   | 0.055     | 0.070     | 1.40      | 1.77   |

| G   | 0.430 BSC |           | 10.92 BSC |        |

| Н   | 0.215 BSC |           | 5.46 BSC  |        |

| K   | 0.440     | 0.480     | 11.18     | 12.19  |

| L   | 0.665 BSC |           | 16.89 BSC |        |

| N   |           | 0.830     |           | 21.08  |

| Q   | 0.151     | 0.165     | 3.84      | 4.19   |

| U   | 1.187 BSC |           | 30.15 BSC |        |

| ٧   | 0.131     | 0.188     | 3.33      | 4.77   |

STYLE 2: PIN 1. BASE 2. COLLECTOR STYLE 3: PIN 1. GATE 2. SOURCE STYLE 5: PIN 1. CATHODE 2. EXTERNAL TRIP/DELAY CASE: ANODE STYLE 4: PIN 1. GROUND 2. INPUT STYLE 1: PIN 1. BASE 2. EMITTER CASE: COLLECTOR CASE: EMITTER CASE: DRAIN CASE: OUTPUT STYLE 6: STYLE 7: STYLE 8: STYLE 9: PIN 1. CATHODE #1 2. CATHODE #2 PIN 1. GATE 2. EMITTER PIN 1. ANODE 2. OPEN PIN 1. ANODE #1 2. ANODE #2

CASE: CATHODE

CASE: ANODE

| DOCUMENT NUMBER: | 98ASB42001B   | Electronic versions are uncontrolled except when accessed directly from the Document Reposition Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TO-204 (TO-3) |                                                                                                                                                                                 | PAGE 1 OF 1 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves onsem and of 15G11 if are trademarks of Semiconductor Components industries, LLC due onsem or its substitutines in the Office States and/or other countries. Onsem reserves the right to make changes without further notice to any products herein. onsem makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales