# 3.3 V 100/133 MHz Differential 1:19 HCSL Clock ZDB/Fanout Buffer for PCle<sup>®</sup>

# **NB3N1900K**

### **Description**

The NB3N1900K differential clock buffers are designed to work in conjunction with a PCIe compliant source clock synthesizer to provide point—to—point clocks to multiple agents. The device is capable of distributing the reference clocks for Intel<sup>®</sup> QuickPath Interconnect (Intel QPI & UPI), PCIe Gen1, Gen2, Gen3, Gen4. The NB3N1900K internal PLL is optimized to support 100 MHz and 133 MHz frequency operation. The NB3N1900K supports HCSL output levels.

#### **Features**

- Fixed Feedback Path for Lowest Input-to-Output Delay

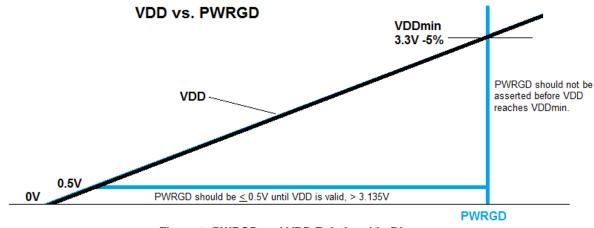

- Eight Dedicated OE# Pins for Hardware Control of Outputs

- PLL Bypass Configurable for PLL or Fanout Operation

- Selectable PLL Bandwidth

- Spread Spectrum Compatible: Tracks Input Clock Spreading for Low EMI

- SMBus Programmable Configurations

- 100 MHz and 133 MHz PLL Mode to Meet the Next Generation PCIe Gen2/Gen3/Gen4 and Intel QPI & UPI Phase Jitter

- 2 Tri-Level Addresses Selection (Nine SMBUS Addresses)

- Cycle-to-Cycle Jitter: < 50 ps

- Output-to-Output Skew: < 65 ps

- Input-to-Output Delay: Fixed at 0 ps

- Input-to-Output Delay Variation: < 50 ps

- Phase Jitter: PCIe Gen3 < 1 ps rms

- Phase Jitter: PCIe Gen4 < 0.5 ps rms

- Phase Jitter: QPI 9.6GB/s < 0.12 ps rms

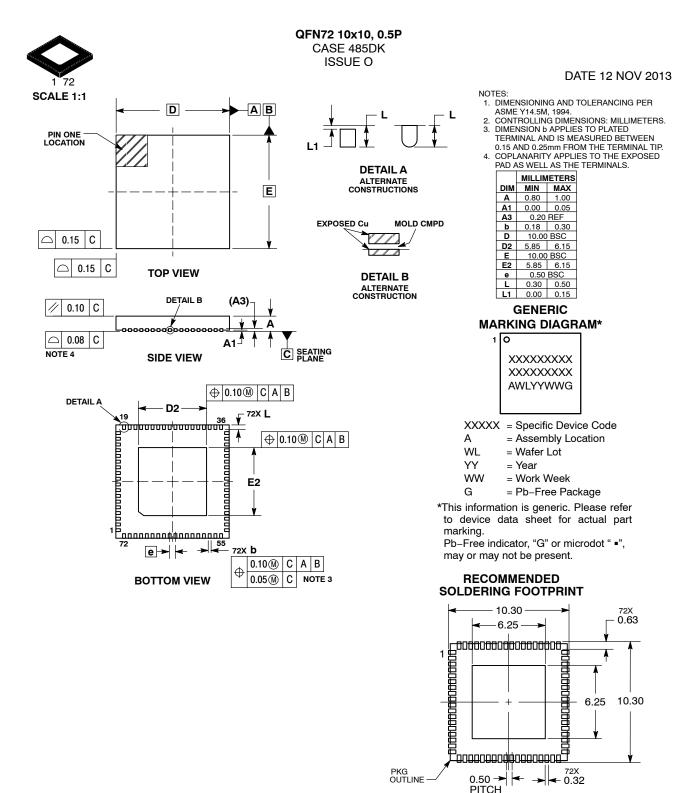

- QFN 72-pin Package, 10 mm x 10 mm

- These are Pb-Free Devices

QFN72 MN SUFFIX CASE 485DK

#### **MARKING DIAGRAM\***

NB3N1900K = Specific Device Code

= Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 21 of this data sheet.

NOTE: Some of the devices on this data sheet have been **DISCONTINUED**. Please refer to the table on page 21.

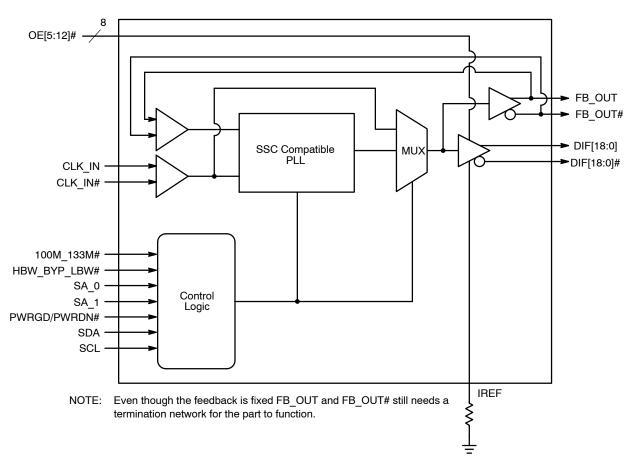

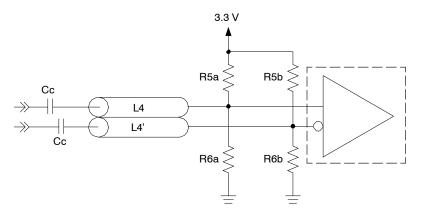

Figure 1. Simplified Block Diagram of NB3N1900K

FB\_OUT pins loaded the same as the DIF outputs.

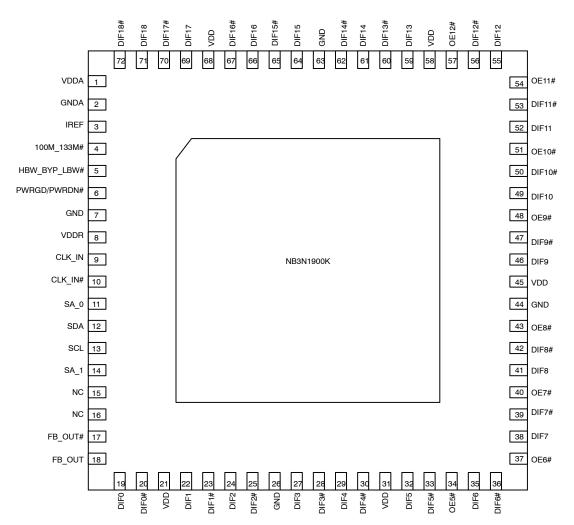

Figure 2. Pin Configuration (Top View)

Table 1. PLL OPERATING MODE READBACK TABLE

| HBW_BYP_LBW#   | Byte0, bit 7 | Byte 0, bit 6 |

|----------------|--------------|---------------|

| Low (Low BW)   | 0            | 0             |

| Mid (Bypass)   | 0            | 1             |

| High (High BW) | 1            | 1             |

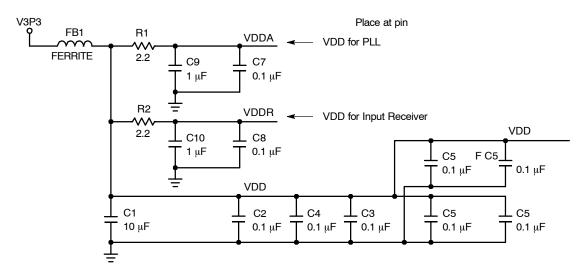

### **Table 2. POWER CONNECTIONS**

| Pin Nu                | ımber      |              |

|-----------------------|------------|--------------|

| VDD GND               |            | Description  |

| 1                     | 2          | Analog PLL   |

| 8                     | 7          | Analog Input |

| 21, 31, 45,<br>58, 68 | 26, 44, 63 | DIF clocks   |

## Table 3. FUNCTIONALITY AT POWER UP (PLL MODE)

| 100M_133M# | CLK_IN<br>(MHz) | DIF<br>(MHz) |

|------------|-----------------|--------------|

| 1          | 100.00          | CLK_IN       |

| 0          | 133.33          | CLK_IN       |

Table 4. NB3N1900K SMBus ADDRESSING

| Pin  |      | SMBus Address – 8 bit |

|------|------|-----------------------|

| SA_1 | SA_0 | (Rd/Wrt bit = 0)      |

| 0    | 0    | D8                    |

| 0    | М    | DA                    |

| 0    | 1    | DE                    |

| М    | 0    | C2                    |

| М    | М    | C4                    |

| М    | 1    | C6                    |

| 1    | 0    | CA                    |

| 1    | М    | CC                    |

| 1    | 1    | CE                    |

## **Table 5. PLL OPERATING MODE**

| HBW_BYP_LBW# | MODE      |

|--------------|-----------|

| Low          | PLL Lo BW |

| Mid          | Bypass    |

| High         | PLL Hi BW |

NOTE: PLL is OFF in Bypass

Table 6. MODE TRI-LEVEL INPUT THRESHOLD

| Level | Voltage           |

|-------|-------------------|

| Low   | < 0.8 V           |

| Mid   | 1.2 < Vin < 1.8 V |

| High  | Vin > 2.2 V       |

## **Table 7. PIN DESCRIPTION**

| differential impedances. Other impedances require different values.  See data sheet.  IN Input to select operating frequency 1 = 100.00 MHz, 0 = 133.33 MHz  IN Trilevel input to select High BW, Bypass or Low BW mode. See PLL Operating Mode Table for Details.  Notifies device to sample latched inputs and start up on first high assertion, or exit Power Down Mode on subsequent assertions. Low enters Power Down Mode.  Repure Town Mode on Subsequent assertions. This VDD should be treated as an analog power rail and filtered appropriately.  CLK_IN IN 0.7 V Differential true input  CLK_IN# IN 0.7 V Differential complementary Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin# | Pin Name     | Pin Type | Description                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This pin establishes the reference for the differential current—mode output pairs. It requires a fixed precision resistor to ground, 47% 8 is the standard value for 100 Ω See also sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1    | VDDA         | PWR      | 3.3 V power for the PLL core.                                                                                                                                         |

| See                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2    | GNDA         | PWR      | Ground pin for the PLL core.                                                                                                                                          |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3    | IREF         | OUT      | requires a fixed precision resistor to ground. 475 $\Omega$ is the standard value for 100 $\Omega$ differential impedance. Other impedances require different values. |

| See PLL Operating Mode Table for Details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4    | 100M_133M#   | IN       |                                                                                                                                                                       |

| PWNGU/PWNDW    Pww   Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5    | HBW_BYP_LBW# | IN       |                                                                                                                                                                       |

| B VDDR PWR 3.3 V power for differential input clock (receiver). This VDD should be treated as an analog power rail and filtered appropriately.  9 CLK_IN# IN 0.7 V Differential true input  10 CLK_IN# IN 0.7 V Differential compjementary Input  11 SA_0 IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_1 to decode 1 of 9 SMBus Addresses.  12 SDA I/O Data pin of SMBus circuitry, 5V tolerant  13 SCL IN Clock pin of SMBus circuitry, 5V tolerant  14 SA_1 IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_1 to decode 1 of 9 SMBus Addresses.  15 NC N/A No Connection.  16 NC N/A No Connection.  17 FB_OUT# OUT Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  18 FB_OUT OUT True half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  19 DIFO OUT 0.7 V differential true clock output  20 DIFO# OUT 0.7 V differential true clock output  21 VDD PWR Power supply, nominal 3.3 V  22 DIF1 OUT 0.7 V differential true clock output  23 DIF1# OUT 0.7 V differential true clock output  24 DIF2 OUT 0.7 V differential true clock output  25 DIF2# OUT 0.7 V differential true clock output  26 GAND PWR Ground pin.  27 DIF3 OUT 0.7 V differential complementary clock output  28 DIF3# OUT 0.7 V differential complementary clock output  30 DIF4# OUT 0.7 V differential complementary clock output  31 VDD PWR Power supply, nominal 3.3 V  32 DIF5# OUT 0.7 V differential true clock output  33 DIF5# OUT 0.7 V differential true clock output  34 OES# IN Active low input for enabling DIF pair 6.  35 DIF6# OUT 0.7 V differential complementary clock output  36 DIF6# OUT 0.7 V differential complementary clock output  37 OLE## OUT 0.7 V differential complementary clock output  38 DIF6# OUT 0.7 V differential complementary clock output  39 DIF6# OUT 0.7 V differential complementary clock output  30 DIF6# OUT 0.7  | 6    | PWRGD/PWRDN# | IN       | Notifies device to sample latched inputs and start up on first high assertion, or exit Power Down Mode on subsequent assertions. Low enters Power Down Mode.          |

| 9 CLK_IN IN 0.7 V Differential true input 10 CLK_IN# IN 0.7 V Differential true input 11 SA_0 IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_1 to decode 1 of 9 SMBus circuitry, 5V tolerant 12 SDA I/O Data pin of SMBus circuitry, 5V tolerant 13 SCL IN Clock pin of SMBus circuitry, 5V tolerant 14 SA_1 IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_1 to decode 1 of 9 SMBus circuitry, 5V tolerant 14 SA_1 IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_0 to decode 1 of 9 SMBus Addresses. 16 NC N/A No Connection. 17 FB_OUT# OUT Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error. 18 FB_OUT OUT True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error. 19 DIFO OUT 0.7 V differential true clock output 20 DIFO# OUT 0.7 V differential true clock output 21 VDD PWR Power supply, nominal 3.3 V 22 DIF1 OUT 0.7 V differential complementary clock output 23 DIF1# OUT 0.7 V differential complementary clock output 24 DIF2 OUT 0.7 V differential complementary clock output 25 DIF2# OUT 0.7 V differential complementary clock output 26 GND PWR Ground pin. 27 DIF3# OUT 0.7 V differential true clock output 30 DIF3# OUT 0.7 V differential true clock output 31 VDD PWR Power supply, nominal 3.3 V 32 DIF6# OUT 0.7 V differential complementary clock output 33 DIF6# OUT 0.7 V differential complementary clock output 34 OE5# IN Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                    | 7    | GND          | PWR      | Ground pin.                                                                                                                                                           |

| 10 CLK_IN# IN 0.7 V Differential complementary Input  11 SA_0 IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_1  12 SDA I/O Data pin of SMBus circuitry, 5V tolerant  13 SCL IN Clock pin of SMBus circuitry, 5V tolerant  14 SA_1 IN SMBus addresses.  16 NC N/A No Connection.  17 NA No Connection.  18 FB_OUT# OUT Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  18 FB_OUT# OUT True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  18 FB_OUT OUT O.7 V differential complementary clock output  19 DIFO OUT 0.7 V differential true clock output  20 DIFO# OUT 0.7 V differential true clock output  21 VDD PWR Power supply, nominal 3.3 V  22 DIF1# OUT 0.7 V differential rue clock output  23 DIF1# OUT 0.7 V differential rue clock output  24 DIF2 OUT 0.7 V differential rue clock output  25 DIF2# OUT 0.7 V differential rue clock output  26 GND PWR Ground pin.  27 DIF3# OUT 0.7 V differential rue clock output  30 DIF4# OUT 0.7 V differential rue clock output  31 VDD PWR Ground pin.  32 DIF3# OUT 0.7 V differential rue clock output  33 DIF5# OUT 0.7 V differential rue clock output  34 DIF5# OUT 0.7 V differential rue clock output  35 DIF6# OUT 0.7 V differential rue clock output  36 DIF6# OUT 0.7 V differential rue clock output  37 A DIF6# OUT 0.7 V differential rue clock output  38 DIF6# OUT 0.7 V differential rue clock output  39 DIF6# OUT 0.7 V differential rue clock output  30 DIF6# OUT 0.7 V differential rue clock output  31 Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                   | 8    | VDDR         | PWR      | 3.3 V power for differential input clock (receiver). This VDD should be treated as an analog power rail and filtered appropriately.                                   |

| IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_1 to decode 1 of 9 SMBus Addresses.  IV Data pin of SMBus circuitry, 5V tolerant  SCL IN Clock pin of SMBus circuitry, 5V tolerant  IN SMBus addresses.  IN Clock pin of SMBus circuitry, 5V tolerant  SA_1 IN SMBus addresses bit. This is a tri-level input that works in conjunction with the SA_0 to decode 1 of 9 SMBus Addresses.  NC N/A No Connection.  NOC N/A No Connection.  TO PB_OUT# OUT Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  PUT 0.7 V differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  PUT 0.7 V differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  PUT 0.7 V differential true clock output  OUT 0.7 V differential true clock output  DIF1 OUT 0.7 V differential true clock output  DIF2 OUT 0.7 V differential true clock output  DIF3 OUT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential true clock output  DIF4 OUT 0.7 V differential true clock output  DIF4 OUT 0.7 V differential complementary clock output  DIF5 OUT 0.7 V differential complementary clock output  N Active low input for enabling DIF pair 5.  1 disable outputs, 0 = enable outputs  DIF6 OUT 0.7 V differential complementary clock output  N Active low input for enabling DIF pair 6.                                                                  | 9    | CLK_IN       | IN       | 0.7 V Differential true input                                                                                                                                         |

| 12 SDA I/O Data pin of SMBus Addresses.  13 SCL IN Clock pin of SMBus circuitry, 5V tolerant  14 SA_1 IN Clock pin of SMBus circuitry, 5V tolerant  15 NC N/A No Connection.  16 NC N/A No Connection.  17 FB_OUT# OUT Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  18 FB_OUT OUT True half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  18 FB_OUT OUT True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  19 DIFO OUT 0.7 V differential true clock output  20 DIFO# OUT 0.7 V differential true clock output  21 VDD PWR Power supply, nominal 3.3 V  22 DIF1 OUT 0.7 V differential complementary clock output  23 DIF1# OUT 0.7 V differential complementary clock output  24 DIF2 OUT 0.7 V differential complementary clock output  25 DIF2# OUT 0.7 V differential complementary clock output  26 GND PWR Ground pin.  27 DIF3 OUT 0.7 V differential complementary clock output  28 DIF3# OUT 0.7 V differential complementary clock output  29 DIF4 OUT 0.7 V differential complementary clock output  30 DIF4# OUT 0.7 V differential complementary clock output  31 VDD PWR Power supply, nominal 3.3 V  32 DIF5 OUT 0.7 V differential complementary clock output  33 DIF5# OUT 0.7 V differential complementary clock output  34 OE5# IN Active low input for enabling DIF pair 5.  1 - disable outputs, 0 = enable outputs  36 DIF6# OUT 0.7 V differential complementary clock output                                                                                                                                                                                                                                                                                                                                                                                                                         | 10   | CLK_IN#      | IN       | 0.7 V Differential complementary Input                                                                                                                                |

| SCL IN Clock pin of SMBus circuitry, 5V tolerant  SA_1 IN SMBus address bit. This is a tri-level input that works in conjunction with the SA_C to decode 1 of 9 SMBus Addresses.  NC N/A No Connection.  NC N/A No Connection.  Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  PB_OUT OT 0.7 V differential true clock output provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  PB_OUT OT 0.7 V differential true clock output  OT 0.7 V differential complementary clock output  DIFO OUT 0.7 V differential true clock output  OT 0.7 V differential true clock output  DIF1 OUT 0.7 V differential true clock output  DIF2 OUT 0.7 V differential complementary clock output  DIF2 OUT 0.7 V differential true clock output  OT 0.7 V differential complementary clock output  DIF3 OUT 0.7 V differential true clock output  OT 0.7 V differential complementary clock output  DIF3 OUT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential complementary clock output  OT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential true clock output  OT 0.7 V differential complementary clock output  DIF5 OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 5. 1 disable outputs, 0 = enable outputs  DIF6 OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                          | 11   | SA_0         | IN       | SMBus address bit. This is a tri-level input that works in conjunction with the SA_1 to decode 1 of 9 SMBus Addresses.                                                |

| SMBus address bit. This is a tri–level input that works in conjunction with the SA_C to decode 1 of 9 SMBus Addresses.  NC N/A No Connection.  NC N/A No Connection.  Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  BEQUIT OUT True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  DIFO OUT 0.7 V differential true clock output  DIFO# OUT 0.7 V differential true clock output  DIFO# OUT 0.7 V differential complementary clock output  DIF1# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential complementary clock output  DIF3# OUT 0.7 V differential complementary clock output  DIF3# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential complementary clock output  DIF5# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 e disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12   | SDA          | I/O      | Data pin of SMBus circuitry, 5V tolerant                                                                                                                              |

| to decode 1 of 9 SMBus Addresses.  NC N/A No Connection.  NC N/A No Connection.  FB_OUT# OUT Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock output  Tue half of differential true | 13   | SCL          | IN       | Clock pin of SMBus circuitry, 5V tolerant                                                                                                                             |

| NC   N/A   No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14   | SA_1         | IN       |                                                                                                                                                                       |

| Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  DIFO# OUT 0.7 V differential true clock output  DIFO# OUT 0.7 V differential complementary clock output  DIF1# OUT 0.7 V differential true clock output  DIF1# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential complementary clock output  GRND PWR Ground pin.  DIF3# OUT 0.7 V differential true clock output  DIF3# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  IN Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15   | NC           | N/A      | No Connection.                                                                                                                                                        |

| PLL for synchronization with input clock to eliminate phase error.  PLL for synchronization with input clock to eliminate phase error.  True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.  PDIFO OUT 0.7 V differential true clock output  DIFO# OUT 0.7 V differential complementary clock output  DIFO# OUT 0.7 V differential true clock output  DIFO# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  DIFO# OUT 0.7 V differential true clock output  DIFO# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16   | NC           | N/A      | No Connection.                                                                                                                                                        |

| synchronization with the input clock to eliminate phase error.  19 DIFO OUT 0.7 V differential true clock output  20 DIF0# OUT 0.7 V differential complementary clock output  21 VDD PWR Power supply, nominal 3.3 V  22 DIF1 OUT 0.7 V differential true clock output  23 DIF1# OUT 0.7 V differential complementary clock output  24 DIF2 OUT 0.7 V differential true clock output  25 DIF2# OUT 0.7 V differential complementary clock output  26 GND PWR Ground pin.  27 DIF3 OUT 0.7 V differential true clock output  28 DIF3# OUT 0.7 V differential complementary clock output  29 DIF4 OUT 0.7 V differential complementary clock output  30 DIF4# OUT 0.7 V differential complementary clock output  31 VDD PWR Power supply, nominal 3.3 V  32 DIF5 OUT 0.7 V differential true clock output  33 DIF5# OUT 0.7 V differential complementary clock output  34 OES# IN Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  36 DIF6# OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17   | FB_OUT#      | OUT      |                                                                                                                                                                       |

| DIFO# OUT 0.7 V differential complementary clock output  PWR Power supply, nominal 3.3 V  DIF1 OUT 0.7 V differential true clock output  DIF1# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential true clock output  Ground pin.  DIF3# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18   | FB_OUT       | OUT      |                                                                                                                                                                       |

| PWR Power supply, nominal 3.3 V  DIF1 OUT 0.7 V differential true clock output  DIF1# OUT 0.7 V differential complementary clock output  DIF2# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential true clock output  COLUMN OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential complementary clock output  COLUMN OUT 0.7 V differential true clock output  DIF3 OUT 0.7 V differential true clock output  DIF3# OUT 0.7 V differential complementary clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential complementary clock output  DIF4# OUT 0.7 V differential complementary clock output  DIF5# OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19   | DIF0         | OUT      | 0.7 V differential true clock output                                                                                                                                  |

| DIF1 OUT 0.7 V differential true clock output  DIF2 OUT 0.7 V differential complementary clock output  DIF2 OUT 0.7 V differential true clock output  DIF2 OUT 0.7 V differential true clock output  DIF2 OUT 0.7 V differential complementary clock output  Ground pin.  DIF3 OUT 0.7 V differential true clock output  DIF3 OUT 0.7 V differential true clock output  DIF3 OUT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential true clock output  DIF4 OUT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential complementary clock output  DIF5 OUT 0.7 V differential true clock output  DIF5 OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6 OUT 0.7 V differential true clock output  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20   | DIF0#        | OUT      | 0.7 V differential complementary clock output                                                                                                                         |

| DIF1# OUT 0.7 V differential complementary clock output  DIF2# OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential complementary clock output  GROD PWR Ground pin.  DIF3 OUT 0.7 V differential true clock output  DIF3# OUT 0.7 V differential true clock output  DIF3# OUT 0.7 V differential complementary clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential complementary clock output  DIF4# OUT 0.7 V differential complementary clock output  DIF5# OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential true clock output  NOE5# IN Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21   | VDD          | PWR      | Power supply, nominal 3.3 V                                                                                                                                           |

| DIF2 OUT 0.7 V differential true clock output  DIF2# OUT 0.7 V differential complementary clock output  GND PWR Ground pin.  DIF3 OUT 0.7 V differential true clock output  DIF3# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential complementary clock output  VDD PWR Power supply, nominal 3.3 V  DIF5# OUT 0.7 V differential true clock output  NOT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22   | DIF1         | OUT      | 0.7 V differential true clock output                                                                                                                                  |

| DIF2# OUT 0.7 V differential complementary clock output  PWR Ground pin.  OUT 0.7 V differential true clock output  DIF3 OUT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential true clock output  DIF4 OUT 0.7 V differential complementary clock output  VDD PWR Power supply, nominal 3.3 V  DIF5 OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 5.  In Active low input for enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enable outputs  DIF6# OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23   | DIF1#        | OUT      | 0.7 V differential complementary clock output                                                                                                                         |

| GND PWR Ground pin.  OUT 0.7 V differential true clock output  DIF3# OUT 0.7 V differential complementary clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential complementary clock output  VDD PWR Power supply, nominal 3.3 V  DIF5 OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential true clock output  Active low input for enabling DIF pair 5.  1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enable outputs  DIF6# OUT 0.7 V differential complementary clock output  Active low input for enable outputs  DIF6# OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24   | DIF2         | OUT      | 0.7 V differential true clock output                                                                                                                                  |

| DIF3 OUT 0.7 V differential true clock output  DIF3# OUT 0.7 V differential complementary clock output  DIF4# OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential complementary clock output  VDD PWR Power supply, nominal 3.3 V  DIF5 OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential true clock output  N Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  N Active low input for enable outputs  DIF6# OUT 0.7 V differential true clock output  N Active low input for enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enable outputs  DIF6# OUT 0.7 V differential complementary clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25   | DIF2#        | OUT      | 0.7 V differential complementary clock output                                                                                                                         |

| DIF3# OUT 0.7 V differential complementary clock output  DIF4 OUT 0.7 V differential true clock output  DIF4# OUT 0.7 V differential complementary clock output  VDD PWR Power supply, nominal 3.3 V  DIF5 OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential true clock output  NOE5# IN Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enable outputs  DIF6# OUT 0.7 V differential true clock output  Active low input for enable outputs  Active low input for enable outputs  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26   | GND          | PWR      | Ground pin.                                                                                                                                                           |

| DIF4 OUT 0.7 V differential true clock output  OUT 0.7 V differential complementary clock output  DIF4# OUT 0.7 V differential complementary clock output  DIF5 OUT 0.7 V differential true clock output  DIF5# OUT 0.7 V differential complementary clock output  DIF5# OUT 0.7 V differential complementary clock output  NACtive low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6# OUT 0.7 V differential true clock output  DIF6# OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27   | DIF3         | OUT      | 0.7 V differential true clock output                                                                                                                                  |

| 30 DIF4# OUT 0.7 V differential complementary clock output 31 VDD PWR Power supply, nominal 3.3 V 32 DIF5 OUT 0.7 V differential true clock output 33 DIF5# OUT 0.7 V differential complementary clock output 34 OE5# IN Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs 35 DIF6 OUT 0.7 V differential true clock output 36 DIF6# OUT 0.7 V differential complementary clock output 37 OF6# Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28   | DIF3#        | OUT      | 0.7 V differential complementary clock output                                                                                                                         |

| 31 VDD PWR Power supply, nominal 3.3 V  32 DIF5 OUT 0.7 V differential true clock output  33 DIF5# OUT 0.7 V differential complementary clock output  34 OE5# IN Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  35 DIF6 OUT 0.7 V differential true clock output  36 DIF6# OUT 0.7 V differential complementary clock output  37 OF6# Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29   | DIF4         | OUT      | 0.7 V differential true clock output                                                                                                                                  |

| 32 DIF5 OUT 0.7 V differential true clock output  33 DIF5# OUT 0.7 V differential complementary clock output  34 OE5# IN Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  35 DIF6 OUT 0.7 V differential true clock output  36 DIF6# OUT 0.7 V differential complementary clock output  37 OF6# Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30   | DIF4#        | OUT      | 0.7 V differential complementary clock output                                                                                                                         |

| OE5# OUT 0.7 V differential complementary clock output  IN Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  DIF6 OUT 0.7 V differential true clock output  OUT 0.7 V differential complementary clock output  Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31   | VDD          | PWR      | Power supply, nominal 3.3 V                                                                                                                                           |

| 34 OE5# IN Active low input for enabling DIF pair 5. 1 = disable outputs, 0 = enable outputs  35 DIF6 OUT 0.7 V differential true clock output  36 DIF6# OUT 0.7 V differential complementary clock output  37 OF6# Active low input for enabling DIF pair 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32   | DIF5         | OUT      | 0.7 V differential true clock output                                                                                                                                  |