# Low Dropout Linear Regulator Controller

The NCP102 is a low dropout linear regulator controller for applications requiring high-current and ultra low dropout voltages. The use of an external N-Channel MOSFET allows the user to adapt the device to a multitude of applications depending on system requirements for current and dropout voltage.

An extremely accurate 0.8 V  $(\pm 2\%)$  reference allows the implementation of sub 1 V voltage supplies. The reference is guaranteed over the complete supply and temperature ranges.

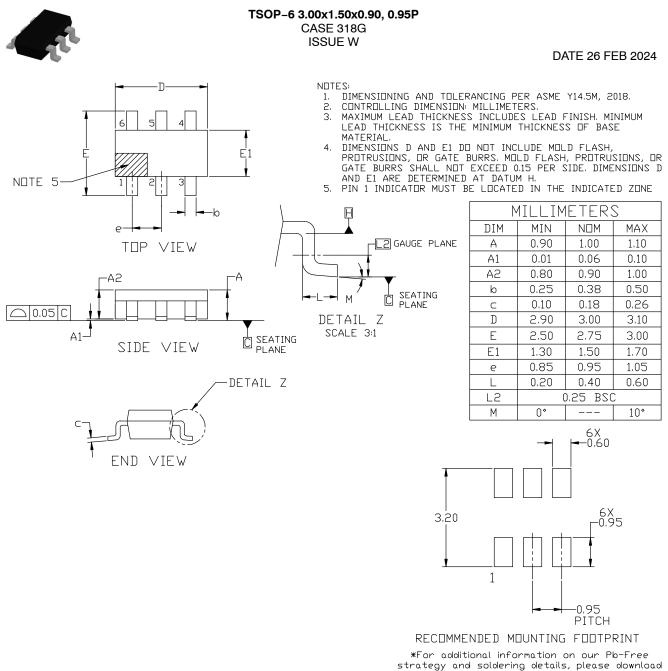

Other features of the NCP102 are a dedicated enable input, internally compensated error amplifier and an adjustable soft-start. A minimum drive capability of  $\pm 5$  mA provides fast transient response. The drive current is internally limited to protect the controller in case of an external MOSFET failure. The NCP102 is packaged in a space saving TSOP-6.

#### Features

- 4.5 V to 13.5 V Supply Voltage Range

- 0.8 V (±2%) Voltage Reference (Temperature and Process)

- Programmable Regulator Output Voltage Down to 0.8 V

- Drive Current Capability of  $> \pm 5$  mA

- MLCC and POSCAP Compatible

- Programmable Soft-Start

- Enable Active High

- Space Saving TSOP-6 Package

- RoHS Compliant Pb-Free Package

#### Applications

- Desktop and Laptops

- Computer Peripherals such as Graphics Cards

- Sub 1 V Power Supplies

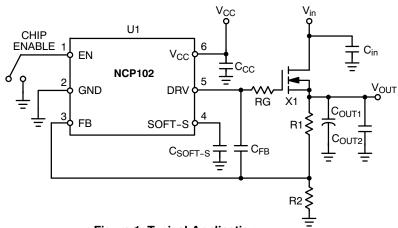

Figure 1. Typical Application

## **ON Semiconductor®**

http://onsemi.com

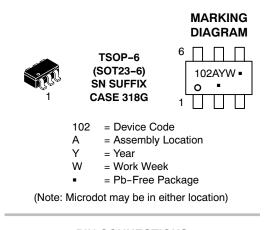

#### **ORDERING INFORMATION**

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| NCP102SNT1G | TSOP-6<br>(Pb-Free) | 3000/Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

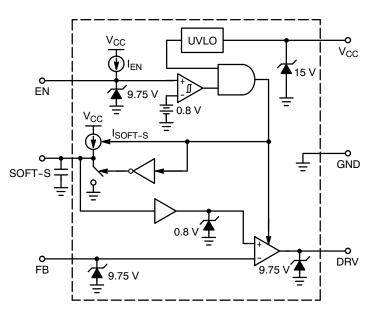

Figure 2. Representative Block Diagram

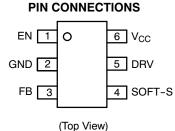

### **PIN FUNCTION DESCRIPTION**

| Pin | Symbol Name     | Description                                                                                                                                                                                 |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | EN              | Enable Input (Active High). Pull the EN pin below 0.8 V to disable the regulator and enter the standby mode operation.                                                                      |

| 2   | GND             | Ground                                                                                                                                                                                      |

| 3   | FB              | Inverting input of the error amplifier. The output voltage is sampled by means of a resistor divider and applied to this pin for regulation.                                                |

| 4   | SOFT-S          | Programmable soft-start. An internal current source charges the capacitor connected to this pin. The soft-<br>start period ends once the voltage of the soft-start capacitor reaches 0.8 V. |

| 5   | DRV             | Gate drive for external N-Channel MOSFET. It is also the buffered output of the error amplifier.                                                                                            |

| 6   | V <sub>CC</sub> | Power supply voltage input. Operating voltage range is from 4.5 to 13.5 V. A decoupling capacitor to GND should be used. A minimum of 0.1 $\mu$ F is recommended.                           |

#### **MAXIMUM RATINGS** ( $T_A = 25^{\circ}C$ , unless otherwise noted)

| Rating                                                                                                                         | Symbol                                     | Value               | Unit    |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|---------|

| Main Supply Input Voltage<br>Main Supply Input Current                                                                         | V <sub>CC</sub><br>I <sub>CC</sub>         | -0.3 to 15<br>100   | V<br>mA |

| Enable Voltage<br>Enable Current                                                                                               | V <sub>EN</sub><br>I <sub>EN</sub>         | -0.3 to 9.75<br>100 | V<br>mA |

| Soft-Start Voltage<br>Soft-Start Current                                                                                       | V <sub>SOFT-S</sub><br>I <sub>SOFT-S</sub> | -0.3 to 9.75<br>100 | V<br>mA |

| Drive Voltage<br>Drive Current                                                                                                 | V <sub>DRV</sub><br>I <sub>DRV</sub>       | -0.3 to 9.75<br>100 | V<br>mA |

| Feedback Voltage<br>Feedback Current                                                                                           | V <sub>FB</sub><br>I <sub>FB</sub>         | -0.3 to 9.75<br>100 | V<br>mA |

| Thermal Resistance, Junction-to-Ambient<br>(0.36 sq in Printed Circuit Copper Clad)<br>(1.0 sq in Printed Circuit Copper Clad) | R <sub>θJA</sub>                           | 230<br>200          | °C/W    |

| Power Dissipation (T <sub>A</sub> = 25°C, 2 oz Cu, 0.36 sq in Printed Circuit Copper Clad)                                     | PD                                         | 0.4                 | W       |

| Storage Temperature Range                                                                                                      | T <sub>stg</sub>                           | -65 to 150          | °C      |

| Operating Junction Temperature Range                                                                                           | Τ <sub>J</sub>                             | -40 to 125          | °C      |

| Reflow Temperature 10 seconds                                                                                                  | T <sub>reflow</sub>                        | 260                 | °C      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device series contains ESD protection and exceeds the following tests:

Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22-A114

Machine Model (MM) ±200 V per JEDEC standard: JESD22-A115

2. Latch-up current maximum rating: ±100 mA per JEDEC standard: JESD78.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> = 12 V, V <sub>EN</sub> = 1 V, V <sub>DRV</sub> = V <sub>FB</sub> , V <sub>SS</sub> = open, C <sub>CC</sub> = 0.1 $\mu$ F. For typical values T <sub>J</sub> = 25°C. |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| For min/max values, $T_J = -40^{\circ}$ C to 125°C, unless otherwise noted)                                                                                                                                             |  |

| Parameter                                                | Condition                                                                                                                                                                        |                                                  | Min         | Тур         | Max         | Unit |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------|-------------|-------------|------|

| POWER SUPPLY                                             |                                                                                                                                                                                  |                                                  |             |             |             |      |

| Supply Voltage                                           |                                                                                                                                                                                  | V <sub>CC</sub>                                  | 4.5         | -           | 13.5        | V    |

| Supply Current                                           | V <sub>CC</sub> = 5 V<br>V <sub>CC</sub> = 12 V                                                                                                                                  | I <sub>CC1</sub><br>I <sub>CC2</sub>             | -           | 1.4<br>1.8  | 3.2<br>3.2  | mA   |

| V <sub>CC</sub> Startup Voltage                          | V <sub>CC</sub> increasing                                                                                                                                                       | V <sub>CC(on)</sub>                              | 4.0         | 4.2         | 4.5         | V    |

| V <sub>CC</sub> Turn Off Voltage                         | V <sub>CC</sub> decreasing                                                                                                                                                       | V <sub>CC(off)</sub>                             | 3.8         | 4.0         | 4.4         | V    |

| V <sub>CC</sub> Hysteresis                               | V <sub>CC(on)</sub> - V <sub>CC(off)</sub>                                                                                                                                       | V <sub>CC(hys)</sub>                             | 0.10        | 0.24        | 0.30        | V    |

| Standby Current                                          | $V_{\text{EN}} = 0 \text{ V}, V_{\text{CC}} = 5 \text{ V}$ $V_{\text{EN}} = 0 \text{ V}, V_{\text{CC}} = 12 \text{ V}$                                                           | I <sub>CC(off1)</sub><br>I <sub>CC(off2)</sub>   | -           | 0.3<br>0.48 | 0.8<br>1.5  | mA   |

| ERROR AMPLIFIER                                          |                                                                                                                                                                                  |                                                  |             |             | -           |      |

| Input Bias Current                                       | V <sub>FB</sub> = 1.0 V                                                                                                                                                          | I <sub>FB</sub>                                  | -1.0        | -           | 1.0         | μΑ   |

| Open Loop DC Gain (Note 3)                               |                                                                                                                                                                                  | A <sub>v</sub>                                   | 55          | 70          | -           | dB   |

| Unity Gain Bandwidth                                     | $V_{FB} = V_{DRV}$                                                                                                                                                               | BW                                               | -           | 0.7         | -           | MHz  |

| Power Supply Rejection Ratio (Note 3)                    | V <sub>CC</sub> = 12 V, 100 Hz                                                                                                                                                   | PSRR                                             | 50          | -           | -           | dB   |

| DRIVE                                                    |                                                                                                                                                                                  |                                                  |             |             |             |      |

| Sink Current                                             | $V_{DRV} = 6 V, V_{FB} = 1 V$<br>$V_{DRV} = 2.5 V, V_{CC} = 5 V$<br>$V_{FB} = 1 V$                                                                                               | I <sub>DRV(SNK1)</sub><br>I <sub>DRV(SNK2)</sub> | 5.0<br>5.0  | -           | -           | mA   |

| Source Current                                           |                                                                                                                                                                                  | I <sub>DRV(SRC1)</sub><br>I <sub>DRV(SRC2)</sub> | 5.0<br>5.0  | -           | -           | mA   |

| Output Voltage Low State<br>High State                   | $\begin{split} I_{DRV} &= 5 \text{ mA}, \text{ V}_{FB} = 1 \text{ V} \\ I_{DRV} &= 5 \text{ mA}, \text{ V}_{FB} = 0.6 \text{ V}, \\ \text{ V}_{CC} &= 9.5 \text{ V} \end{split}$ | V <sub>DRV(low)</sub><br>V <sub>DRV(high)</sub>  | -<br>9.0    | -           | 0.5<br>-    | V    |

| Drive Current Under Fault Conditions $T_J = 25^{\circ}C$ | $\label{eq:VDRV} \begin{array}{l} V_{DRV} = 0 \ V, \ V_{FB} = 0.6 \ V \\ V_{DRV} = \text{open}, \ V_{FB} = 0.6 \ V \end{array}$                                                  | I <sub>DRV(MAX1)</sub><br>I <sub>DRV(MAX2)</sub> | -           |             | 45<br>40    | mA   |

| SOFT-START                                               |                                                                                                                                                                                  |                                                  |             |             |             |      |

| Source Current                                           | V <sub>SOFT-S</sub> = 1 V                                                                                                                                                        | I <sub>SOFT-S</sub>                              | 3.5         | 4.5         | 6.2         | μA   |

| ENABLE                                                   |                                                                                                                                                                                  |                                                  |             |             |             |      |

| Source Current                                           |                                                                                                                                                                                  | I <sub>EN</sub>                                  | 5.0         | 10          | 15          | μA   |

| Input Threshold Voltage<br>On State<br>Off State         | V <sub>EN</sub> Increasing<br>V <sub>EN</sub> Decreasing                                                                                                                         | V <sub>EN(on)</sub><br>V <sub>EN(off)</sub>      | 0.7<br>0.66 | 0.8<br>0.77 | 0.9<br>0.88 | V    |

| Threshold Voltage Hysteresis                             | V <sub>EN(on)</sub> – V <sub>EN(off)</sub>                                                                                                                                       | V <sub>EN(hys)</sub>                             | -           | 35          | -           | mV   |

| REFERENCE                                                |                                                                                                                                                                                  | -                                                | -           | -           | -           |      |

| Reference Voltage                                        | $V_{CC} = 5 V, V_{CC} = 12 V$                                                                                                                                                    | V <sub>REF</sub>                                 | 0.784       | 0.8         | 0.816       | V    |

|                                                          |                                                                                                                                                                                  |                                                  |             |             |             | ·    |

3. Guaranteed by design.

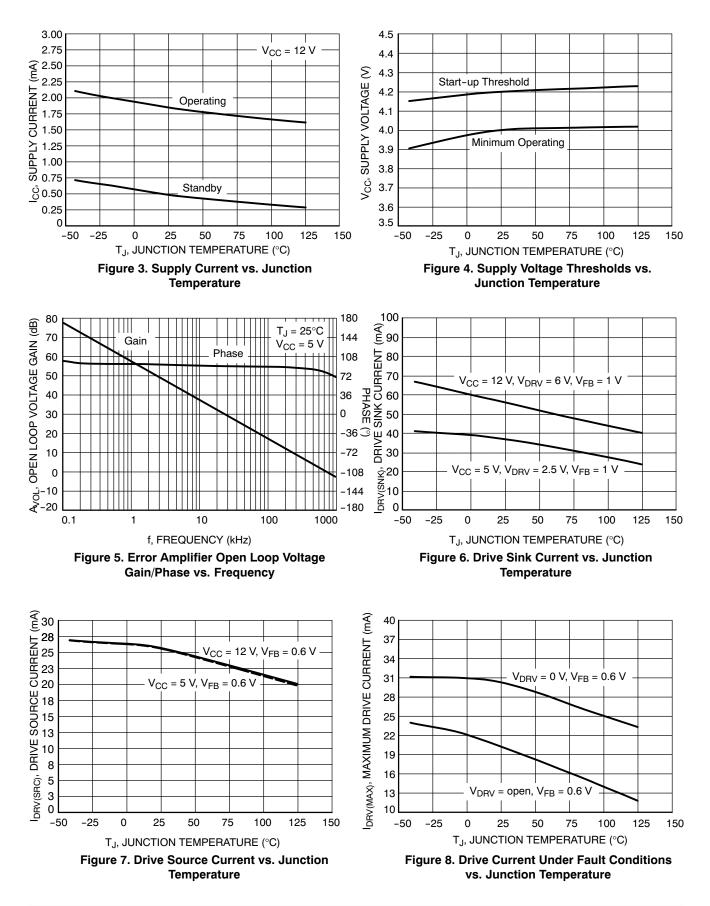

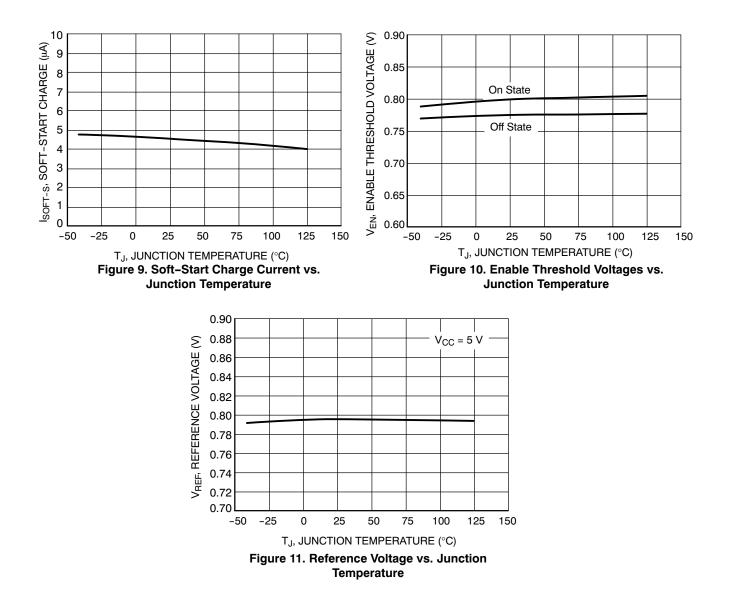

### **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS**

#### DETAILED OPERATING DESCRIPTION

The NCP102 is a low dropout linear regulator controller for applications requiring high-current and ultra low dropout voltages. The use of an external N-Channel MOSFET allows the user to adapt the device to a multitude of applications depending on system requirements for current and dropout voltage.

An extremely accurate 0.8 V ( $\pm 2\%$ ) reference allows the implementation of sub 1 V voltage supplies. The reference is guaranteed over the complete supply and temperature ranges.

Other features of the NCP102 are a dedicated enable input, internally compensated error amplifier and an adjustable soft-start. A minimum drive capability of  $\pm 5$  mA provides fast transient response. The drive current is internally limited to protect the controller in case of an external MOSFET failure. The NCP102 is packaged in a space saving TSOP-6.

#### SUPPLY VOLTAGE

The NCP102 supply voltage range is between 4.5 V and 13.5 V. The controller is enabled once the supply voltage exceeds its minimum supply threshold, typically 4.5 V. The minimum operating voltage is reduced to 4.2 V (typical) once the controller is enabled to provide noise immunity.

A bypass capacitor is required on the  $V_{CC}$  pin to provide charge storage during power up and transient events. A minimum of 0.1  $\mu$ F is recommended.

#### **DRIVE OUTPUT**

A powerful error amplifier (EA) capable of driving an external MOSFET is built into the NCP102. The output of the error amplifier is connected to the DRV pin. It has a minimum drive current capability of  $\pm 5$  mA providing a fast transient response.

The EA is biased directly from  $V_{CC}$ . The DRV voltage follows  $V_{CC}$  up and it is internally clamped to 9.75 V (typ.). This allows the use of external MOSFETs with a maximum gate voltage of 12 V.

The DRV current is provided directly from  $V_{CC}$ . Therefore, the  $V_{CC}$  capacitor should be large enough to maintain a constant  $V_{CC}$  during power up and transients. Otherwise, the supply voltage may collapse reaching the controller undervoltage lockout threshold.

#### **INTERNAL REFERENCE**

The internal 0.8 V reference facilitates the implementation of sub 1 V supplies required in modern computing equipment. The internal reference is trimmed during manufacturing to obtain better than  $\pm 2\%$  accuracy over the complete operating range.

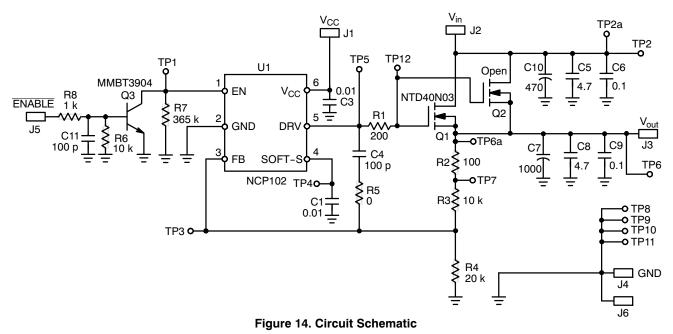

The output voltage,  $V_{out}$ , is programmed using a resistor divider (R1 and R2) as shown in Figure 1.

The resistor divider senses the output voltage and compares it to the internal 0.8 V reference.

Equation 1 relates the output voltage to the internal reference voltage and external resistors R1 and R2.

$$V_{out} = V_{REF} \cdot \left(\frac{R1 + R2}{R2}\right)$$

(eq. 1)

#### ERROR AMPLIFIER

The NCP102 has a wide bandwidth error amplifier. It allows the user to implement a wide bandwidth feedback loop resulting in better transient response and lower system cost. It requires the user to compensate the system. A narrow bandwidth error amplifier usually does not require external compensation but it requires more output capacitance to meet typical transient requirements.

The output of the error amplifier is available for frequency compensation. A capacitor ( $C_{COMP}$ ) can be placed between the DRV and FB pins. In most cases the resistor is not needed. The uncompensated error amplifier dominant pole is approximately 1.65 Hz. Any external capacitance between the DRV and FB pins reduces the dominant pole frequency due to the Miller multiplication effect. Equation 2 relates the dominant pole frequency to  $C_{COMP}$

$$f_{pole} = 6.7016 \cdot C_{COMP}^{-0.846}$$

(eq. 2)

#### EXTERNAL ENABLE

The EN input allows the NCP102 to be remotely enabled. An internal 10  $\mu$ A (typ.) current source pulls up the EN voltage. The EN pin is internally pulled to V<sub>CC</sub> or 9.5 V, whichever is lower.

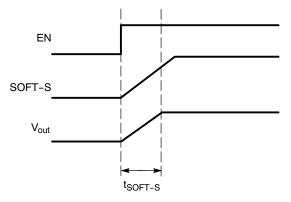

The controller is enabled once the EN pin voltage exceeds 0.8 V (typ.). The controller is disabled by pulling down on the EN pin. Figure 12 shows the relationship between enable and soft-start.

#### Figure 12. Relationship Between Enable and Soft-Start

The EN pin can be connected to  $V_{CC}$  if the enable feature is not used. If connected to  $V_{CC}$  and  $V_{CC}$  is higher than 9.5 V a resistor in series should be used to limit the current into the EN pin as the pin is internally clamped to 9.5 V. A minimum of 40 k $\Omega$  is recommended.

#### SOFT-START

Soft-start reduces inrush current and overshoot of the output voltage. The adjustable soft-start built into the NCP102 allows the user to select the optimum soft-start time for the application. The soft-start time is set with a capacitor from the SOFT-S pin to ground.

Soft-start is achieved by controlling the slope of the DRV voltage based on the slope of the soft-start capacitor voltage,  $C_{SOFT-S}$ . The capacitor is charged to  $V_{CC}$  with a constant 4.5  $\mu$ A (typ.) current source,  $I_{SOFT-S}$ . This results in a linear charge of the soft-start capacitor and thus the output voltage. The soft-start period,  $t_{SOFT-S}$ , ends once the capacitor voltage reaches 0.8 V (typ). The soft-start capacitor is calculated using Equation 3.

$$t_{SOFT-S} = \left(\frac{c_{SOFT-S} \cdot 0.8}{I_{SOFT-S}}\right)$$

(eq. 3)

The soft-start capacitor is internally pulled to GND when  $V_{CC}$  is not within its operating range or the controller is disabled using the EN pin.

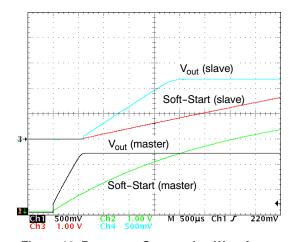

#### POWER SEQUENCING

Power sequencing can be easily implemented using the SOFT-S and EN pins. This is achieved by directly connecting the SOFT-S pin of the master controller to the EN pin of the slave controller. If  $V_{CC}$  is above 9.5 V a resistor divider is required to limit the voltage on the EN pin because the pin is internally clamped to 9.5 V. Figure 13 shows the timing waveforms of the master and slave controllers.

Figure 13. Power-up Sequencing Waveforms

Power sequencing will affect the soft-start time calculated using Equation 3 because the soft-start capacitor charge current is now increased by the enable charge current. The soft-start time is calculated using Equation 3 by replacing  $I_{SOFT-S}$  with the sum of  $I_{EN}$  and  $I_{SOFT-S}$ .

#### **APPLICATION INFORMATION**

ON Semiconductor provides an electronic design tool, a demonstration board and an application note to facilitate design using the NCP102 and to reduce development cycle time. All the tools can be downloaded at www.onsemi.com.

The electronic design tool allows the user to easily determine most of the system parameters of a linear regulator. The tool also evaluates the frequency response of the system. The demonstration board is designed to generate a 1.2 V/3 A voltage supply from a 1.8 V supply. The circuit schematic is shown in Figure 14 and the regulator design is described in Application Note AND8303.

The products described herein (NCP102), may be covered by one or more of the following U.S. patents: 7,307,476. There may be other patents pending.

strategy and soldering details, please download th e DN Semiconductor Soldering and Mounting Techniques Reference manual, SDLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                         | 98ASB14888C Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:                                                                                                                                                             | TSOP-6 3.00x1.50x0.90, 0.95P                                                                                                                                                                    |  | PAGE 1 OF 2 |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves |                                                                                                                                                                                                 |  |             |  |  |

the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights of others.

#### TSOP-6 3.00x1.50x0.90, 0.95P CASE 318G **ISSUE W**

DATE 26 FEB 2024

#### GENERIC **MARKING DIAGRAM\***

XXX = Specific Device Code

= Pb-Free Package

= Date Code

XXX = Specific Device Code

А =Assembly Location

= Year

Υ W = Work Week

= Pb-Free Package .

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

М

.

| STYLE 1:                                                                                          | STYLE 2:                                                                                                      | STYLE 3:                | STYLE 4:                                                                                       | STYLE 5:                                                                                             | STYLE 6:         |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|

| PIN 1. DRAIN                                                                                      | PIN 1. EMITTER 2                                                                                              | PIN 1. ENABLE           | PIN 1. N/C                                                                                     | PIN 1. EMITTER 2                                                                                     | PIN 1. COLLECTOR |

| 2. DRAIN                                                                                          | 2. BASE 1                                                                                                     | 2. N/C                  | 2. V in                                                                                        | 2. BASE 2                                                                                            | 2. COLLECTOR     |

| 3. GATE                                                                                           | 3. COLLECTOR 1                                                                                                | 3. R BOOST              | 3. NOT USED                                                                                    | 3. COLLECTOR 1                                                                                       | 3. BASE          |

| 4. SOURCE                                                                                         | 4. EMITTER 1                                                                                                  | 4. Vz                   | 4. GROUND                                                                                      | 4. EMITTER 1                                                                                         | 4. EMITTER       |

| 5. DRAIN                                                                                          | 5. BASE 2                                                                                                     | 5. V in                 | 5. ENABLE                                                                                      | 5. BASE 1                                                                                            | 5. COLLECTOR     |

| 6. DRAIN                                                                                          | 6. COLLECTOR 2                                                                                                | 6. V out                | 6. LOAD                                                                                        | 6. COLLECTOR 2                                                                                       | 6. COLLECTOR     |

| STYLE 7:                                                                                          | STYLE 8:                                                                                                      | STYLE 9:                | STYLE 10:                                                                                      | STYLE 11:                                                                                            | STYLE 12:        |

| PIN 1. COLLECTOR                                                                                  | PIN 1. Vbus                                                                                                   | PIN 1. LOW VOLTAGE GATE | PIN 1. D(OUT)+                                                                                 | PIN 1. SOURCE 1                                                                                      | PIN 1. I/O       |

| 2. COLLECTOR                                                                                      | 2. D(in)                                                                                                      | 2. DRAIN                | 2. GND                                                                                         | 2. DRAIN 2                                                                                           | 2. GROUND        |

| 3. BASE                                                                                           | 3. D(in)+                                                                                                     | 3. SOURCE               | 3. D(OUT)-                                                                                     | 3. DRAIN 2                                                                                           | 3. I/O           |

| 4. N/C                                                                                            | 4. D(out)+                                                                                                    | 4. DRAIN                | 4. D(IN)-                                                                                      | 4. SOURCE 2                                                                                          | 4. I/O           |

| 5. COLLECTOR                                                                                      | 5. D(out)                                                                                                     | 5. DRAIN                | 5. VBUS                                                                                        | 5. GATE 1                                                                                            | 5. VCC           |

| 6. EMITTER                                                                                        | 6. GND                                                                                                        | 6. HIGH VOLTAGE GATE    | 6. D(IN)+                                                                                      | 6. DRAIN 1/GATE 2                                                                                    | 6. I/O           |

| STYLE 13:<br>PIN 1. GATE 1<br>2. SOURCE 2<br>3. GATE 2<br>4. DRAIN 2<br>5. SOURCE 1<br>6. DRAIN 1 | STYLE 14:<br>PIN 1. ANODE<br>2. SOURCE<br>3. GATE<br>4. CATHODE/DRAIN<br>5. CATHODE/DRAIN<br>6. CATHODE/DRAIN |                         | LE 16:<br>11. ANODE/CATHODE<br>2. BASE<br>3. EMITTER<br>4. COLLECTOR<br>5. ANODE<br>6. CATHODE | STYLE 17:<br>PIN 1. EMITTER<br>2. BASE<br>3. ANODE/CATHODE<br>4. ANODE<br>5. CATHODE<br>6. COLLECTOR |                  |

| DOCUMENT NUMBER: | 98ASB14888C Electronic versions are uncontrolled except when accessed directly from the Document Repository.   Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|

| DESCRIPTION:     | TSOP-6 3.00x1.50x0.90, 0.95P                                                                                                                                                                   |  | PAGE 2 OF 2 |  |

|                  |                                                                                                                                                                                                |  |             |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>