# Step-Up/Down/Inverting Switching Regulators, 1.5 A

# NCP3063, NCP3063B, NCV3063

The NCP3063 Series is a higher frequency upgrade to the popular MC34063A and MC33063A monolithic DC-DC converters. These devices consist of an internal temperature compensated reference, comparator, a controlled duty cycle oscillator with an active current limit circuit, a driver and a high current output switch. This series was specifically designed to be incorporated in Step-Down, Step-Up and Voltage-Inverting applications with a minimum number of external components.

#### **Features**

- Operation to 40 V Input

- Low Standby Current

- Output Switch Current to 1.5 A

- Output Voltage Adjustable

- Frequency Operation of 150 kHz

- Precision 1.5% Reference

- New Features: Internal Thermal Shutdown with Hysteresis Cycle-by-Cycle Current Limiting

- Pb-Free Packages are Available

#### **Applications**

- Step-Down, Step-Up and Inverting supply applications

- High Power LED Lighting

- Battery Chargers

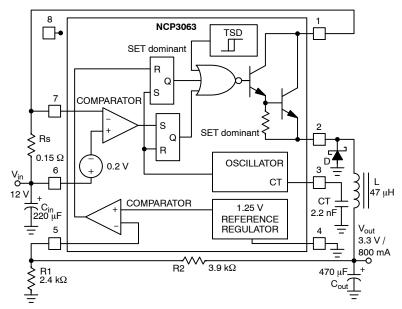

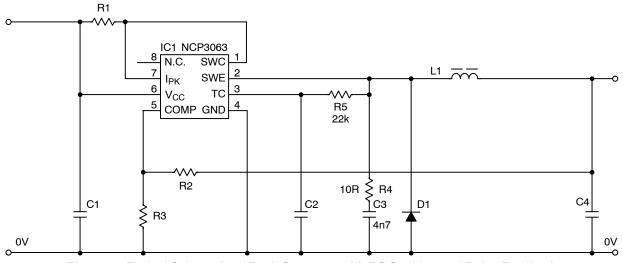

Figure 1. Typical Buck Application Circuit

1

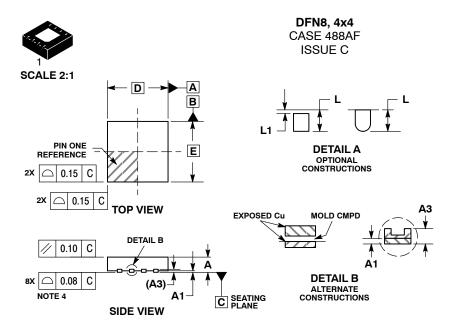

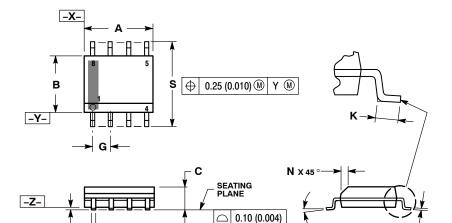

DFN-8 CASE 488AF

#### **MARKING DIAGRAMS**

NCP3063x = Specific Device Code

x = B

A = Assembly Location

L = Wafer Lot Y = Year W = Work Week ■ Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 16 of this data sheet.

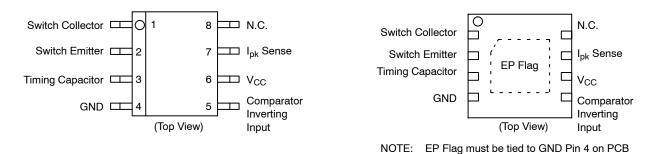

Figure 2. Pin Connections

Figure 3. Pin Connections

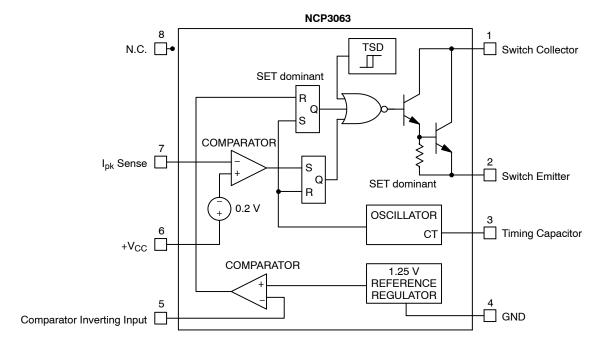

Figure 4. Block Diagram

#### **PIN DESCRIPTION**

| Pin No.        | Pin Name                             | Description                                                                                                                                                                                                |

|----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | Switch Collector                     | Internal Darlington switch collector                                                                                                                                                                       |

| 2              | Switch Emitter                       | Internal Darlington switch emitter                                                                                                                                                                         |

| 3              | Timing Capacitor<br>Oscillator Input | Timing Capacitor                                                                                                                                                                                           |

| 4              | GND                                  | Ground pin for all internal circuits                                                                                                                                                                       |

| 5              | Comparator<br>Inverting Input        | Inverting input pin of internal comparator                                                                                                                                                                 |

| 6              | V <sub>CC</sub>                      | Voltage Supply                                                                                                                                                                                             |

| 7              | I <sub>pk</sub> Sense                | Peak Current Sense Input to monitor the voltage drop across an external resistor to limit the peak current through the circuit                                                                             |

| 8              | N.C.                                 | Pin Not Connected                                                                                                                                                                                          |

| Exposed<br>Pad | Exposed Pad                          | The exposed pad beneath the package must be connected to GND (Pin 4). Additionally, using proper layout techniques, the exposed pad can greatly enhance the power dissipation capabilities of the NCP3063. |

### MAXIMUM RATINGS (measured vs. Pin 4, unless otherwise noted)

| Rating                                           | Symbol            | Value                         | Unit |

|--------------------------------------------------|-------------------|-------------------------------|------|

| V <sub>CC</sub> pin 6                            | V <sub>CC</sub>   | 0 to +40                      | V    |

| Comparator Inverting Input pin 5                 | V <sub>CII</sub>  | -0.2 to + V <sub>CC</sub>     | V    |

| Darlington Switch Collector pin 1                | V <sub>SWC</sub>  | 0 to +40                      | V    |

| Darlington Switch Emitter pin 2 (transistor OFF) | V <sub>SWE</sub>  | -0.6 to + V <sub>CC</sub>     | V    |

| Darlington Switch Collector to Emitter pin 1–2   | V <sub>SWCE</sub> | 0 to +40                      | V    |

| Darlington Switch Current                        | I <sub>SW</sub>   | 1.5                           | А    |

| I <sub>pk</sub> Sense Pin 7                      | V <sub>IPK</sub>  | -0.2 to V <sub>CC</sub> + 0.2 | V    |

| Timing Capacitor Pin 3                           | V <sub>TCAP</sub> | -0.2 to +1.4                  | V    |

#### POWER DISSIPATION AND THERMAL CHARACTERISTICS

| Rating                                                                          | Symbol                        | Value                   | Unit |

|---------------------------------------------------------------------------------|-------------------------------|-------------------------|------|

| SOIC-8 Thermal Resistance, Junction-to-Air Thermal Resistance, Junction-to-Case | $R_{	heta JA} \ R_{	heta JC}$ | 180<br>45               | °C/W |

| DFN-8 Thermal Resistance, Junction-to-Air                                       | $R_{	hetaJA}$                 | 80                      | °C/W |

| Storage Temperature Range                                                       | T <sub>STG</sub>              | -65 to +150             | °C   |

| Maximum Junction Temperature                                                    | T <sub>J MAX</sub>            | +150                    | °C   |

| Operating Junction Temperature Range (Note 3) NCP3063 NCP3063B, NCV3063         | TJ                            | 0 to +70<br>-40 to +125 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- This device series contains ESD protection and exceeds the following tests: Pin 1–8: Human Body Model 2000 V per AEC Q100–002; 003 or JESD22/A114; A115

- Machine Model Method 200 V

2. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

- 3. The relation between junction temperature, ambient temperature and Total Power dissipated in IC is  $T_J = T_A + R_\theta \cdot P_D$

- 4. The pins which are not defined may not be loaded by external signals

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5.0 \text{ V}$ ,  $T_J = T_{low}$  to  $T_{high}$  [Note 5], unless otherwise specified)

| Symbol                                    | Characteristic                                         | Conditions                                                                                                                                                           | Min   | Тур   | Max  | Unit |

|-------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|

| OSCILLATOR                                |                                                        |                                                                                                                                                                      |       | 1     | •    |      |

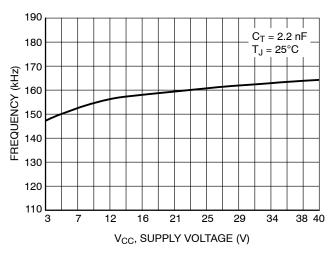

| f <sub>OSC</sub>                          | Frequency                                              | $(V_{Pin} 5 = 0 \text{ V, CT} = 2.2 \text{ nF,}  T_J = 25^{\circ}\text{C})$                                                                                          | 110   | 150   | 190  | kHz  |

| I <sub>DISCHG</sub> /<br>I <sub>CHG</sub> | Discharge to Charge Current Ratio                      | (Pin 7 to V <sub>CC</sub> , T <sub>J</sub> = 25°C)                                                                                                                   | 5.5   | 6.0   | 6.5  | -    |

| I <sub>DISCHG</sub>                       | Capacitor Discharging Current                          | (Pin 7 to V <sub>CC</sub> , T <sub>J</sub> = 25°C)                                                                                                                   |       | 1650  |      | μΑ   |

| I <sub>CHG</sub>                          | Capacitor Charging Current                             | (Pin 7 to $V_{CC}$ , $T_J = 25^{\circ}C$ )                                                                                                                           |       | 275   |      | μΑ   |

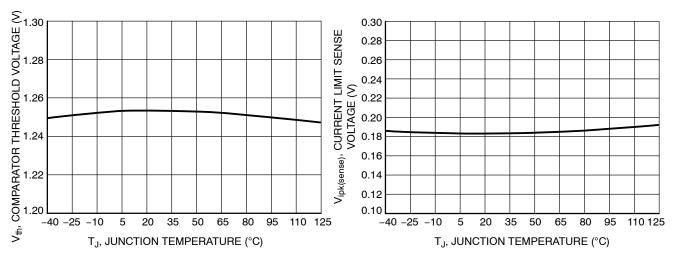

| V <sub>IPK(Sense)</sub>                   | Current Limit Sense Voltage                            | (T <sub>J</sub> = 25°C) (Note 6)                                                                                                                                     | 165   | 200   | 235  | mV   |

| OUTPUT SWI                                | TCH (Note 7)                                           |                                                                                                                                                                      |       |       | •    |      |

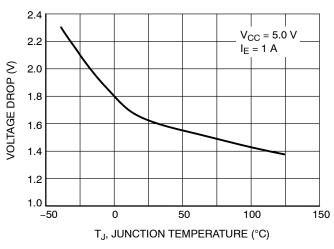

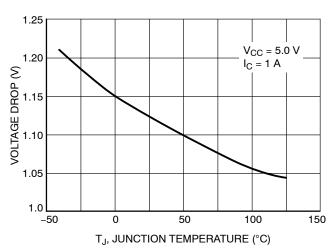

| V <sub>SWCE(DROP)</sub>                   | Darlington Switch Collector to<br>Emitter Voltage Drop | $(I_{SW} = 1.0 \text{ A, Pin 2 to GND,}  T_{J} = 25^{\circ}\text{C) (Note 7)}$                                                                                       |       | 1.0   | 1.3  | V    |

| I <sub>C(OFF)</sub>                       | Collector Off-State Current                            | (V <sub>CE</sub> = 40 V)                                                                                                                                             |       | 0.01  | 100  | μΑ   |

| COMPARATO                                 | R                                                      | <u>.</u>                                                                                                                                                             |       |       |      | •    |

| $V_{TH}$                                  | Threshold Voltage                                      | T <sub>J</sub> = 25°C                                                                                                                                                |       | 1.250 |      | V    |

|                                           |                                                        | NCP3063                                                                                                                                                              | -1.5  |       | +1.5 | %    |

|                                           |                                                        | NCP3063B, NCV3063                                                                                                                                                    | -2    |       | +2   | %    |

| REG <sub>LINE</sub>                       | Threshold Voltage Line Regulation                      | (V <sub>CC</sub> = 5.0 V to 40 V)                                                                                                                                    | -6.0  | 2.0   | 6.0  | mV   |

| I <sub>CII in</sub>                       | Input Bias Current                                     | $(V_{in} = V_{th})$                                                                                                                                                  | -1000 | -100  | 1000 | nA   |

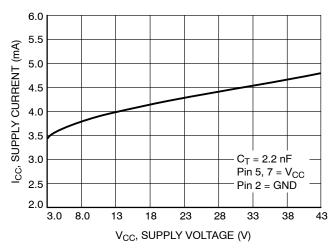

| TOTAL DEVIC                               | E                                                      |                                                                                                                                                                      |       |       | •    |      |

| I <sub>CC</sub>                           | Supply Current                                         | $(V_{CC} = 5.0 \text{ V to } 40 \text{ V},\\ CT = 2.2 \text{ nF, Pin } 7 = V_{CC},\\ V_{Pin} 5 > V_{th}, \text{ Pin } 2 = \text{GND},\\ \text{remaining pins open)}$ |       |       | 7.0  | mA   |

|                                           | Thermal Shutdown Threshold                             |                                                                                                                                                                      |       | 160   |      | °C   |

|                                           | Hysteresis                                             |                                                                                                                                                                      |       | 10    |      | °C   |

|                                           |                                                        |                                                                                                                                                                      |       |       |      |      |

NCP3063: T<sub>low</sub> = 0°C, T<sub>high</sub> = +70°C; NCP3063B, NCV3063: T<sub>low</sub> = -40°C, T<sub>high</sub> = +125°C

The V<sub>IPK(Sense)</sub> Current Limit Sense Voltage is specified at static conditions. In dynamic operation the sensed current turn-off value depends on comparator response time and di/dt current slope. See the Operating Description section for details.

Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient temperature as possible.

NCV prefix is for automotive and other applications requiring site and change control.

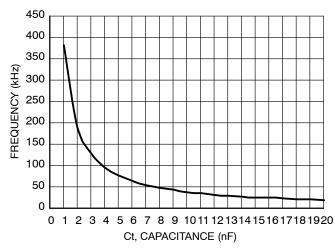

Figure 5. Oscillator Frequency vs. Oscillator Timing Capacitor

Figure 6. Oscillator Frequency vs. Supply Voltage

Figure 7. Emitter Follower Configuration Output Darlington Switch Voltage Drop vs. Temperature

Figure 8. Common Emitter Configuration Output Darlington Switch Voltage Drop vs. Temperature

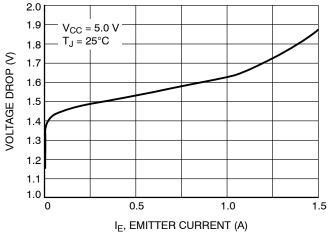

Figure 9. Emitter Follower Configuration Output Darlington Switch Voltage Drop vs. Emitter Current

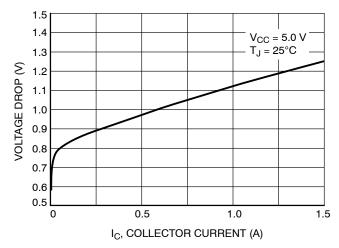

Figure 10. Common Emitter Configuration

Output Darlington Switch Voltage Drop vs.

Collector Current

Figure 11. Comparator Threshold Voltage vs. Temperature

Figure 12. Current Limit Sense Voltage vs. Temperature

Figure 13. Standby Supply Current vs. Supply Voltage

#### INTRODUCTION

The NCP3063 is a monolithic power switching regulator optimized for dc to dc converter applications. The combination of its features enables the system designer to directly implement step-up, step-down, and voltage-inverting converters with a minimum number of external components. Potential applications include cost sensitive consumer products as well as equipment for industrial markets. A representative block diagram is shown in Figure 4.

#### **Operating Description**

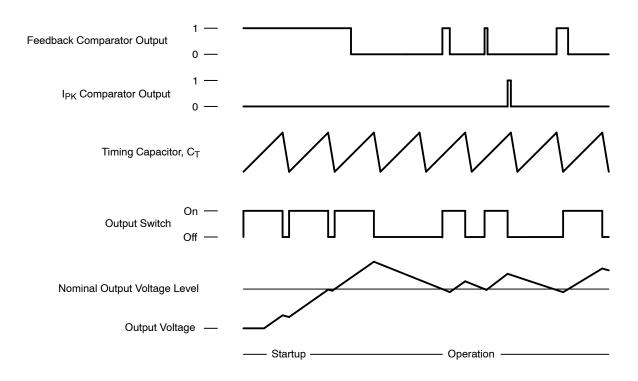

The NCP3063 is a hysteretic, dc-dc converter that uses a gated oscillator to regulate output voltage. In general, this mode of operation is somewhat analogous to a capacitor charge pump and does not require dominant pole loop compensation for converter stability. The Typical Operating Waveforms are shown in Figure 14. The output voltage waveform shown is for a step-down converter with the ripple and phasing exaggerated for clarity. During initial converter startup, the feedback comparator senses that the output voltage level is below nominal. This causes the output switch to turn on and off at a frequency and duty cycle

controlled by the oscillator, thus pumping up the output filter capacitor. When the output voltage level reaches nominal, the output switch next cycle turning on is inhibited. The feedback comparator will enable the switching immediately when the load current causes the output voltage to fall below nominal. Under these conditions, output switch conduction can be enabled for a partial oscillator cycle, a partial cycle plus a complete cycle, multiple cycles, or a partial cycle plus multiple cycles. (See AN920/D for more information).

#### Oscillator

The oscillator frequency and off–time of the output switch are programmed by the value selected for timing capacitor  $C_T$ . Capacitor  $C_T$  is charged and discharged by a 1 to 6 ratio internal current source and sink, generating a positive going sawtooth waveform at Pin 3. This ratio sets the maximum  $t_{ON}/(t_{ON}+t_{OFF})$  of the switching converter as 6/(6+1) or 0.857 (typical) The oscillator peak and valley voltage difference is 500 mV typically. To calculate the  $C_T$  capacitor value for required oscillator frequency, use the equations found in Figure 15. An Excel based design tool can be found at <a href="https://www.onsemi.com">www.onsemi.com</a> on the NCP3063 product page.

Figure 14. Typical Operating Waveforms

#### **Peak Current Sense Comparator**

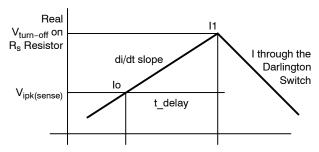

With a voltage ripple gated converter operating under normal conditions, output switch conduction is initiated by the Voltage Feedback comparator and terminated by the oscillator. Abnormal operating conditions occur when the converter output is overloaded or when feedback voltage sensing is lost. Under these conditions, the I<sub>pk</sub> Current Sense comparator will protect the Darlington output Switch. The switch current is converted to a voltage by inserting a fractional ohm resistor, RSC, in series with VCC and the Darlington output switch. The voltage drop across R<sub>SC</sub> is monitored by the Current Sense comparator. If the voltage drop exceeds 200 mV with respect to V<sub>CC</sub>, the comparator will set the latch and terminate output switch conduction on a cycle-by-cycle basis. This Comparator/Latch configuration ensures that the Output Switch has only a single on-time during a given oscillator cycle.

The  $V_{IPK(Sense)}$  Current Limit Sense Voltage threshold is specified at static conditions. In dynamic operation the sensed current turn-off value depends on comparator response time and di/dt current slope.

Real V<sub>turn-off</sub> on R<sub>sc</sub> resistor

$$V_{turn off} = V_{ipk(sense)} + Rs \cdot (t_{delay} \cdot di/dt)$$

Typical  $I_{pk}$  comparator response time t\_delay is 350 ns. The di/dt current slope is growing with voltage difference on the inductor pins and with decreasing inductor value.

It is recommended to check the real max peak current in the application at worst conditions to be sure that the max peak current will never get over the 1.5 A Darlington Switch Current max rating.

#### **Thermal Shutdown**

Internal thermal shutdown circuitry is provided to protect the IC in the event that the maximum junction temperature is exceeded. When activated, typically at 160°C, the Output Switch is disabled. The temperature sensing circuit is designed with 10°C hysteresis. The Switch is enabled again when the chip temperature decreases to at least 150°C threshold. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a replacement for proper heatsinking.

#### **Output Switch**

The output switch is designed in a Darlington configuration. This allows the application designer to operate at all conditions at high switching speed and low voltage drop. The Darlington Output Switch is designed to switch a maximum of 40 V collector to emitter voltage and current up to 1.5 A.

# **APPLICATIONS**

Figures 16 through 24 show the simplicity and flexibility of the NCP3063. Three main converter topologies are demonstrated with actual test data shown below each of the circuit diagrams.

Figure 15 gives the relevant design equations for the key parameters. Additionally, a complete application design aid for the NCP3063 can be found at <a href="https://www.onsemi.com">www.onsemi.com</a>.

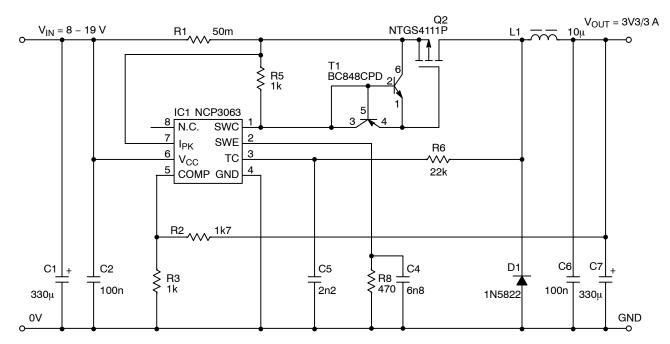

Figures 25 through 31 show typical NCP3063 applications with external transistors. This solution helps to

increase output current and helps with efficiency still keeping low cost bill of materials. Typical schematics of boost configuration with NMOS transistor, buck configuration with PMOS transistor and buck configuration with LOW  $V_{CE(sat)}$  PNP are shown.

Another advantage of using the external transistor is higher operating frequency which can go up to 250 kHz. Smaller size of the output components such as inductor and capacitor can be used then.

| (See Notes 9, 10, 11)    | Step-Down                                                                                 | Step-Up                                                        | Voltage-Inverting                                                           |

|--------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|

| ton<br>toff              | Vout + VF<br>Vin - VSWCE - Vout                                                           | $\frac{V_{out} + V_F - V_{in}}{V_{in} - V_{SWCE}}$             | V <sub>out</sub>   + V <sub>F</sub><br> V <sub>in</sub> - V <sub>SWCE</sub> |

| t <sub>on</sub>          | $\frac{\frac{\text{ton}}{\text{toff}}}{f\left(\frac{\text{ton}}{\text{toff}} + 1\right)}$ | $\frac{\frac{ton}{toff}}{f\left(\frac{ton}{toff} + 1\right)}$  | $\frac{\frac{ton}{toff}}{f\left(\frac{ton}{toff} + 1\right)}$               |

| C <sub>T</sub>           | Cī                                                                                        | $T = \frac{381.6 \cdot 10^{-6}}{f_{OSC}} - 343 \cdot 10^{-12}$ |                                                                             |

| I <sub>L(avg)</sub>      | lout                                                                                      | $I_{out}\left(\frac{t_{on}}{t_{off}} + 1\right)$               | $I_{out}\left(\frac{t_{on}}{t_{off}} + 1\right)$                            |

| I <sub>pk</sub> (Switch) | $I_{L(avg)} + \frac{\Delta I_{L}}{2}$                                                     | $I_{L(avg)} + \frac{\Delta I_L}{2}$                            | $I_{L(avg)} + \frac{\Delta I_L}{2}$                                         |

| R <sub>SC</sub>          | 0.20<br><sup>I</sup> pk (Switch)                                                          | 0.20<br>I <sub>pk</sub> (Switch)                               | 0.20<br><sup>I</sup> pk (Switch)                                            |

| L                        | $\left(\!\frac{V_{in} - V_{SWCE} - V_{out}}{\Delta I_L}\!\right) t_{on}$                  | $\left(\frac{V_{in} - V_{SWCE}}{\Delta I_L}\right) t_{on}$     | $\left(\frac{Vin - VSWCE}{\Delta I_L}\right) t_{on}$                        |

| V <sub>ripple(pp)</sub>  | $\Delta I_L \sqrt{\left(\frac{1}{8 f C_O}\right)^2 + (ESR)^2}$                            | $\approx \frac{tonlout}{CO} + \DeltaIL\cdotESR$                | $\approx \frac{tonlout}{CO} + \DeltalL\cdotESR$                             |

| V <sub>out</sub>         | $V_{TH}\left(\frac{R_2}{R_1} + 1\right)$                                                  | $V_{TH}\left(\frac{R_2}{R_1} + 1\right)$                       | $V_{TH}\left(\frac{R_2}{R_1} + 1\right)$                                    |

<sup>9.</sup>  $V_{SWCE}$  - Darlington Switch Collector to Emitter Voltage Drop, refer to Figures 7, 8, 9 and 10.

#### The Following Converter Characteristics Must Be Chosen:

V<sub>in</sub> – Nominal operating input voltage.

Vout - Desired output voltage.

Iout - Desired output current.

$\Delta I_L$  – Desired peak-to-peak inductor ripple current. For maximum output current it is suggested that  $\Delta I_L$  be chosen to be less than 10% of the average inductor current  $I_{L(avg)}$ . This will help prevent  $I_{pk\,(Switch)}$  from reaching the current limit threshold set by  $R_{SC}$ . If the design goal is to use a minimum inductance value, let  $\Delta I_L = 2(I_{L(avg)})$ . This will proportionally reduce converter output current capability.

*f* – Maximum output switch frequency.

$V_{ripple(pp)}$  – Desired peak-to-peak output ripple voltage. For best performance the ripple voltage should be kept to a low value since it will directly affect line and load regulation. Capacitor  $C_O$  should be a low equivalent series resistance (ESR) electrolytic designed for switching regulator applications.

Figure 15. Design Equations

<sup>10.</sup> V<sub>F</sub> - Output rectifier forward voltage drop. Typical value for 1N5819 Schottky barrier rectifier is 0.4 V.

<sup>11.</sup> The calculated t<sub>on</sub>/t<sub>off</sub> must not exceed the minimum guaranteed oscillator charge to discharge ratio.

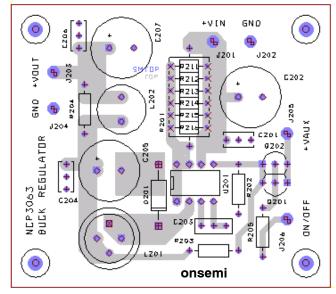

Figure 16. Typical Buck Application Schematic

### **Value of Components**

| Name | Value                           |

|------|---------------------------------|

| L201 | 47 μH, I <sub>sat</sub> > 1.5 A |

| D201 | 1 A, 40 V Schottky Rectifier    |

| C202 | 220 μF, 50 V, Low ESR           |

| C205 | 470 μF, 25 V, Low ESR           |

| C203 | 2.2 nF Ceramic Capacitor        |

| Name | Value                    |

|------|--------------------------|

| R201 | 150 mΩ, 0.5 W            |

| R202 | 2.40 kΩ                  |

| R203 | 3.90 kΩ                  |

| C201 | 100 nF Ceramic Capacitor |

| C202 | 100 nF Ceramic Capacitor |

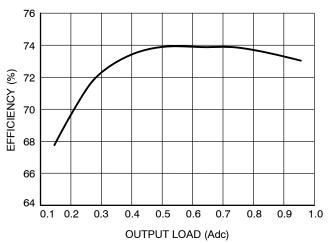

#### **Test Results**

| Test                  | Condition                                                 | Results               |

|-----------------------|-----------------------------------------------------------|-----------------------|

| Line Regulation       | V <sub>in</sub> = 9 V to 12 V, I <sub>o</sub> = 800 mA    | 8 mV                  |

| Load Regulation       | V <sub>in</sub> = 12 V, I <sub>o</sub> = 80 mA to 800 mA  | 9 mV                  |

| Output Ripple         | V <sub>in</sub> = 12 V, I <sub>o</sub> = 40 mA to 800 mA  | ≤ 85 mV <sub>pp</sub> |

| Efficiency            | V <sub>in</sub> = 12 V, I <sub>o</sub> = 400 mA to 800 mA | > 73%                 |

| Short Circuit Current | $V_{in}$ = 12 V, $R_{load}$ = 0.15 $\Omega$               | 1.25 A                |

Figure 17. Buck Demoboard Layout

Figure 18. Efficiency vs. Output Current for the Buck Demo Board at  $V_{in}$  = 12 V,  $V_{out}$  = 3.3 V,  $T_A$  = 25°C

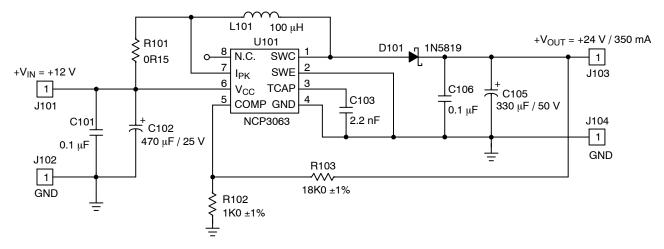

Figure 19. Typical Boost Application Schematic

#### **Value of Components**

| Name | Value                            |

|------|----------------------------------|

| L101 | 100 μH, I <sub>sat</sub> > 1.5 A |

| D101 | 1 A, 40 V Schottky Rectifier     |

| C102 | 470 μF, 25 V, Low ESR            |

| C105 | 330 μF, 50 V, Low ESR            |

| C103 | 2.2 nF Ceramic Capacitor         |

| Name | Value                    |

|------|--------------------------|

| R101 | 150 mΩ, 0.5 W            |

| R102 | 1.00 kΩ                  |

| R103 | 18.00 kΩ                 |

| C101 | 100 nF Ceramic Capacitor |

| C106 | 100 nF Ceramic Capacitor |

#### **Test Results**

| Test            | Condition                                                | Results                |

|-----------------|----------------------------------------------------------|------------------------|

| Line Regulation | V <sub>in</sub> = 9 V to 15 V, I <sub>o</sub> = 250 mA   | 2 mV                   |

| Load Regulation | V <sub>in</sub> = 12 V, I <sub>o</sub> = 30 mA to 350 mA | 5 mV                   |

| Output Ripple   | V <sub>in</sub> = 12 V, I <sub>o</sub> = 10 mA to 350 mA | ≤ 350 mV <sub>pp</sub> |

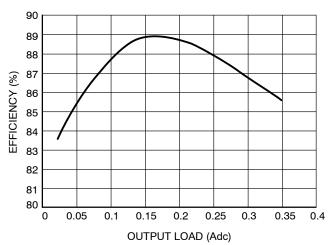

| Efficiency      | V <sub>in</sub> = 12 V, I <sub>o</sub> = 50 mA to 350 mA | > 85.5%                |

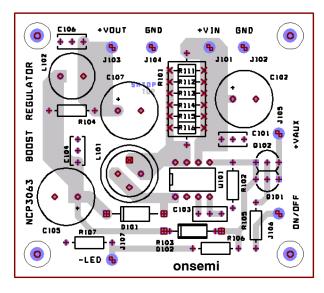

Figure 20. Boost Demoboard Layout

Figure 21. Efficiency vs. Output Current for the Boost Demo Board at  $V_{in}$  = 12 V,  $V_{out}$  = 24 V,  $T_A$  = 25°C

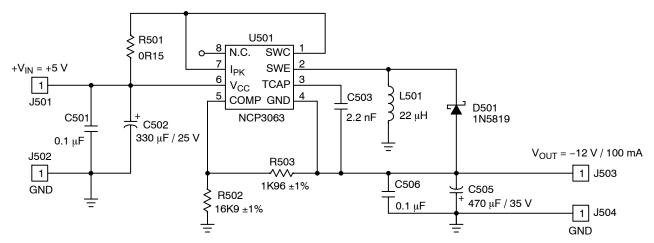

Figure 22. Typical Voltage Inverting Application Schematic

### **Value of Components**

| Name | Value                           |

|------|---------------------------------|

| L501 | 22 μH, I <sub>sat</sub> > 1.5 A |

| D501 | 1 A, 40 V Schottky Rectifier    |

| C502 | 330 μF, 25 V, Low ESR           |

| C505 | 470 μF, 35 V, Low ESR           |

| C503 | 2.2 nF Ceramic Capacitor        |

| Name | Value                    |

|------|--------------------------|

| R501 | 150 mΩ, 0.5 W            |

| R502 | 16.9 kΩ                  |

| R503 | 1.96 kΩ                  |

| C501 | 100 nF Ceramic Capacitor |

| C506 | 100 nF Ceramic Capacitor |

#### **Test Results**

| Test                  | Condition                                               | Results                |

|-----------------------|---------------------------------------------------------|------------------------|

| Line Regulation       | V <sub>in</sub> = 4.5 V to 6 V, I <sub>o</sub> = 50 mA  | 1.5 mV                 |

| Load Regulation       | V <sub>in</sub> = 5 V, I <sub>o</sub> = 10 mA to 100 mA | 1.6 mV                 |

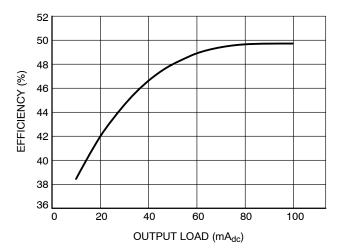

| Output Ripple         | V <sub>in</sub> = 5 V, I <sub>o</sub> = 0 mA to 100 mA  | ≤ 300 mV <sub>pp</sub> |

| Efficiency            | $V_{in} = 5 \text{ V}, I_{o} = 100 \text{ mA}$          | 49.8%                  |

| Short Circuit Current | $V_{in} = 5 \text{ V}, R_{load} = 0.15 \Omega$          | 0.885 A                |

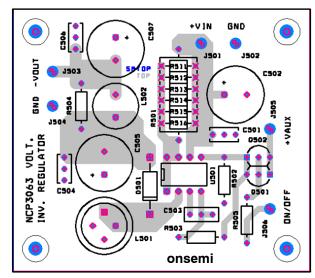

Figure 23. Voltage Inverting Demoboard Layout

Figure 24. Efficiency vs. Output Current for the Voltage Inverting Demo Board at  $V_{in}$  = +5 V,  $V_{out}$  = -12 V,  $T_A$  = 25°C

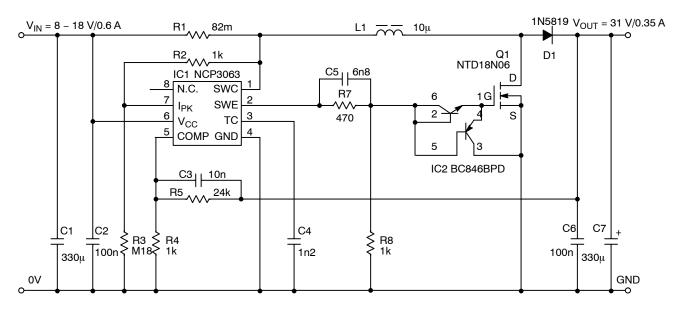

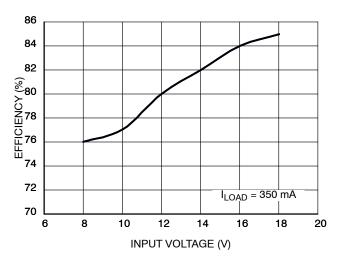

Figure 25. Typical Boost Application Schematic with External NMOS Transistor

Figure 26. Typical Efficiency for Application Shown in Figure 25.

External transistor is recommended in applications where wide input voltage ranges and higher power is required. The suitable schematic with an additional NMOS transistor and its driving circuit is shown in the Figure 25. The driving circuit is controlled from SWE Pin of the NCP3063 through frequency compensated resistor divider R7/R8. The driver IC2 is onsemi low cost dual NPN/PNP transistor BC846BPD. Its NPN transistor is connected as a super diode for charging the gate capacitance. The PNP transistor works as an emitter follower for discharging the gate capacitor. This configuration assures sharp driving edge between 50 – 100 ns as well as it limits power consumption of R7/R8 divider down to 50 mW. The output current limit is balanced by resistor R3. The fast switching with low R<sub>DS(on)</sub> NMOS transistor will achieve efficiencies up to 85% in automotive applications.

Figure 27. Typical Buck Application Schematic with External PMOS Transistor

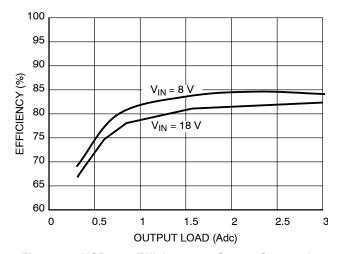

Figure 28. NCP3063 Efficiency vs. Output Current for Buck External PMOS at  $V_{out}$  = 3.3 V, f = 220 kHz,  $T_A$  = 25°C

Figure 27 shows typical buck configuration with external PMOS transistor. The principle of driving the Q2 gate is the same as shown in Figure 27.

Resistor R6 connected between TC and SWE pin provides a pulsed feedback voltage. It is recommended to use this pulsed feedback approach on applications with a wide input voltage range, applications with the input voltage over +12 V or applications with tighter specifications on output ripple. The suitable value of resistor R6 is between 10k-68k. The pulse feedback approach increases the operating frequency by about 20%. It also creates more regular switching waveforms with constant operating frequency which results in lower output ripple voltage and improved efficiency.

The pulse feedback resistor value has to be selected so that the capacitor charge and discharge currents as listed in the electrical characteristic table, are not exceeded. Improper selection will lead to errors in the oscillator operation. The maximum voltage at the TC Pin cannot exceed 1.4 V when implementing pulse feedback.

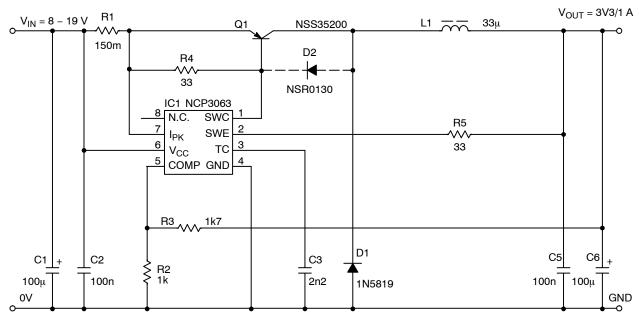

Figure 29. Typical Buck Application Schematic with External Low  $V_{\text{CE}}(\text{sat})$  PNP Transistor

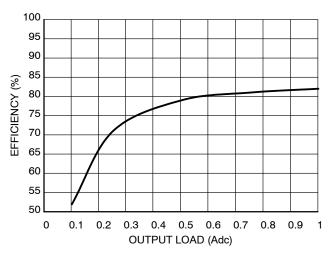

Figure 30. NCP3063 Efficiency vs. Output Current for External Low  $V_{CE(sat)}$  at  $V_{in}$  = +5 V, f = 160 kHz,  $T_A$  = 25°C

Typical application of the buck converter with external bipolar transistor is shown in the Figure 29. It is an ideal solution for configurations where the input and output voltage difference is small and high efficiency is required. NSS35200, the low  $V_{\text{CE}(\text{sat})}$  transistor from **onsemi** will be ideal for applications with 1 A output current, the input voltages up to 15 V and operating frequency 100-150~kHz. The switching speed could be improved by using desaturation diode D2.

Figure 31. Typical Schematic of Buck Converter with RC Snubber and Pulse Feedback

In some cases where there are oscillations on the output due to the input/output combination, output load variations or PCB layout a snubber circuit on the SWE Pin will help minimize the oscillation. Typical usage is shown in the Figure 31. C3 values can be selected between 2.2 nF and 6.8 nF and R4 can be from 10  $\Omega$  to 22  $\Omega$ .

#### **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup> |

|---------------|---------------------|-----------------------|

| NCP3063BMNTXG | DFN-8<br>(Pb-Free)  | 4000 / Tape & Reel    |

| NCP3063DR2G   | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCP3063BDR2G  | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCP3063MNTXG  | DFN-8<br>(Pb-Free)  | 4000 / Tape & Reel    |

| NCV3063DR2G*  | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCV3063MNTXG* | DFN-8<br>(Pb-Free)  | 4000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements.

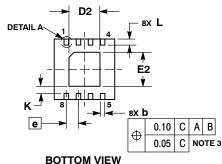

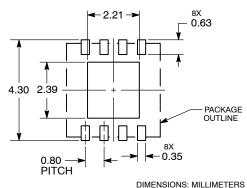

#### **SOLDERING FOOTPRINT\***

**DATE 15 JAN 2009**

#### NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- CONTROLLING DIMENSION. MICHINETERS.

DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30MM FROM TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED

- PAD AS WELL AS THE TERMINALS.

5. DETAILS A AND B SHOW OPTIONAL CON-STRUCTIONS FOR TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  | 0.00        | 0.05 |  |

| А3  | 0.20        | REF  |  |

| b   | 0.25        | 0.35 |  |

| D   | 4.00 BSC    |      |  |

| D2  | 1.91        | 2.21 |  |

| E   | 4.00 BSC    |      |  |

| E2  | 2.09        | 2.39 |  |

| е   | 0.80 BSC    |      |  |

| K   | 0.20        |      |  |

| Ĺ   | 0.30        | 0.50 |  |

| L1  |             | 0.15 |  |

#### **GENERIC MARKING DIAGRAM\***

XXXX = Specific Device Code Α = Assembly Location

= Wafer Lot Т Υ = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98AON15232D     | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED ( |             |

|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | DFN8, 4X4, 0.8P |                                                                                                                                                | PAGE 1 OF 1 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

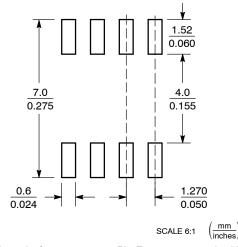

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

XS

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INC   | HES   |

|-----|-------------|------|-------|-------|

| DIM | MIN         | MAX  | MIN   | MAX   |

| Α   | 4.80        | 5.00 | 0.189 | 0.197 |

| В   | 3.80        | 4.00 | 0.150 | 0.157 |

| С   | 1.35        | 1.75 | 0.053 | 0.069 |

| D   | 0.33        | 0.51 | 0.013 | 0.020 |

| G   | 1.27 BSC    |      | 0.05  | 0 BSC |

| Н   | 0.10        | 0.25 | 0.004 | 0.010 |

| J   | 0.19        | 0.25 | 0.007 | 0.010 |

| K   | 0.40        | 1.27 | 0.016 | 0.050 |

| М   | 0 °         | 8 °  | 0 °   | 8 °   |

| N   | 0.25        | 0.50 | 0.010 | 0.020 |

| S   | 5.80        | 6.20 | 0.228 | 0.244 |

# **SOLDERING FOOTPRINT\***

0.25 (0.010) M Z Y S

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week W = Pb-Free Package

XXXXXX XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α

ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 3:

STYLE 2:

### **DATE 16 FEB 2011**

STYLE 4:

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE                                                                            | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1                              | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8. EMITTER  STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                   | 8. EMITTER, #1  STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | 8. COMMON CATHODE  STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1           |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON               | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                      |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                         |

| DOCUMENT NUMBER: | 98ASB42564B | Printed versions are uncontrolled except when accessed directly from the Document Repository.  Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                | PAGE 2 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

STYLE 1:

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales