# onsemi

## **Quad High-side Driver**

## NCV760040

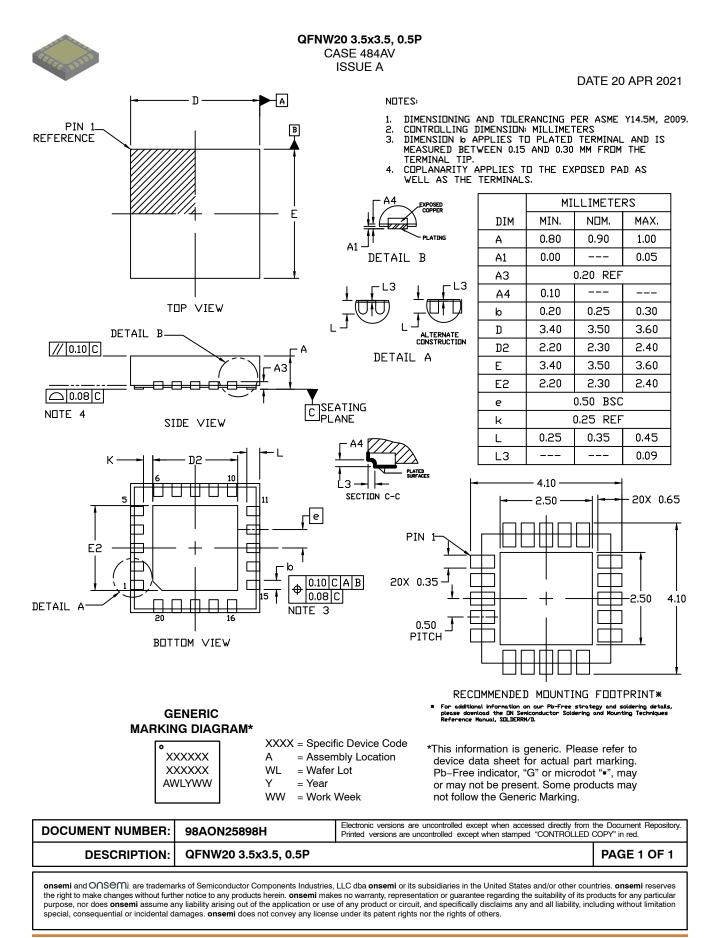

The NCV760040 is an automotive grade integrated driver with four high-side switches. The device features per-channel adjustable current limit and is protected for overtemperature conditions. Output control and diagnostic reporting is performed via  $I^2C$  bus. Current sense data is provided through  $I^2C$  in addition to a multiplexed analog current sense output pin. The NCV760040 is available in a QFNW20 3.5 x 3.5 mm step-cut package with wettable flanks and features an exposed pad for optimal thermal performance.

#### Features

- 4 High-side Channels

- 1.2 A Peak Current Per Channel

- RDS(ON) = 500 m $\Omega$  Typical, 1.0  $\Omega$  Max

- Global Enable Pin

- Low Quiescent Current in Sleep Mode

- Status Reporting via I<sup>2</sup>C and via Open-drain Fault Pin

- Current Sense Readout via I<sup>2</sup>C and via CS Pin

- Baseline Current Limit Set via External Resistor with Per-channel Current Limit Shift via I<sup>2</sup>C

- Overtemperature Shutdown

- Short to Battery Protection with Per-channel Reverse Current Blocking

- Open Load Detection

- Loss of Ground Protection

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### Applications

- Camera Switch

- LEDs, Sensors

- Advanced Driver Assistance Systems (ADAS)

- Infotainment

- Power Over Coax (PoC)

QFNW20 3.5x3.5, 0.5P CASE 484AV

#### MARKING DIAGRAM

NCV760040 = Specific Device Code

A = Assembly Location

- WL = Wafer Lot Y = Year

- WW = Work Week

#### **ORDERING INFORMATION**

| Device         | Package             | Shipping <sup>†</sup> |

|----------------|---------------------|-----------------------|

| NCV760040MWTXG | QFNW20<br>(Pb–Free) | 3000 / Tape<br>& Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

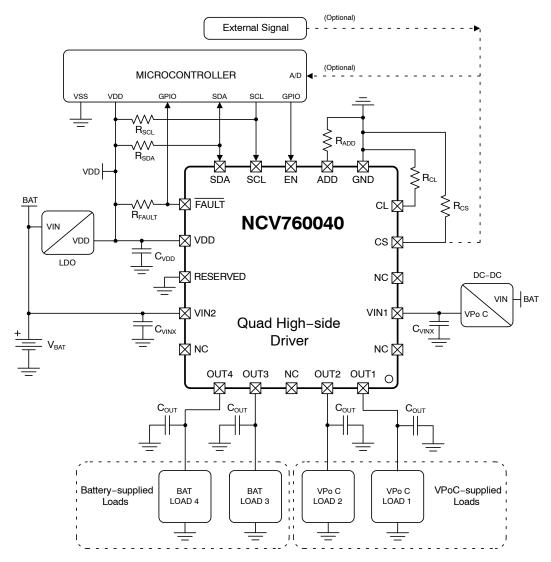

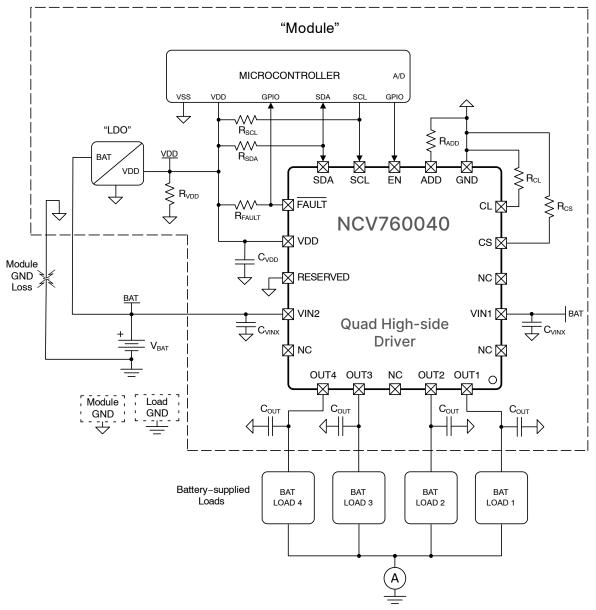

#### **Application Diagram**

Figure 1. Typical Application

| Reference          | Pin        | Value                           |

|--------------------|------------|---------------------------------|

| C <sub>VINx</sub>  | VIN1, VIN2 | 10 μF // 0.1 μF                 |

| C <sub>VDD</sub>   | VDD        | 0.1 μF                          |

| R <sub>ADD</sub>   | ADD        | 470 Ω to 100.0 kΩ               |

| R <sub>SDA</sub>   | SDA        | 4.7 kΩ                          |

| R <sub>SCL</sub>   | SCL        | 4.7 kΩ                          |

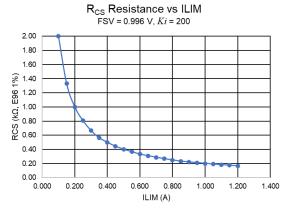

| R <sub>CS</sub>    | CS         | 330 Ω                           |

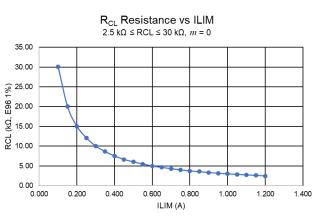

| R <sub>CL</sub>    | CL         | 2.5 k $\Omega$ to 30 k $\Omega$ |

| R <sub>FAULT</sub> | FAULT      | 4.7 kΩ                          |

| C <sub>OUT</sub>   | OUT1 – 4   | 0.1 µF                          |

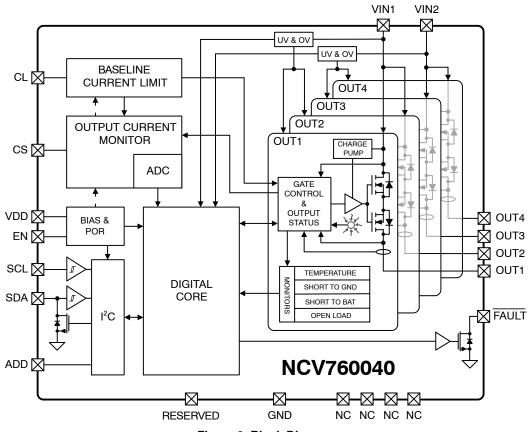

**Block Diagram**

Figure 2. Block Diagram

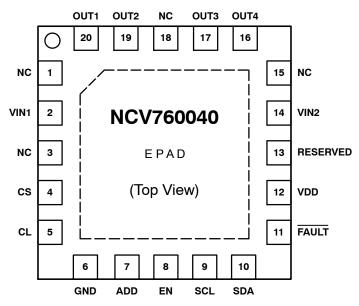

#### **QFNW20 Pinout Diagram**

Figure 3. Pinout – QFNW20 (Top View)

#### **Table 2. PIN FUNCTION DESCRIPTION**

| QFNW20 | Symbol      | Description                                                                                                      |

|--------|-------------|------------------------------------------------------------------------------------------------------------------|

| 1      | NC          | No Connection. Leave floating or connected to GND.                                                               |

| 2      | VIN1        | Power supply input for high-side outputs OUT1 and OUT2.                                                          |

| 3      | NC          | No Connection. Leave floating or connected to GND.                                                               |

| 4      | CS          | Current sense output. Connect a resistor to GND for ADC functionality.                                           |

| 5      | CL          | Baseline current limit setting. Connect a resistor to GND for ILIM functionality.                                |

| 6      | GND         | Ground. Common reference node and VDD power supply return.                                                       |

| 7      | ADD         | I <sup>2</sup> C address selection. Connect a resistor to GND to set the target device I <sup>2</sup> C address. |

| 8      | EN          | Active-high enable input. Wakes the device from sleep mode and enables the I <sup>2</sup> C bus.                 |

| 9      | SCL         | I <sup>2</sup> C clock input. Connect a pull-up resistor to VDD.                                                 |

| 10     | SDA         | I <sup>2</sup> C data input/open-drain output. Connect a pull-up resistor to VDD.                                |

| 11     | FAULT       | Active-low fault flag output. Connect a pull-up resistor to VDD; GND if unused.                                  |

| 12     | VDD         | Power supply input for analog and digital functionalities.                                                       |

| 13     | RESERVED    | Reserved for factory use. This pin shall be connected to GND.                                                    |

| 14     | VIN2        | Power supply input for high-side outputs OUT3 and OUT4.                                                          |

| 15     | NC          | No Connection. Leave floating or connected to GND.                                                               |

| 16     | OUT4        | High-side driver output 4.                                                                                       |

| 17     | OUT3        | High-side driver output 3.                                                                                       |

| 18     | NC          | No Connection. Leave floating or connected to GND.                                                               |

| 19     | OUT2        | High-side driver output 2.                                                                                       |

| 20     | OUT1        | High-side driver output 1.                                                                                       |

| EPAD   | Exposed Pad | Leave floating or connect to GND or to spreader plane for best thermal performance.                              |

#### Table 3. MAXIMUM RATINGS (Except as noted, voltages are with respect to GND.)

| Rating                                                                            | Symbol              | Min       | Max                   | Unit                  |    |

|-----------------------------------------------------------------------------------|---------------------|-----------|-----------------------|-----------------------|----|

| VINx Pin Voltage<br>AC: ISO 16750-2 § 4.6.4.2.3 Test B, 400 ms @ 25°C             | VinxMax             | -0.3      | 40                    | V                     |    |

| OUTx Pin Voltage                                                                  | VINx = 0 V          | VoutMax0  | -0.3                  | 40                    | V  |

|                                                                                   | VINx > 5 V          | VoutMax5  | Internally<br>Limited | 40                    | V  |

| VINx Pin to OUTx Pin Differential Voltage                                         | VINx = 0 V          | VrevMax0  | -40                   | 40                    | V  |

|                                                                                   | VINx > 5 V          | VrevMax5  | Internally            | y Limited             | V  |

| OUTx Pin Current                                                                  |                     | IoutMax   | -                     | Internally<br>Limited | А  |

| VDD Pin Voltage                                                                   | VddMax              | -0.3      | 5.5                   | V                     |    |

| Logic Pin Voltage (SDA, SCL, EN, ADD, FAULT)                                      |                     | VlogicMax | -0.3                  | 5.5                   | V  |

| Analog Pin Voltage (CL, CS)                                                       |                     | VcxMax    | -0.3                  | 5.5                   | V  |

| Logic Pin Current (SCL, EN, ADD, FAULT)                                           |                     | llogicMax | -10.0                 | 2.0                   | mA |

| Logic Pin Current (SDA)                                                           |                     | lioMax    | -10.0                 | 20                    | mA |

| Analog Pin Output Current (CL, CS)                                                |                     | IclMax    | -10.0                 | 2                     | mA |

|                                                                                   | lcsMax: t ≤ Tlatch0 | IcsMax    | -10.0                 | 12                    | mA |

| Operating Junction Temperature Range                                              |                     | Tj        | -40                   | 150                   | °C |

| Storage Temperature Range                                                         |                     | Tstr      | -55                   | 150                   | °C |

| Peak Reflow Soldering Temperature:<br>Pb-free 60 to 150 seconds at 217°C (Note 1) |                     | -         | -                     | 260                   | °C |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. See or download **onsemi**'s Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **Table 4. ATTRIBUTES**

| Characteristic                                                | Symbol         | Value             | Unit    |      |

|---------------------------------------------------------------|----------------|-------------------|---------|------|

| Short Circuit Reliability Characterization per AEC – Q100–012 |                | AECQ10x           | Grade A | -    |

| ESD Capability                                                |                |                   |         |      |

| Human Body Model per AEC-Q100-002                             | VINx, OUTx     | Vesd4k            | ≥±4.0   | kV   |

|                                                               | All Other Pins | Vesd2k            | ≥±2.0   | kV   |

| Charged Device Model per AEC-Q100-011                         |                | Vesd750           | ≥±750   | V    |

| Moisture Sensitivity Level                                    |                | MSL               | MSL1    | -    |

| Thermal Characterization Parameters                           |                |                   |         | °C/W |

| Junction-to-Ambient                                           | (Note 2)       | $R_{\theta JA}$   | 22.3    |      |

| Junction-to-Board                                             | (Note 2)       | $R\psi_{JB-EPAD}$ | 2.2     |      |

2. Based on a 4-layer, 1.6 mm thick PCB with 35 µm copper per layer using 9 thermal vias in exposed pad to internal layer 2 and to external layer 4 planes. Simulated for 0.4 W and 0.68 W per channel cases of simultaneous power dissipation.

#### Table 5. RECOMMENDED OPERATING CONDITIONS

| Parameter                                                             | Symbol   | Min  | Max  | Unit |

|-----------------------------------------------------------------------|----------|------|------|------|

| Supply Input Voltage                                                  | VINxOp   | 4.5  | 28   | V    |

| Digital Supply Input Voltage                                          | VDDOp    | 3.15 | 5.25 | V    |

| Logic Low Input Level                                                 | Vinl     | _    | 0.8  | V    |

| Logic High Input Level                                                | Vinh     | 2.0  | -    | V    |

| Address Confirmation Time (EN L $\rightarrow$ H, Note 4, Note 6)      | TADDconf | 350  | -    | μs   |

| Enable Release Time (EN H→L, Note 4, Note 7)                          | tENhl    | _    | 250  | μs   |

| I2C SCL Frequency                                                     | SCLfreq  | _    | 1.0  | MHz  |

| DC Output Current (Single Channel On, T <sub>J</sub> < 150°C, Note 2) | IxOp     | _    | 1.2  | А    |

| DC Output Current (All Channels On, $T_A \leq 125^{\circ}$ C, Note 2) | lxOp125  | _    | 529  | mA   |

| DC Output Current (All Channels On, $T_A \leq 105^{\circ}$ C, Note 2) | lxOp105  | _    | 710  | mA   |

| DC Output Current (All Channels On, $T_A \le 85^{\circ}C$ , Note 2)   | lxOp85   | _    | 854  | mA   |

| Operating Temperature                                                 | ТаОр     | -40  | 125  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

$\begin{array}{l} \textbf{Table 6. ELECTRICAL CHARACTERISTICS} \\ (-40^{\circ}C \leq T_J \leq 150^{\circ}C, \ 5 \ V \leq VINx \leq 18 \ V, \ 3.15 \ V \leq V_{DD} \leq 5.25 \ V, \ EN = V_{DD}, \ unless \ otherwise \ specified.) \ (Note \ 3) \end{array}$

| Characteristic                | Symbol      | Conditions                                                                                                                                                                                                                          | Min   | Тур      | Max        | Unit |

|-------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|------------|------|

| POWER SUPPLIES                |             |                                                                                                                                                                                                                                     |       |          |            |      |

| VDD Sleep Current             | lqVDD       | $\begin{array}{l} VDD = 5 \ V, \ EN = 0 \ V \\ -40^\circC \leq T_A < 125^\circC \\ T_A \geq 125^\circC \end{array}$                                                                                                                 | -     | 3.0<br>_ | 4.0<br>5.0 | μΑ   |

| VDD Active Current            | IVDD        | $\begin{array}{l} -40^\circ C \leq T_A \leq 125^\circ C \\ \text{VDD} = \text{EN} = 5 \text{ V, } \text{RCL} = 2.5 \text{ k}\Omega \\ \text{VIN1} = \text{VIN2} = 13.2 \text{ V} \\ \text{All Outputs On, I(OUTx)} = 0 \end{array}$ | -     | 2.6      | 4.0        | mA   |

| VDD Power-on Reset Threshold  | VDDpor_i    | VDD Increasing                                                                                                                                                                                                                      | 2.4   | 2.70     | 3.0        | V    |

|                               | VDDpor_d    | VDD Decreasing                                                                                                                                                                                                                      | 2.2   | 2.5      | 2.8        | V    |

| VDD Power-on Reset Hysteresis | VDDhys      |                                                                                                                                                                                                                                     | 50    | -        | -          | mV   |

| VINx Sleep Current            | lqVINx125   | VDD = EN = 0 V<br>VIN1 = VIN2 = 13.2 V<br>OUT1 = OUT2 = OUT3 = OUT4 = 0 V                                                                                                                                                           | -     | 1.0      | 5.0        | μΑ   |

| VINx Active Current           | lqVINx_sb   | $\begin{array}{l} EN = VDD,  VIN1 = VIN2 = 18 \; V \\ OUT1 = OUT2 = OUT3 = OUT4 = 0 \; V \\ RCL = 2.5 \; k\Omega,  All \; Outputs \; Off \end{array}$                                                                               | -     | 0.6      | 1.5        | mA   |

| VINx Undervoltage Threshold   | VINxUV      | VINx Decreasing                                                                                                                                                                                                                     | 2.9   | 3.5      | 3.9        | V    |

|                               |             | VINx Increasing                                                                                                                                                                                                                     | 3.1   | 3.7      | 4.1        |      |

| VINx Undervoltage Hysteresis  | VINxUVHys   |                                                                                                                                                                                                                                     | 0.100 | 0.200    | 0.350      | V    |

| VINx Overvoltage Threshold    | VINxOV      | VINx Increasing                                                                                                                                                                                                                     | 17.5  | 19.5     | 21.5       | V    |

|                               |             | VINx Decreasing                                                                                                                                                                                                                     | 16.2  | 18       | 19.8       |      |

| VINx Overvoltage Hysteresis   | VINxOVHys   |                                                                                                                                                                                                                                     | 0.5   | 1.5      | 2.5        | V    |

| DRIVER OUTPUT                 |             | ·                                                                                                                                                                                                                                   |       |          | -          |      |

| Output On-State Resistance    | RDSonHS     | VINx = 13.2 V, IOUT = 500 mA                                                                                                                                                                                                        | -     | 0.5      | 1.0        | Ω    |

| Output Leakage Current        | loutLkg13.2 | $ \begin{array}{l} \text{VINx} = 13.2 \text{ V}, \text{ OUTx} = 0 \text{ V} \\ -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 125^{\circ}\text{C} \\ \text{T}_{\text{A}} > 125^{\circ}\text{C} \end{array} $                     | -     |          | 1.0<br>5.0 | μΑ   |

$\begin{array}{l} \textbf{Table 6. ELECTRICAL CHARACTERISTICS} \\ (-40^{\circ}C \leq T_J \leq 150^{\circ}C, \ 5 \ V \leq VINx \leq 18 \ V, \ 3.15 \ V \leq V_{DD} \leq 5.25 \ V, \ EN = V_{DD}, \ unless \ otherwise \ specified.) \ (Note \ 3) \end{array}$

| DRIVER OUTPUT                                                    |                |                                                                                                                                                                                                         |        |       |            | Unit |

|------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------------|------|

|                                                                  |                |                                                                                                                                                                                                         |        |       |            |      |

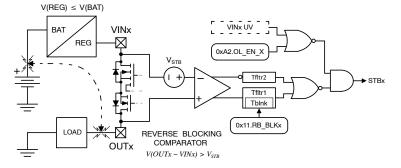

| Reverse Blocking<br>Leakage Current                              | loutLkgRvs13.2 | $ \begin{array}{l} \text{VINx} = 0 \text{ V, OUTx} = 13.2 \text{ V} \\ -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 125^{\circ}\text{C} \\ \text{T}_{\text{A}} > 125^{\circ}\text{C} \end{array} $ | -<br>- |       | 1.0<br>5.0 | μΑ   |

| Reverse Blocking Comparator                                      | V_STB          | VINx = 5 V, VOUTx – VINx, OUTx rising                                                                                                                                                                   | 90     | 300   | 1000       | mV   |

| Threshold                                                        |                | VINx = 5 V, OUTx falling                                                                                                                                                                                | _      | -500  | -          | mV   |

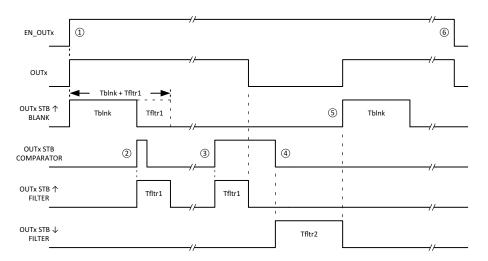

| Reverse Blocking Deglitch Time                                   | Tblnk          | Delay from OUTx activation to enable short to battery detection                                                                                                                                         | 8.0    | 10.0  | 12.0       | μs   |

|                                                                  | Tfltr1         | OUTx crossing rising threshold<br>to output deactivation                                                                                                                                                | 1.0    | 2.0   | 3.0        | μs   |

|                                                                  | Tfltr2         | OUTx crossing falling threshold<br>to output reactivation                                                                                                                                               | 8.0    | 10.0  | 12.0       | μs   |

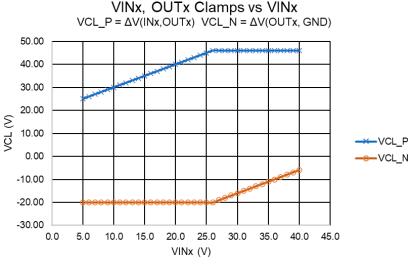

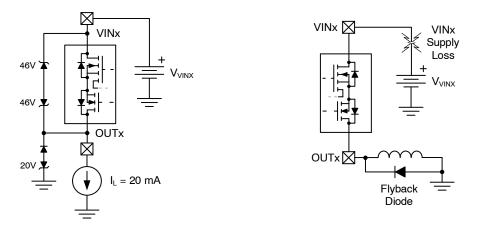

| VINx to OUTx Clamp                                               | VCL_P          | IL = 20 mA, VINx = 36 V<br>VCL_P = $\Delta V$ = VINx - OUTx                                                                                                                                             | 42     | 46    | 54         | ΔV   |

| OUTx to GND Clamp                                                | VCL_N          | IL = 20 mA, VINx = 13.2 V                                                                                                                                                                               | -25    | -20   | -16        | V    |

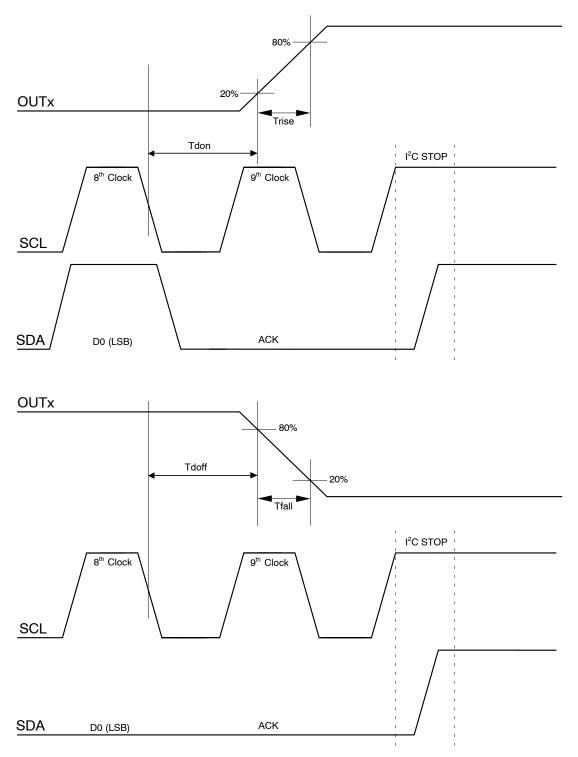

| DRIVER OUTPUT SWITCHING CHAP                                     |                | Figure 4, RCL = 2.5 k $\Omega$ )                                                                                                                                                                        |        |       |            |      |

| Turn On Delay Time                                               | Tdon           | VINx = 13.5 V, $R_L$ = 50 $\Omega$                                                                                                                                                                      | 15     | 20    | 35         | μs   |

| Turn Off Delay Time                                              | Tdoff          | VINx = 13.5 V, $R_L$ = 50 $\Omega$                                                                                                                                                                      | 10     | 20    | 30         | μs   |

| Rise Time                                                        | Trise          | VINx = 13.5 V, $R_L$ = 50 $\Omega$                                                                                                                                                                      | 20     | 40    | 60         | μs   |

| Fall Time                                                        | Tfall          | VINx = 13.5 V, $R_L$ = 50 $\Omega$                                                                                                                                                                      | 30     | 50    | 70         | μs   |

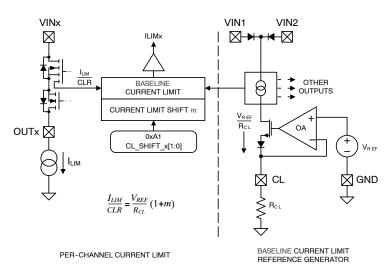

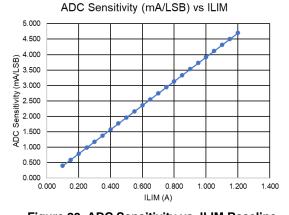

| CURRENT SENSE AND CURRENT L                                      | ІМІТ           |                                                                                                                                                                                                         |        |       |            |      |

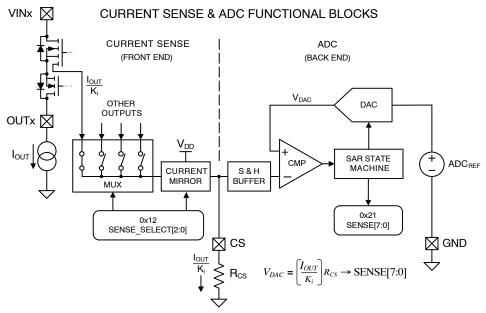

| Current Sense Ratio                                              | K0             | $25 \text{ mA} \le \text{IOUT} < 50 \text{ mA}$                                                                                                                                                         | -25%   | 200   | +25%       | -    |

| Current Sense Ratio                                              | K1             | $50 \text{ mA} \le \text{IOUT} < 100 \text{ mA}$                                                                                                                                                        | -12%   | 200   | +12%       | -    |

| Current Sense Ratio                                              | K2             | $100 \text{ mA} \le \text{IOUT} < 200 \text{ mA}$                                                                                                                                                       | -8%    | 200   | +8%        | -    |

| Current Sense Ratio                                              | КЗ             | 200 mA $\leq$ IOUT < 400 mA                                                                                                                                                                             | -7%    | 200   | +7%        | -    |

| Current Sense Ratio                                              | K4             | IOUT ≥ 400 mA                                                                                                                                                                                           | -6%    | 200   | +6%        | -    |

| Current Limit Shutdown Time                                      | Tlatch0        | LATCH = 0                                                                                                                                                                                               | 18     | 20    | 22         | ms   |

|                                                                  | Tlatch1        | LATCH = 1                                                                                                                                                                                               | 18     | 20    | 22         | μs   |

| Current Limit Ratio (Note 4)                                     | CLR            |                                                                                                                                                                                                         | _      | 5000  | -          | -    |

| Internal Voltage Reference                                       | Vref           |                                                                                                                                                                                                         | 0.540  | 0.600 | 0.660      | V    |

| Current Limit Accuracy (Note 5)                                  | CLacc1         | R <sub>CL</sub> = 30 kΩ                                                                                                                                                                                 | 85     | 107   | 130        | mA   |

|                                                                  | CLacc2         | R <sub>CL</sub> = 7.5 kΩ                                                                                                                                                                                | 368    | 400   | 432        | mA   |

|                                                                  | CLaccExt       | R <sub>CL</sub> = 2.5 kΩ                                                                                                                                                                                | 1040   | 1155  | 1270       | mA   |

| Current Limit Shift (Note 4)<br>R <sub>CL</sub> = 7.5 k $\Omega$ | CLshift0       | CL_SHIFT_x[1:0] = 0b00                                                                                                                                                                                  | -      | 0     | -          | %    |

| HCL - 7.3 K22                                                    | CLshift1       | CL_SHIFT_x[1:0] = 0b01                                                                                                                                                                                  | -      | 30    | -          | %    |

|                                                                  | CLshift2       | CL_SHIFT_x[1:0] = 0b02                                                                                                                                                                                  | _      | 60    | -          | %    |

|                                                                  | CLshift3       | CL_SHIFT_x[1:0] = 0b03                                                                                                                                                                                  | -      | 100   | -          | %    |

| THERMAL PROTECTION (Note 4)                                      |                |                                                                                                                                                                                                         |        |       |            |      |

| Thermal Warning             | Twr   | 120 | 140 | 170 | °C |

|-----------------------------|-------|-----|-----|-----|----|

| Thermal Warning Hysteresis  | TwHy  | -   | 20  | -   | °C |

| Thermal Shutdown            | Tsd   | 150 | 175 | 200 | °C |

| Thermal Shutdown Hysteresis | TsdHy | -   | 20  | -   | °C |

#### Table 6. ELECTRICAL CHARACTERISTICS

$(-40^{\circ}C \leq T_J \leq 150^{\circ}C, \ 5 \ V \leq VINx \leq 18 \ V, \ 3.15 \ V \leq V_{DD} \leq 5.25 \ V, \ EN = V_{DD}, \ unless \ otherwise \ specified.) \ (Note \ 3)$

|                                            |           |                                                   | , (   |       |       |      |

|--------------------------------------------|-----------|---------------------------------------------------|-------|-------|-------|------|

| Characteristic                             | Symbol    | Conditions                                        | Min   | Тур   | Max   | Unit |

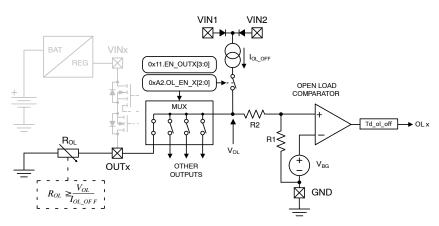

| OPEN LOAD DETECTION                        |           |                                                   |       |       |       |      |

| Off-state Open Load<br>Detection Threshold | Vol       | Diagnostic enabled,<br>EN_OUTx = 0                | 3     | 3.3   | 3.6   | V    |

| Off-state Open Load Source Current         | lol_off   | Diagnostic enabled,<br>EN_OUTx = 0                | 25    | 50    | 100   | μΑ   |

| Off-state Open Load Detection Delay        | Td_ol_off | $OUTx = Vol, OL = 0 \rightarrow 1$                | 8     | 10    | 12    | μs   |

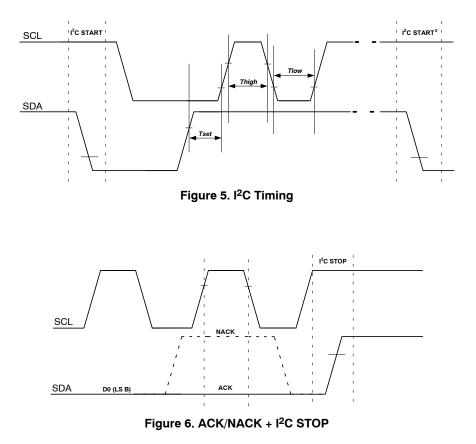

| I2C: SDA, SCL (Figures 5, 6)               |           |                                                   |       |       |       |      |

| Clock High Time                            | Thigh     |                                                   | 260   | -     | -     | ns   |

| Clock Low Time                             | Tlow      |                                                   | 500   | -     | -     | ns   |

| Data Setup Time                            | Tset      |                                                   | 50    | -     | -     | ns   |

| Bus Idle Time                              | Tbuf      | Time between a STOP and<br>a next START condition | 500   | -     | -     | ns   |

| Input Threshold High                       | Vih_I2C   | SCL, SDA increasing                               | 1.0   | 1.2   | 1.4   | V    |

| Input Threshold Hysteresis                 | Vi_I2Chys | SCL, SDA                                          | 0.100 | 0.200 | 0.300 | V    |

| SDA Output Low Voltage                     | VolSDA    | SDA active, I(SDA) = 20 mA                        | -     | -     | 0.4   | V    |

| PIN CHARACTERISTICS                        |           |                                                   |       |       |       |      |

| Enable Input Pull-down Resistance          | Rpdx      | EN = VDD                                          | 50    | 120   | 190   | kΩ   |

| Enable Input Threshold                     | VthIn     | EN increasing                                     | 1.1   | 1.4   | 1.9   | V    |

| Enable Input Hysteresis                    | Vhysln    | EN                                                | 0.100 | 0.265 | 0.600 | V    |

| FAULT Low Voltage                          | FLTBv     | FAULT active, I(FAULT) = 2 mA                     | -     | -     | 0.4   | V    |

| FAULT Leakage Current                      | FLTBi     | V(FAULT) = VDD                                    | -     | -     | 5     | μA   |

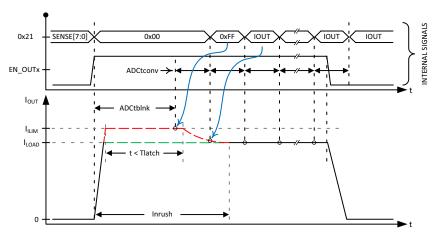

| INTERNAL ADC                               |           |                                                   |       |       |       |      |

| ADC Resolution                             | ADCres    |                                                   | -     | 8     | -     | bits |

| ADC Reference Voltage                      | ADCref    |                                                   | 0.95  | 1.00  | 1.05  | V    |

| Integral Non-linearity (INL)               | ADCinl    | (Notes 4, 8)                                      | -1.5  | -     | +1.5  | LSB  |

| Differential Non-linearity (DNL)           | ADCdnl    | (Notes 4, 8)                                      | -1.5  | -     | +1.5  | LSB  |

| Offset Error                               | ADCoff    | (Notes 4, 8)                                      | -3    | -     | +3    | LSB  |

| Gain Error                                 | ADCgain   | (Notes 4, 8)                                      | -2    | -     | +2    | %    |

| Conversion Time                            | ADCtconv  | (Note 4, Figure 21)                               | -     | 12    | -     | μs   |

| Initial Acquisition Delay                  | ADCblnk   | EN_OUTx 0→1 (Note 4, Figure 21)                   | -     | 200   | -     | μs   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Min/Max values are guaranteed by design, test, or statistical correlation, and are valid for the stated temperature range unless otherwise noted.

4. No production test.

5. Current limit accuracy is valid for saturation mode operation (short to ground and inrush/charging events).

The time required after EN L→H for the device to wake-up and confirm an I2C address selection (as per external resistor RADD) after which the device is ready for I2C communication.

7. The time required after EN H $\rightarrow$ L for the device to enter into sleep mode.

Measured as a deviation of the actual ADC transfer function from a best fit straight–line interpolation between 5% and 95% of the CS input Full–Scale Voltage, FSV = ADCref x (1 – 2<sup>-ADCres</sup>).

#### **Characteristic Timing Diagrams**

### **Characteristic Timing Diagrams**

#### **Detailed Operating Description**

#### **General Overview**

The NCV760040 is an  $I^2C$ -enabled target device featuring four independent high-side outputs constructed using two back-to-back NMOS power transistors for true reverse current blocking capability. Each output is protected against short to battery, short to ground, and overtemperature faults. An off-state open load diagnostic supports system-level fault detection.

The product features a low quiescent current sleep mode under control of the device's EN pin. The device transitions from sleep mode to active mode when EN changes from low to high, allowing device configuration and control of the outputs via I<sup>2</sup>C interface. The device transitions from active mode to sleep mode when EN changes from high to low, disabling the outputs and resetting all device registers to their default state.

The four outputs are grouped in pairs and powered via one of two independent supply inputs VIN1 and VIN2 (Figure 2). These can be directly connected to a conditioned battery voltage bus or to a lower bus voltage (Figure 1) such as may be supplied via a DC–DC converter within an application. VIN1 and VIN2 are each separately monitored for overvoltage and undervoltage events. During an undervoltage event, the corresponding outputs are disabled. During an overvoltage event, the corresponding outputs normally remain active and can be optionally configured via I<sup>2</sup>C to be disabled during overvoltage.

Device configuration, output control, and diagnosis is done via the  $I^2C$  interface at SCL rates up to 1 MHz. Target  $I^2C$  addresses may be programmed via an external resistor  $R_{ADD}$  at the device's ADD pin, allowing up to eight NCV760040 target devices supporting up to 32 high-side outputs. The ADD pin may optionally be left open or connected to ground, providing the target with a defined ninth default 'fail-safe'  $I^2C$  address, and supports target communication in the event of an open or shorted  $R_{ADD}$ resistor.

The product offers adjustable baseline current limit – programmed via an external resistor  $R_{CL}$  at the CL pin – as well as current limit shift functionality programmed via the I<sup>2</sup>C interface. Current limit shift allows for adjustments to the global baseline current limit on a per-channel basis. In the event of an open or shorted  $R_{CL}$  resistor, the baseline current limit defaults to defined levels.

An embedded 8-bit ADC converts the voltage at the CS pin – an external signal or a voltage developed via an internal current and an external resistor  $R_{CS}$  – for readout through I<sup>2</sup>C. The conversion range can be adapted to the programmed baseline current limit by adjusting the  $R_{CS}$  resistor. In the event of an open or shorted  $R_{CS}$  resistor, the ADC conversion range defaults to defined levels.

Conversion of the voltage developed via the  $R_{CS}$  resistor may also be done by connecting the CS pin to an external ADC. Conversion of an external signal via the internal ADC may be done by connecting the signal to the CS pin and by configuring the internal ADC accordingly.

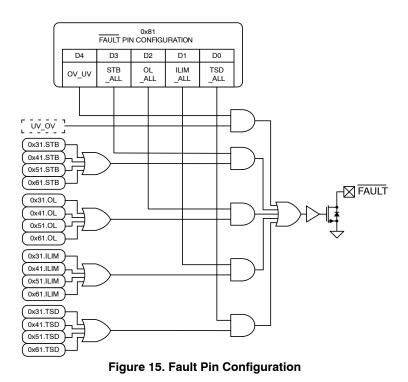

An open-drain flag pin provides a means for immediate communication of faults to a host controller. Short to battery, short to ground, overtemperature, and open load fault types from all channels are grouped by type and selectively routed to the flag pin. Control over which fault types are routed to the pin is provided via the fault pin configuration register (Figure 15).

#### Device I<sup>2</sup>C Protocol

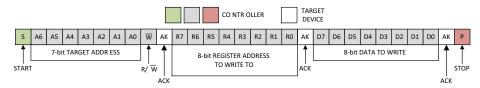

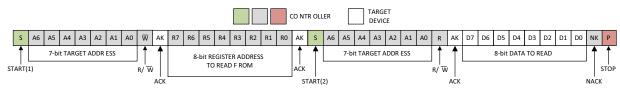

The NCV760040 is a target device compatible with the I<sup>2</sup>C-bus protocol, receiving and sending 8-bit transaction sequences via the SDA bus line synchronized to packets of 9 clock pulses on the SCL bus line. The clock pulses and the START and STOP conditions are always generated by a controller device. The NCV760040 does not employ any form of clock stretching. Refer to Figure 7 – Figure 10 for I<sup>2</sup>C transaction sequence examples.

For every transaction sequence, the first packet sent by the controller to a target begins with a START condition, defined by a high to low transition on SDA while SCL is held high. The final packet sent or received by the controller must be terminated by the controller with a STOP condition, defined by a low to high transition on SDA while SCL is held high.

During a write transaction sequence, the controller must release control of the SDA line after every byte sent to the target to allow the target to acknowledge (ACK) or not-acknowledge (NACK) receipt of the data. During a read transaction sequence, the target must release control of the SDA line after every byte sent to the controller to allow the controller to acknowledge (ACK) or not-acknowledge (NACK) receipt of the byte.

The ACK or NACK signal occurs during a packet's 9<sup>th</sup> SCL clock pulse. The ACK signal is defined by the target pulling SDA low while SCL is clocked. The NACK signal is defined by SDA remaining high while SCL is clocked. See the Figure 5 diagram for I<sup>2</sup>C and START timing and the Figure 6 diagram for ACK, NACK, and STOP timing.

The NCV760040 only accepts 8-bit data transactions that conform to the examples of Figure 7 – Figure 10 and have:

- 9 clock pulses per packet -and-

- a 1st packet containing a defined 7-bit target address with R/W = 0 - and -

- a 2nd packet containing a defined 8-bit register address.

If at any point within a transaction the controller's packet sequences do not conform to the target NCV760040's defined protocol, the target will ignore (NACK) the transaction, and the controller must abort the transaction and repeat it, if desired, by sending either:

• a STOP condition -or-

• a repeated START condition to begin a new transaction.

The defined target addresses are given in Table 7 and the defined register addresses are given in Table 8.

#### **Target Device Address**

Target Address 3

Target Address 4

Target Address 5

Target Address 6

Target Address 7

Target Address 8

(Fail-safe address)

Target I<sup>2</sup>C addresses may be programmed via an external resistor R<sub>ADD</sub> at the device's ADD pin, allowing up to eight NCV760040 target devices per standard 128–address I<sup>2</sup>C bus. The ADD pin may optionally be left open or connected to ground, providing the target with a defined ninth default 'fail–safe' I<sup>2</sup>C address, and supports target communication in the event of an open or shorted R<sub>ADD</sub> resistor. A 1% initial tolerance resistor with 3% end–of–life tolerance or better is recommended for R<sub>ADD</sub>.

The defined address assignments and corresponding  $R_{ADD}$  resistor values are summarized in Table 7. The general call address '0x00' is not supported. If a controller issues a general call address packet, the NCV760040 will ignore (NACK) the transaction.

| Table 7. TARGET DEVICE FC ADDRESS ENVINERATION |      |              |  |  |  |  |

|------------------------------------------------|------|--------------|--|--|--|--|

| Target Device<br>I <sup>2</sup> C Address      |      |              |  |  |  |  |

| Target Address 0                               | 0x60 | 536 $\Omega$ |  |  |  |  |

| Target Address 1                               | 0x61 | 1.24 kΩ      |  |  |  |  |

| Target Address 2                               | 0x62 | 2.80 kΩ      |  |  |  |  |

0x63

0x64

0x65

0x66

0x67

0x68

5.62 kΩ 11.5 kΩ

$27.4 \text{ k}\Omega$

59.0 kΩ

$133.0 \text{ k}\Omega$

ADD pin opened or shorted to ground

Table 7. TARGET DEVICE I<sup>2</sup>C ADDRESS ENUMERATION

The programmed target address is automatically enumerated upon transition from the sleep mode to the active mode via the EN pin, or upon power–on reset via the device's internal VDD monitor when EN is connected to VDD. Enumeration is completed and the target is ready for communication after the address acquisition time TADDconf. Except when grounding the pin, capacitive loading of the ADD pin can result in enumeration of an address different from that expected per the chosen  $R_{ADD}$  value.

#### I<sup>2</sup>C Transactions

Several examples of I<sup>2</sup>C transaction sequences conforming to the target NCV760040's defined protocol are provided in the following descriptions and figures.

*Single-byte Write Sequence:* (Figure 7) A START condition is sent, followed by a 7-bit target device address (Table 7) with the R/W bit = 0 to select write mode. Next, send the 8-bit register address (Table 8) to write to, followed by the data to write. Once the data have been written, the controller must send a NACK by pulling SDA high while SCL is clocked. A STOP sequence must then follow from the controller to end the transaction.

\*A 1/8 W 1% initial tolerance resistor with 3% end-of-life tolerance or better, and with a 100 ppm/°C tempco or better is recommended.

Figure 7. Write Transaction – Single-byte Sequence

Single-byte Read Sequence: (Figure 8) A first START condition is sent, followed by a 7-bit target device address with the R/W bit = 0 to select write mode. Next, send the 8-bit register address to read from. Then a second START condition is sent, followed by the same 7-bit target device address with the R/W bit = 1 to select read mode. The

controller must now release control of the SDA line to receive the 8-bit data from the target NCV760040. After the data have been read, the controller must send a NACK by pulling SDA high while SCL is clocked. A STOP sequence must then follow from the controller to end the transaction.

Figure 8. Read Transaction – Single-byte Sequence

*Multi-byte Write Sequence:* (Figure 9) A multi-byte write sequence is initially the same as a single-byte sequence, but following the first data byte sent, the controller does not send a STOP condition after receipt of the target's ACK signal. The controller instead continues to

write target address and data byte pairs to the same target address – to the same or to another data register address – then sends a STOP condition after the target acknowledges receipt of the final byte pair sent.

Figure 9. Write Transaction – Multi-byte Sequence

*Multi-byte Read Sequence:* (Figure 10) A multi-byte read sequence is initially the same as a single-byte sequence, but following the first data byte received from the target's register address 'N', the controller does not send a

NACK signal. The controller instead sends an ACK signal and continues to receive and acknowledge additional data bytes from the same target address, and the target increments its register address to 'N+1'.

Figure 10. Read Transaction – Multi-byte Sequence

The initial register address 'N' can be any of the target's valid register addresses. Once the target's last register address has been read, the target will automatically loop back to the lowest register address and will continue to send data as long ACK signals continue to be received from the controller. The controller indicates its final read request from the target by sending a NACK signal followed by a STOP condition.

#### **Register Structure**

Target device control and configuration commands, device status data, ADC data, and fault diagnostic data are accessed via the twelve defined device register addresses as summarized in Table 8.

| Function                   | Туре                             | Alias | Address | Description                                                                                                                     |

|----------------------------|----------------------------------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT CONTROL             | Read/Write                       | R0    | 0x11    | Per-channel output enable/disable.                                                                                              |

| CONFIGURATION              | Read/Write                       | R1    | 0x12    | Per-channel ILIM latch-off time select; global OVLO enable/<br>disable; current sense ADC channel selection.                    |

| CURRENT LIMIT SHIFT        | Read/Write                       | R2    | 0xA1    | Per-channel ILIM shift selection.                                                                                               |

| CONFIGURATION 2            | Read/Write                       | R3    | 0xA2    | Global clear-on-read (COR) mode enable/disable; off-state open load diagnostic enable/disable.                                  |

| ADC READOUT                | Read Only                        | R4    | 0x21    | Global ADC conversion data corresponding to the selected input source.                                                          |

| DIAGNOSTICS OUT1           | Read/Clear                       | R5    | 0x31    | Per-channel status and diagnostic data - output enabled/dis-                                                                    |

| DIAGNOSTICS OUT2           | Read/Clear                       | R6    | 0x41    | abled; current limit (ILIM), thermal warning, and thermal shut-<br>down status (TSD); short to battery (STB) and open load (OL) |

| DIAGNOSTICS OUT3           | Read/Clear                       | R7    | 0x51    | diagnostics.                                                                                                                    |

| DIAGNOSTICS OUT4           | Read/Clear                       | R8    | 0x61    |                                                                                                                                 |

| GLOBAL DIAGNOSTICS         | Mixed<br>Read Only<br>Read/Clear | R9    | 0x71    | Global fault status (STB/OL/ILIM/TSD – any channel); VIN1<br>and VIN2 undervoltage (UV) /overvoltage (OV) status.               |

| FAULT PIN<br>CONFIGURATION | Read/Write                       | R10   | 0x81    | Map selected status data to the FAULT pin: global VINx UV/OV; STB/OL/ILIM/TSD – any channel.                                    |

| DEVICE ID                  | Read Only                        | R11   | 0x82    | Hard-coded 3-bit device identification string.                                                                                  |

#### Table 8. DEVICE REGISTER SUMMARY

#### **R0 OUTPUT CONTROL Register**

#### R0 – OUTPUT CONTROL (Read/Write)

|         |         |         | Addres  | s: 0x11 |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

| RB_BLK4 | RB_BLK3 | RB_BLK2 | RB_BLK1 | EN_OUT4 | EN_OUT3 | EN_OUT2 | EN_OUT1 |

| Mnemonic | Functional Description                                                                                                                      |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| RB_BLKx  | Corresponding OUTx short to battery (STB) reverse blocking deglitch:<br>0 = blanking timer enabled (default)<br>1 = blanking timer disabled |

| EN_OUTx  | Corresponding OUTx control:<br>0 = OUTx disabled (default)<br>1 = OUTx enabled                                                              |

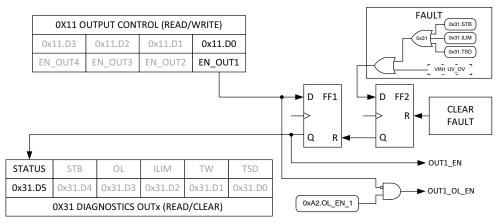

The 0x11.OUTPUT CONTROL register provides read/write access for configuration of the short to battery blanking timer via register bits D[7:4] and for control of the OUTx drivers via register bits D[3:0]. Selection of the several configuration options is done by writing to the corresponding register bits. Confirmation of the written configuration is returned by reading the same register bits. Default after VDD POR or WAKE: 0x11.D[7:0] = 0x00. Refer to § Short to Battery Protection for additional details about the STB functionality.

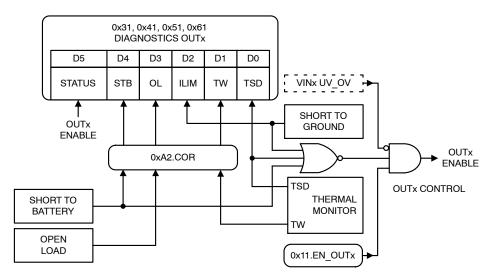

Using OUT1 as a focus example, Figure 11 shows the simplified register and output control topology. Basic control of the outputs is done by writing to the 0x11.EN\_OUTx bits. Real-time status of the outputs is

returned by reading the STATUS bit in the 0x31 DIAGNOSTICS OUTx register. If for example activation of OUT1 is desired, writing '1' to the EN\_OUT1 bit will enable activation of OUT1. If there are no fault conditions present, the output will turn on and its status can be confirmed by reading '1' via the 0x31 STATUS bit.

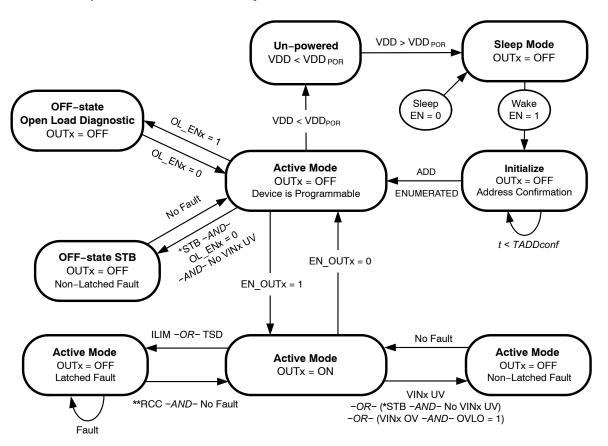

The device's fault protection and recovery, and its fault reporting and clearing functionalities work together with behaviors that are dependent upon the specific fault type. Further details about the embedded protections and their fault handling and status reporting behaviors are provided in the succeeding sections of this datasheet. A summary of the protections and behaviors is provided in Table 12.

Figure 11. Output Control Overview (OUT1 focus)

#### **R1 Configuration Register**

R1 CONFIGURATION REGISTER (Read/Write)

| Address: 0x12 |         |         |         |      |                   |    |    |

|---------------|---------|---------|---------|------|-------------------|----|----|

| D7            | D6      | D5      | D4      | D3   | D2                | D1 | D0 |

| LATCH_1       | LATCH_2 | LATCH_3 | LATCH_4 | OVLO | SENSE_SELECT[2:0] |    |    |

| Mnemonic          | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LATCH_X           | Per-channel ILIM timer for corresponding OUTx:<br>0 = OUTx latches off after time <i>Tlatch0</i> (default)<br>1 = OUTx latches off after time <i>Tlatch1</i>                                                                                                                                                                                                                                                                                              |

| OVLO              | Global VIN1 and VIN2 overvoltage lockout control:<br>0 = corresponding OUTx remain on during overvoltage (default)<br>1 = corresponding OUTx are disabled during overvoltage                                                                                                                                                                                                                                                                              |

| SENSE_SELECT[2:0] | Channel selection for output current sensing via the internal ADC:<br>0b000 = current sense functionality and ADC disabled (default)<br>0b001 = ADC enabled; input is OUT1 sense current<br>0b010 = ADC enabled; input is OUT2 sense current<br>0b011 = ADC enabled; input is OUT3 sense current<br>0b100 = ADC enabled; input is OUT4 sense current<br>0b101 = ADC enabled; input is external signal at CS pin<br>All other 3-bit combinations reserved. |

The 0x12. CONFIGURATION register provides read/write access for per–channel configuration of the ILIM protection delay via register bits D[7:4], for configuration of the global overvoltage lockout control via bit D[3], and for configuration of the current sense and ADC functional blocks via bits D[2:0]. Selection of the several configuration options is done by writing to the corresponding register bits. Confirmation of the written configuration is returned by reading the same register bits. Default after VDD POR or WAKE: 0x12.D[7:0] = 0x00.

Upon detection of an overcurrent condition, the ILIM protection function latches off the affected output after expiration of a delay time *Tlatch0* (20 ms typ.) or *Tlatch1* (20  $\mu$ s typ.) as selected via the 0x12.LATCH\_X bits. The per-channel delay times can be configured along with the 0xA1.CL\_SHIFT\_X bits to help accommodate transient inrush/charging events such as when driving an incandescent lamp load, a large capacitor load, or a motor load's initial start-up/stall torque. Refer to § Current Limit and Current Limit Shift for details about the ILIM functionality.

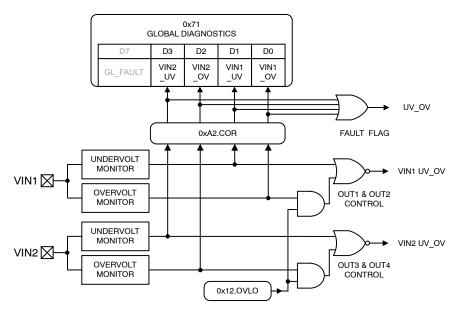

Each of VIN1 and VIN2 is monitored for undervoltage and overvoltage conditions. Upon detection of a VINx undervoltage condition, the corresponding OUTx drivers are always disabled. Upon detection of a VINx overvoltage condition, the corresponding OUTx drivers are enabled or disabled according to the 0x12.OVLO bit. Refer to § VINx Voltage Monitoring for details about the OVLO functionality.

Current sense ('front-end') and ADC ('back-end') functional blocks (see Figure 18) are embedded to provide a readout of a channel's sensed output current (as a voltage developed via an external resistor) at the CS pin, or to provide a readout an external voltage applied directly to the CS pin. The 0x12. SENSE\_SELECT bits are provided to select which front-end input signal (internal or external) will be routed to the ADC back-end, or to disable the embedded current sense and ADC blocks for reduced power consumption. Refer to § Current Sense and ADC for details about the ADC functionality.

#### **R2 CURRENT LIMIT SHIFT Register**

|         |          | Address         |  | s: 0xA1 |          |                 |    |

|---------|----------|-----------------|--|---------|----------|-----------------|----|

| D7      | D6       | D5 D4           |  | D3      | D2       | D1              | D0 |

| CL_SHIF | T_4[1:0] | CL_SHIFT_3[1:0] |  | CL_SHIF | T_2[1:0] | CL_SHIFT_1[1:0] |    |

| Mnemonic        | Functional Description                                                                                                                        |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CL_SHIFT_X[1:0] | Increase the baseline current limit on OUTx by the selected percentage:<br>0b00 = +0% (default)<br>0b01 = +30%<br>0b10 = +60%<br>0b11 = +100% |

The 0xA1 CURRENT LIMIT SHIFT register provides read/write access for per–channel modification of the ILIM protection baseline current limit as set via an external resistor  $R_{CL}$ . Selection of the several configuration options is done by writing to the corresponding register bits. Confirmation of the written configuration is returned by reading the same register bits. Default after VDD POR or WAKE: 0xA1.D[7:0] = 0x00.

The per-channel shift level multiplies the baseline current limit according to the corresponding 0xA1.CL\_SHIFT\_X bits. The shift level can be configured along with the 0x12.LATCH\_X bits to help accommodate transient inrush/charging events such as when driving an incandescent lamp load, a large capacitor load, or a motor load's initial start-up/stall torque.

A 'failsafe' limit functionality is embedded for the case of 1.) open/missing/out-of-range-high or 2.) shorted/ short-to-GND/out-of-range-low  $R_{CL}$  resistor which bounds/defaults the current limit in the 'open' case to 100 mA nominal and in the 'short' case to 1.2 A nominal. The "current limit shift" multiplier functionality is disabled when either `open' or 'short' condition is detected.

For proper operation and parametric quality, the current limit shift functionality requires resistor  $R_{CL}$  to be in the range 2.5 k $\Omega \leq R_{CL} \leq 30$  k $\Omega$ . Refer to § Current Limit and Current Limit Shift for details about the ILIM and CL\_SHIFT functionalities.

#### R3 CONFIGURATION 2 Register

#### R3 – CONFIGURATION 2 (Read/Write)

| D7 D6 D5 D4 D3 D2 D1 D0  |     |    |    | Addres | s: 0xA2 |    |              |    |

|--------------------------|-----|----|----|--------|---------|----|--------------|----|

|                          | D7  | D6 | D5 | D4     | D3      | D2 | D1           | D0 |

| COR – – – – OL_EN_X[2:0] | COR | -  | -  | -      | -       |    | OL_EN_X[2:0] |    |

| Mnemonic     | Functional Description                                                                                                                                                                                                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COR          | Global Clear–On–Read (COR) mode for specific non–latched fault types<br>(see also Table 12 summary):<br>0 = fault status bit(s) updated continuously (default)<br>1 = fault status bit(s) cleared after reading corresponding register                                                                          |

| OL_EN_X[2:0] | Off-state open load diagnostic (current and detection) control:<br>0b000 = diagnostic disabled for all channels (default)<br>0b001 = OUT1 diagnostic enabled<br>0b010 = OUT2 diagnostic enabled<br>0b011 = OUT3 diagnostic enabled<br>0b100 = OUT4 diagnostic enabled<br>All other 3-bit combinations reserved. |

The 0xA2 CONFIGURATION 2 register provides read/write access for modification of the global Clear–On–Read (COR) functionality and for the off–state open load diagnostic functionality. Selection of the several configuration options is done by writing to the corresponding register bits. Confirmation of the written configuration is returned by reading the same register bits. Default after VDD POR or WAKE: 0xA2.D[7:0] = 0x00.

Non-latched driver output fault types – short to battery (STB), open load (OL), and thermal warning (TW) – and non-latched global VINx fault types undervoltage (UV) and overvoltage (OV) – are those that may temporarily disable the affected outputs while a fault is preset then re–enable it automatically when the fault resolves.

Real-time status of the driver output faults and of the global UV/OV faults is returned by respectively reading the

0x31-0x61.DIAGNOSTICS OUTx status bits and the 0x71.GLOBAL DIAGNOSTICS status bits. By default, these status bits are also non-latched and so a transient fault – which may cause momentary interruption of an output – can lead to a situation where the fault resolves and no status information about the fault is captured.

The COR bit can be used to modify the specific non-latched fault types so that their status information is latched into the DIAGNOSTICS OUTx and GLOBAL DIAGNOSTICS and is available during and after resolution of a non-latched fault type. Note that when enabled, the COR functionality affects all non-latched diagnostic bits. Refer to § Diagnostic Register Clearing for additional details about the COR functionality.

An embedded off-state open load (OL) diagnostic – using a single current source and a single comparator detection block – is implemented along with a multiplexer. The 0xA2 OL\_EN\_X bits are provided to select which one of the four OUTx is to be routed to the detection block. Refer to § Off-state Open Load for additional details about the OL diagnostic functionality.

#### **R4 ADC READOUT Register**

R4 – ADC READOUT (Read Only)

|                         | Address: 0x21 |  |  |  |  |  |  |

|-------------------------|---------------|--|--|--|--|--|--|

| D7 D6 D5 D4 D3 D2 D1 D0 |               |  |  |  |  |  |  |

| SENSE[7:0]              |               |  |  |  |  |  |  |

| Mnemonic   | Functional Description                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| SENSE[7:0] | Global 8-bit ADC conversion data corresponding to the input source selected via the register 0x12.SENSE_SELECT bits. (default: 0x21.D[7:0]= 0x00) |

The 0x21 ADC READOUT register provides read-only access for retrieving conversion data from the embedded 8-bit ADC. The returned data represents the last conversion of the sampled ADC input source value as selected via the

register  $0x12.SENSE\_SELECT$  bits. Default after VDD POR or WAKE: 0x21.D[7:0] = 0x00. Refer to § Current Sense and ADC for details about the ADC functionality.

#### R5 - R8 - DIAGNOSTICS OUTx Register

#### R5 - R8 - DIAGNOSTICS OUTx (Mixed Types: Read Only, Read/Clear)

| R5 – OUT1 Address: 0x31<br>R6 – OUT2 Address: 0x41<br>R7 – OUT3 Address: 0x51                                     |   |        |     |    |      |    |     |

|-------------------------------------------------------------------------------------------------------------------|---|--------|-----|----|------|----|-----|

| R8 - OUT4 Address: 0x61           D7         D6         D5         D4         D3         D2         D1         D0 |   |        |     |    | D0   |    |     |

| _                                                                                                                 | - | STATUS | STB | OL | ILIM | TW | TSD |

| Mnemonic | Туре       | Functional Description                                                                                                                                    |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS   | Read Only  | State of corresponding output:<br>0 = OUTx disabled (default)<br>1 = OUTx enabled                                                                         |

| STB      | Read/Clear | State of corresponding OUTx Short To Battery (STB) condition:<br>0 = STB condition not detected (default)<br>1 = STB condition detected                   |

| OL       | Read/Clear | State of corresponding OUTx Open Load (OL) condition:<br>0 = OL condition not detected (default)<br>1 = OL condition detected                             |

| ILIM     | Read/Clear | State of corresponding OUTx current vs. current limit (ILIM) condition:<br>0 = OUTx current < current limit (default)<br>1 = OUTx current > current limit |

| TW       | Read/Clear | State of corresponding OUTx Thermal Warning (TW) condition:<br>0 = TW condition not detected (default)<br>1 = TW condition detected                       |

| TSD      | Read/Clear | State of corresponding OUTx Thermal Shut Down (TSD) condition:<br>0 = TSD condition not detected (default)<br>1 = TSD condition detected                  |

The 0x31 - 0x61 DIAGNOSTICS OUTx registers provide read only and read/clear access for retrieving output status and fault diagnostic status for each of the four driver channels. The real-time output STATUS bit indicates whether the corresponding OUTx driver is enabled or disabled. The fault status bits are either latched or non-latched types and indicate whether a driver fault has been detected. Default after VDD POR or WAKE: 0x31 – 0x61.D[7:0] = 0x00.

Figure 12 hows the basic register structure and output control topology. Latched driver output fault types – current limit (ILIM) and thermal shutdown (TSD) – are those that disable and latch the affected outputs off after a delay time (configurable for ILIM via the 0x12.LATCH\_X bits) when a fault is detected and latch the event into the register's respective fault status bit. Non–latched driver output fault types – short to battery (STB), open load (OL), and thermal warning (TW) – are those that may temporarily disable the affected outputs while a fault is present then re–enable it automatically when the fault resolves.

Note that the device's global VINx\_UV and VINx\_OV voltage monitor bits can provide an additional non-latched fault type which – when modified by the overvoltage lockout bit (0x12.OVLO = 1) – can disable the outputs

associated with the affected VINx path, and cause the STATUS bit to report `0' during an overvoltage event *without indicating any other condition within the DIAGNOSTICS OUTx register itself.* Refer to § VINx Voltage Monitoring § R1 CONFIGURATION Register and § R9 – GLOBAL DIAGNOSTCS Register for details about the overvoltage monitor functionality.

Non-latched fault bits provide real-time status of the driver output faults and so can be transient in nature, which can lead to a situation where a fault resolves and no status information about the fault is captured. The 0xA2.COR bit can be used to modify the non-latched fault types so that their status information is latched into the fault bits and is available during and after resolution of a non-latched fault type. In any case, merely reading the DIAGNOSTICS OUTx registers does not clear any fault bit states and does not re-enable a faulted driver output. Refer to § Diagnostic Register Clearing for additional details about the read/clear and COR functionalities.

For details about each of the STB, OL, ILIM, TW, and TSD functionalities, refer to their corresponding datasheet sections. For details about fault handling refer to § Device Modes and Fault Handling.

Figure 12. Per-channel Diagnostics Mapping and COR Configuration

#### **R9 – GLOBAL DIAGNOSTICS Register**

|          |            |                             | A -1-1 |                                                                                                                                                                  |         |         |         |  |  |

|----------|------------|-----------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|--|--|

|          |            |                             | Addre  | ess: 0x71                                                                                                                                                        |         |         |         |  |  |

| D7       | D6         | D5                          | D4     | D3                                                                                                                                                               | D2      | D1      | D0      |  |  |

| GL_FAULT | -          | _                           | _      | VIN2_UV                                                                                                                                                          | VIN2_OV | VIN1_UV | VIN1_OV |  |  |

|          |            |                             |        |                                                                                                                                                                  |         |         |         |  |  |

| Mnemonic | Туј        | Type Functional Description |        |                                                                                                                                                                  |         |         |         |  |  |

| GL_FAULT | Read Only  |                             | 0 =    | Driver fault condition detection (STB, OL, ILIM, TSD)<br>0 = no fault condition(s) detected (default)<br>1 = fault conditions(s) detected on one or more outputs |         |         |         |  |  |

| VIN2_UV  | Read/      | Clear                       | 0 =    | VIN2 Undervoltage (UV) condition<br>0 = UV condition not detected (default)<br>1 = UV condition detected                                                         |         |         |         |  |  |

| VIN2_OV  | Read/Clear |                             | 0 =    | VIN2 Overvoltage (OV) condition<br>0 = OV condition not detected (default)<br>1 = OV condition detected                                                          |         |         |         |  |  |

VIN1\_UV

Read/Clear

VIN1 Undervoltage (UV) condition

0 = UV condition not detected (default)

1 = UV condition detected

VIN1\_OV

Read/Clear

VIN1 Overvoltage (OV) condition

0 = OV condition not detected (default)

1 = OV condition not detected (default)

1 = OV condition not detected

1 = OV condition not detected

The 0x71 GLOBAL DIAGNOSTICS register provides read only and read/clear access for retrieving driver diagnostic status for all four driver channels and for retrieving global VINx undervoltage (UV) and overvoltage (OV) fault types. The global status bits comprise both latched and non-latched types. Default after VDD POR or WAKE: 0x71.D[7:0] = 0x00.

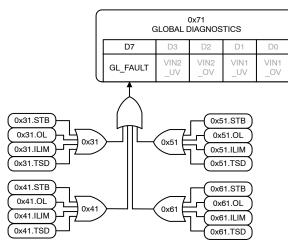

Figures 13 and 14 show the register structures and the basic output control topology. The 0x71. GL\_FAULT bit is a 'read only' type and provides the combined fault states of all four driver channels. The 0x71.VINx\_UV and 0x71.VINx\_OV bits are read/clear types and provide fault states for each VINx voltage.

Note that the global VINx\_UV and VINx\_OV voltage monitor bits can provide an additional non-latched fault type which can disable the outputs associated with the affected VINx path, and cause the DIAGNOSTICS OUTx register STATUS bit to report '0' during an undervoltage event – and optionally an overvoltage event – without indicating any other condition within the DIAGNOSTICS OUTx register itself.

Since OUTx STATUS bits are not mapped to the GLOBAL DIAGNOSTICS register's GL\_FAULT bit, occurrence of a VINx under/over voltage event will only be mapped to the global register's VINx\_UV and VINx\_OV bits. Refer to § VINx Voltage Monitoring for details about the undervoltage and overvoltage functionalities.

The persistence of any of the bit states is dependent upon a particular fault's behavior (transient or steady-state), and a particular fault bit's reporting behavior (latched or non-latched) – which can be modified by the global Clear On Read (COR) functionality via the 0xA2.COR bit. Refer to § Diagnostic Register Clearing for details about the read/clear and the global COR functionalities.

Figure 13. Global Diagnostics: Global Fault Mapping

Figure 14. Global Diagnostics: Under/Over Voltage (UV/OV) Mapping and COR Configuration

#### **R10 – FAULT PIN CONFIGURATION Register**

|                                                                                                                                                                                                            |                                                                                                                                                                     |    | Addres                                                                                                                                                  | s: 0x81                                                        |                   |          |         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------|----------|---------|--|--|

| D7                                                                                                                                                                                                         | D6                                                                                                                                                                  | D5 | D4                                                                                                                                                      | D3                                                             | D2                | D1       | D0      |  |  |