## Precision Switchmode Pulse Width Modulation Control Circuit

## **TL594**

The TL594 is a fixed frequency, pulse width modulation control circuit designed primarily for Switchmode power supply control.

#### **Features**

- Complete Pulse Width Modulation Control Circuitry

- On-Chip Oscillator with Master or Slave Operation

- On-Chip Error Amplifiers

- On-Chip 5.0 V Reference, 1.5% Accuracy

- Adjustable Deadtime Control

- Uncommitted Output Transistors Rated to 500 mA Source or Sink

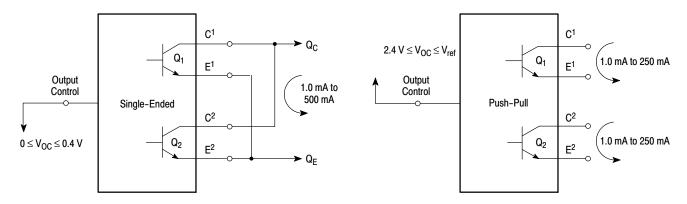

- Output Control for Push-Pull or Single-Ended Operation

- Undervoltage Lockout

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant\*

#### **MAXIMUM RATINGS**

| Rating                                                                                           | Symbol                               | Value            | Unit |

|--------------------------------------------------------------------------------------------------|--------------------------------------|------------------|------|

| Power Supply Voltage                                                                             | V <sub>CC</sub>                      | 42               | V    |

| Collector Output Voltage                                                                         | V <sub>C1</sub> ,<br>V <sub>C2</sub> | 42               | V    |

| Collector Output Current<br>(Each Transistor) (Note 1)                                           | I <sub>C1</sub> , I <sub>C2</sub>    | 500              | mA   |

| Amplifier Input Voltage Range                                                                    | V <sub>IR</sub>                      | -0.3 to +42      | V    |

| Power Dissipation @ T <sub>A</sub> ≤ 45°C                                                        | P <sub>D</sub>                       | 1000             | mW   |

| Thermal Resistance Junction-to-Ambient (PDIP) Junction-to-Air (TSSOP) Junction-to-Ambient (SOIC) | $R_{	hetaJA}$                        | 80<br>140<br>135 | °C/W |

| Operating Junction Temperature                                                                   | TJ                                   | 125              | °C   |

| Storage Temperature Range                                                                        | T <sub>stg</sub>                     | -55 to +125      | °C   |

| Operating Ambient Temperature Range TL594CD, CN, CDTB                                            | T <sub>A</sub>                       | -40 to 85        | °C   |

| Derating Ambient Temperature                                                                     | T <sub>A</sub>                       | 45               | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Maximum thermal limits must be observed.

#### MARKING DIAGRAMS

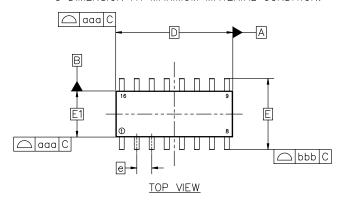

SOIC-16 D SUFFIX CASE 751B

A = Assembly Location

WL, L = Wafer Lot Y = Year WW, W = Work Week

G or ■ = Pb-Free Package

(Note: Microdot may be in either location)

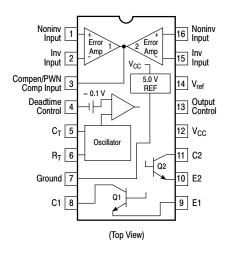

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

1

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **TL594**

### **RECOMMENDED OPERATING CONDITIONS**

| Characteristics                            | Symbol                            | Min    | Тур   | Max                   | Unit |

|--------------------------------------------|-----------------------------------|--------|-------|-----------------------|------|

| Power Supply Voltage                       | V <sub>CC</sub>                   | 7.0    | 15    | 40                    | V    |

| Collector Output Voltage                   | $V_{C1}, V_{C2}$                  | -      | 30    | 40                    | V    |

| Collector Output Current (Each transistor) | I <sub>C1</sub> , I <sub>C2</sub> | -      | -     | 200                   | mA   |

| Amplified Input Voltage                    | V <sub>in</sub>                   | 0.3    | -     | V <sub>CC</sub> - 2.0 | V    |

| Current Into Feedback Terminal             | I <sub>fb</sub>                   | -      | -     | 0.3                   | mA   |

| Reference Output Current                   | I <sub>ref</sub>                  | -      | -     | 10                    | mA   |

| Timing Resistor                            | R <sub>T</sub>                    | 1.8    | 30    | 500                   | kΩ   |

| Timing Capacitor                           | C <sub>T</sub>                    | 0.0047 | 0.001 | 10                    | μF   |

| Oscillator Frequency                       | f <sub>osc</sub>                  | 1.0    | 40    | 300                   | kHz  |

| PWM Input Voltage (Pins 3, 4, 13)          | -                                 | 0.3    | -     | 5.3                   | V    |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 15 V,  $C_T$  = 0.01  $\mu$ F,  $R_T$  = 12  $k\Omega$ , unless otherwise noted.) For typical values  $T_A$  = 25°C, for min/max values  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted.

| Characteristics                                                                                                                                                                   | Symbol                                     | Min          | Тур                       | Max          | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|---------------------------|--------------|------|

| REFERENCE SECTION                                                                                                                                                                 | •                                          | •            |                           | •            | •    |

| Reference Voltage $(I_O = 1.0 \text{ mA}, T_A = 25^{\circ}\text{C})$ $(I_O = 1.0 \text{ mA})$                                                                                     | V <sub>ref</sub>                           | 4.925<br>4.9 | 5.0<br>-                  | 5.075<br>5.1 | V    |

| Line Regulation (V <sub>CC</sub> = 7.0 V to 40 V)                                                                                                                                 | Reg <sub>line</sub>                        | _            | 2.0                       | 25           | mV   |

| Load Regulation (I <sub>O</sub> = 1.0 mA to 10 mA)                                                                                                                                | Reg <sub>load</sub>                        | -            | 2.0                       | 15           | mV   |

| Short Circuit Output Current (V <sub>ref</sub> = 0 V)                                                                                                                             | I <sub>SC</sub>                            | 15           | 40                        | 75           | mA   |

| OUTPUT SECTION                                                                                                                                                                    |                                            |              |                           |              |      |

| Collector Off–State Current (V <sub>CC</sub> = 40 V, V <sub>CE</sub> = 40 V)                                                                                                      | I <sub>C(off)</sub>                        | -            | 2.0                       | 100          | μΑ   |

| Emitter Off-State Current (V <sub>CC</sub> = 40 V, V <sub>C</sub> = 40 V, V <sub>E</sub> = 0 V)                                                                                   | I <sub>E(off)</sub>                        | -            | -                         | -100         | μΑ   |

| Collector–Emitter Saturation Voltage (Note 1)<br>Common–Emitter ( $V_E = 0 \text{ V}, I_C = 200 \text{ mA}$ )<br>Emitter–Follower ( $V_C = 15 \text{ V}, I_E = -200 \text{ mA}$ ) | V <sub>SAT(C)</sub><br>V <sub>SAT(E)</sub> | -<br>-       | 1.1<br>1.5                | 1.3<br>2.5   | V    |

| Output Control Pin Current Low State ( $V_{OC} \le 0.4 \text{ V}$ ) High State ( $V_{OC} = V_{ref}$ )                                                                             | I <sub>OCL</sub><br>I <sub>OCH</sub>       | -<br>-       | 0.1<br>2.0                | _<br>20      | μΑ   |

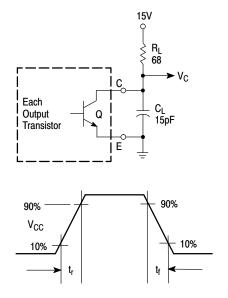

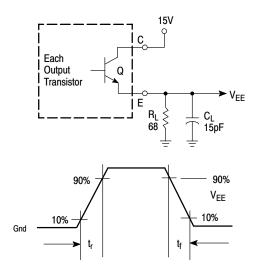

| Output Voltage Rise Time Common–Emitter (See Figure 13) Emitter–Follower (See Figure 14)                                                                                          | t <sub>r</sub>                             | -<br>-       | 100<br>100                | 200<br>200   | ns   |

| Output Voltage Fall Time Common–Emitter (See Figure 13) Emitter–Follower (See Figure 14)                                                                                          | t <sub>f</sub>                             | -<br>-       | 40<br>40                  | 100<br>100   | ns   |

| ERROR AMPLIFIER SECTION                                                                                                                                                           | 1                                          |              |                           | •            |      |

| Input Offset Voltage (V <sub>O (Pin 3)</sub> = 2.5 V)                                                                                                                             | V <sub>IO</sub>                            | -            | 2.0                       | 10           | mV   |

| Input Offset Current (V <sub>O (Pin 3)</sub> = 2.5 V)                                                                                                                             | I <sub>IO</sub>                            | -            | 5.0                       | 250          | nA   |

| Input Bias Current (V <sub>O (Pin 3)</sub> = 2.5 V)                                                                                                                               | I <sub>IB</sub>                            | -            | -0.1                      | -1.0         | μΑ   |

| Input Common Mode Voltage Range (V <sub>CC</sub> = 40 V, T <sub>A</sub> = 25°C)                                                                                                   | V <sub>ICR</sub>                           | (            | to V <sub>CC</sub> -2.0   | )            | V    |

| Inverting Input Voltage Range                                                                                                                                                     | V <sub>IR(INV)</sub>                       | -(           | 0.3 to V <sub>CC</sub> -2 | 2.0          | V    |

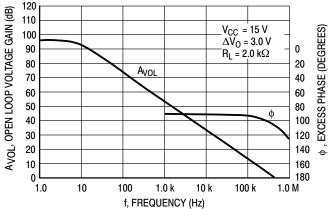

| Open Loop Voltage Gain ( $\Delta V_{O}$ = 3.0 V, $V_{O}$ = 0.5 V to 3.5 V, $R_{L}$ = 2.0 k $\Omega$ )                                                                             | A <sub>VOL</sub>                           | 70           | 95                        | -            | dB   |

| Unity–Gain Crossover Frequency ( $V_{O}$ = 0.5 V to 3.5 V, $R_{L}$ = 2.0 k $\Omega$ )                                                                                             | f <sub>C</sub>                             | -            | 700                       | -            | kHz  |

| Phase Margin at Unity–Gain ( $V_0$ = 0.5 V to 3.5 V, $R_L$ = 2.0 k $\Omega$ )                                                                                                     | φm                                         | -            | 65                        | -            | deg. |

| Common Mode Rejection Ratio (V <sub>CC</sub> = 40 V)                                                                                                                              | CMRR                                       | 65           | 90                        | _            | dB   |

| Power Supply Rejection Ratio ( $\Delta V_{CC}$ = 33 V, $V_{O}$ = 2.5 V, $R_{L}$ = 2.0 k $\Omega$ )                                                                                | PSRR                                       | -            | 100                       | -            | dB   |

| Output Sink Current (V <sub>O (Pin 3)</sub> = 0.7 V)                                                                                                                              | I <sub>O</sub> -                           | 0.3          | 0.7                       | -            | mA   |

| Output Source Current (V <sub>O (Pin 3)</sub> = 3.5 V)                                                                                                                            | l <sub>O</sub> +                           | -2.0         | -4.0                      | -            | mA   |

<sup>1.</sup> Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient temperature as possible.

## **TL594**

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 15 V,  $C_T$  = 0.01 μF,  $R_T$  = 12 kΩ, unless otherwise noted.) For typical values  $T_A$  = 25°C, for min/max values  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted.

| Characteristics                                                                                                                                                                                                              | Symbol                      | Min        | Тур           | Max             | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------|---------------|-----------------|------|

| PWM COMPARATOR SECTION (Test Circuit Figure 11)                                                                                                                                                                              | •                           |            | •             | •               |      |

| Input Threshold Voltage (Zero Duty Cycle)                                                                                                                                                                                    | V <sub>TH</sub>             | -          | 3.6           | 4.5             | V    |

| Input Sink Current (V <sub>Pin 3</sub> = 0.7 V)                                                                                                                                                                              | I <sub>I</sub> _            | 0.3        | 0.7           | -               | mA   |

| DEADTIME CONTROL SECTION (Test Circuit Figure 11)                                                                                                                                                                            |                             |            |               |                 |      |

| Input Bias Current (Pin 4) (V <sub>Pin 4</sub> = 0 V to 5.25 V)                                                                                                                                                              | I <sub>IB (DT)</sub>        | -          | -2.0          | -10             | μΑ   |

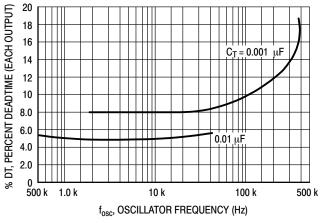

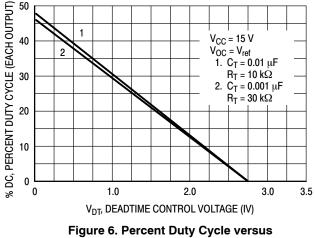

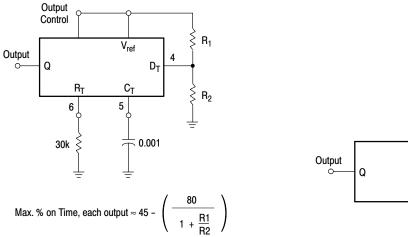

| Maximum Duty Cycle, Each Output, Push–Pull Mode ( $V_{Pin~4}=0~V,~C_{T}=0.01~\mu F,~R_{T}=12~k\Omega$ ) ( $V_{Pin~4}=0~V,~C_{T}=0.001~\mu F,~R_{T}=30~k\Omega$ )                                                             | DC <sub>max</sub>           | 45<br>-    | 48<br>45      | 50<br>-         | %    |

| Input Threshold Voltage (Pin 4)<br>(Zero Duty Cycle)<br>(Maximum Duty Cycle)                                                                                                                                                 | V <sub>TH</sub>             | _<br>0     | 2.8           | 3.3             | V    |

| OSCILLATOR SECTION                                                                                                                                                                                                           |                             |            |               |                 |      |

| Frequency $ \begin{array}{l} (C_T=0.001~\mu\text{F},~R_T=30~k\Omega) \\ (C_T=0.01~\mu\text{F},~R_T=12~k\Omega,~T_A=25^\circ\text{C}) \\ (C_T=0.01~\mu\text{F},~R_T=12~k\Omega,~T_A=T_{low}~\text{to}~T_{high}) \end{array} $ | f <sub>osc</sub>            | 9.2<br>9.0 | 40<br>10<br>- | -<br>10.8<br>12 | kHz  |

| Standard Deviation of Frequency* (C <sub>T</sub> = 0.001 $\mu$ F, R <sub>T</sub> = 30 k $\Omega$ )                                                                                                                           | σf <sub>osc</sub>           | -          | 1.5           | -               | %    |

| Frequency Change with Voltage (V <sub>CC</sub> = 7.0 V to 40 V, T <sub>A</sub> = 25°C)                                                                                                                                       | $\Delta f_{OSC} (\Delta V)$ | -          | 0.2           | 1.0             | %    |

| Frequency Change with Temperature $(\Delta T_A = T_{low} \text{ to } T_{high}, C_T = 0.01 \ \mu\text{F}, R_T = 12 \ \text{k}\Omega)$                                                                                         | $\Delta f_{osc} (\Delta T)$ | -          | 4.0           | -               | %    |

| UNDERVOLTAGE LOCKOUT SECTION                                                                                                                                                                                                 |                             |            |               |                 |      |

| Turn-On Threshold (V <sub>CC</sub> Increasing, $I_{ref}$ = 1.0 mA)<br>$T_A$ = 25°C<br>$T_A$ = $T_{low}$ to $T_{high}$                                                                                                        | V <sub>th</sub>             | 4.0<br>3.5 | 5.2           | 6.0<br>6.5      | V    |

| Hysteresis<br>TL594C,I<br>TL594M                                                                                                                                                                                             | V <sub>H</sub>              | 100<br>50  | 150<br>150    | 300<br>300      | mV   |

| TOTAL DEVICE                                                                                                                                                                                                                 |                             |            |               |                 |      |

| Standby Supply Current (Pin 6 at $V_{ref}$ , All other inputs and outputs open) ( $V_{CC}$ = 15 V) ( $V_{CC}$ = 40 V)                                                                                                        | Icc                         |            | 8.0<br>8.0    | 15<br>18        | mA   |

| Average Supply Current (V <sub>Pin 4</sub> = 2.0 V, C <sub>T</sub> = 0.01 $\mu$ F, R <sub>T</sub> = 12 k $\Omega$ , V <sub>CC</sub> = 15 V, See Figure 11)                                                                   |                             | -          | 11            | _               | mA   |

\*Standard deviation is a measure of the statistical distribution about the mean as derived from the formula,  $\sigma$   $\sqrt{\frac{\sum_{i=1}^{N} (X_{n} - \overline{X})^{2}}{\frac{n-1}{N-1}}}$

This device contains 46 active transistors.

Figure 1. Representative Block Diagram

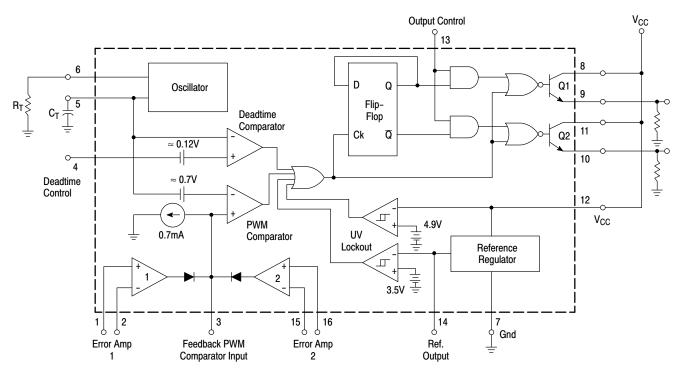

Figure 2. Timing Diagram

#### **APPLICATIONS INFORMATION**

#### **Description**

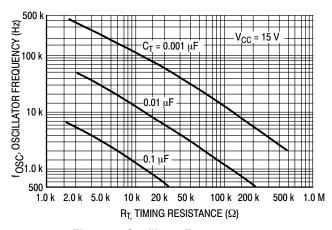

The TL594 is a fixed–frequency pulse width modulation control circuit, incorporating the primary building blocks required for the control of a switching power supply. (See Figure 1) An internal–linear sawtooth oscillator is frequency–programmable by two external components,  $R_T$  and  $C_T$ . The approximate oscillator frequency is determined by:

$$f_{osc} \approx \frac{1.1}{R_T \bullet C_T}$$

For more information refer to Figure 3.

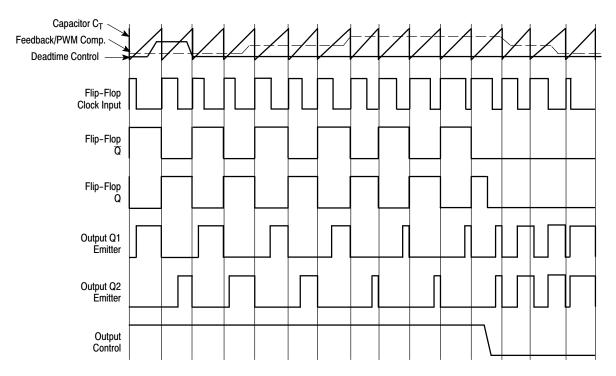

Output pulse width modulation is accomplished by comparison of the positive sawtooth waveform across capacitor  $C_T$  to either of two control signals. The NOR gates, which drive output transistors Q1 and Q2, are enabled only when the flip-flop clock-input line is in its low state. This happens only during that portion of time when the sawtooth voltage is greater than the control signals. Therefore, an increase in control-signal amplitude causes a corresponding linear decrease of output pulse width. (Refer to the Timing Diagram shown in Figure 2.)

The control signals are external inputs that can be fed into the deadtime control, the error amplifier inputs, or the feedback input. The deadtime control comparator has an effective 120 mV input offset which limits the minimum output deadtime to approximately the first 4% of the sawtooth–cycle time. This would result in a maximum duty cycle on a given output of 96% with the output control grounded, and 48% with it connected to the reference line. Additional deadtime may be imposed on the output by setting the deadtime–control input to a fixed voltage, ranging between 0 V to 3.3 V.

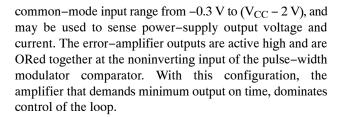

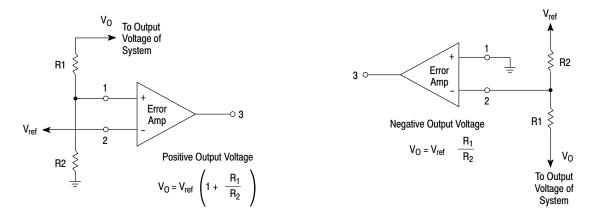

The pulse width modulator comparator provides a means for the error amplifiers to adjust the output pulse width from the maximum percent on–time, established by the deadtime control input, down to zero, as the voltage at the feedback pin varies from 0.5 V to 3.5 V. Both error amplifiers have a

**Functional Table**

| Input/Output<br>Controls | Output Function              | f <sub>out</sub> = |

|--------------------------|------------------------------|--------------------|

| Grounded                 | Single-ended PWM @ Q1 and Q2 | 1.0                |

| @ V <sub>ref</sub>       | Push-pull Operation          | 0.5                |

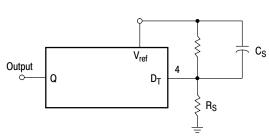

When capacitor  $C_T$  is discharged, a positive pulse is generated on the output of the deadtime comparator, which clocks the pulse-steering flip-flop and inhibits the output transistors, Q1 and Q2. With the output-control connected to the reference line, the pulse-steering flip-flop directs the modulated pulses to each of the two output transistors alternately for push-pull operation. The output frequency is equal to half that of the oscillator. Output drive can also be taken from Q1 or Q2, when single-ended operation with a maximum on-time of less than 50% is required. This is desirable when the output transformer has a ringback winding with a catch diode used for snubbing. When higher output-drive currents are required for single-ended operation, Q1 and Q2 may be connected in parallel, and the output-mode pin must be tied to ground to disable the flip-flop. The output frequency will now be equal to that of the oscillator.

The TL594 has an internal 5.0 V reference capable of sourcing up to 10 mA of load current for external bias circuits. The reference has an internal accuracy of  $\pm 1.5\%$  with a typical thermal drift of less than 50 mV over an operating temperature range of  $0^{\circ}$  to  $70^{\circ}$ C.

Figure 3. Oscillator Frequency versus Timing Resistance

Figure 4. Open Loop Voltage Gain and Phase versus Frequency

Figure 5. Percent Deadtime versus Oscillator Frequency

Figure 6. Percent Duty Cycle versus

Deadtime Control Voltage

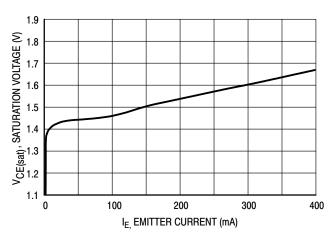

Figure 7. Emitter-Follower Configuration

Output Saturation Voltage versus

Emitter Current

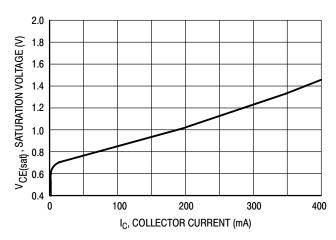

Figure 8. Common–Emitter Configuration

Output Saturation Voltage versus

Collector Current

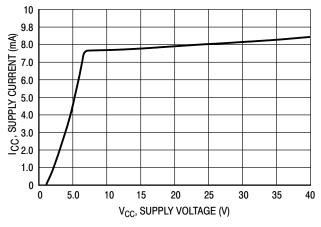

Figure 9. Standby Supply Current versus Supply Voltage

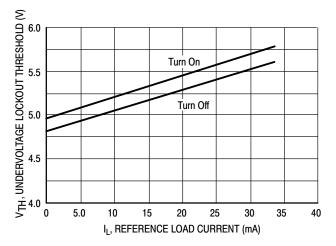

Figure 10. Undervoltage Lockout Thresholds versus Reference Load Current

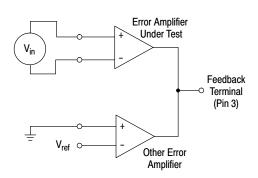

Figure 11. Error-Amplifier Characteristics

Figure 13. Common–Emitter Configuration

Test Circuit and Waveform

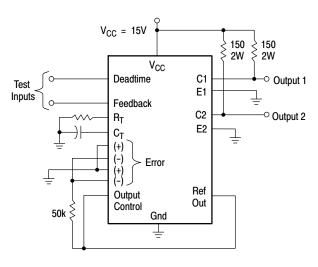

Figure 12. Deadtime and Feedback Control Circuit

Figure 14. Emitter–Follower Configuration Test Circuit and Waveform

Figure 15. Error-Amplifier Sensing Techniques

Figure 16. Deadtime Control Circuit

Figure 17. Soft-Start Circuit

Figure 18. Output Connections for Single-Ended and Push-Pull Configurations

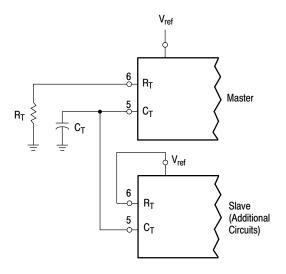

Figure 19. Slaving Two or More Control Circuits

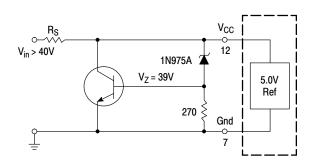

Figure 20. Operation with  $V_{in} > 40 \text{ V}$  Using External Zener

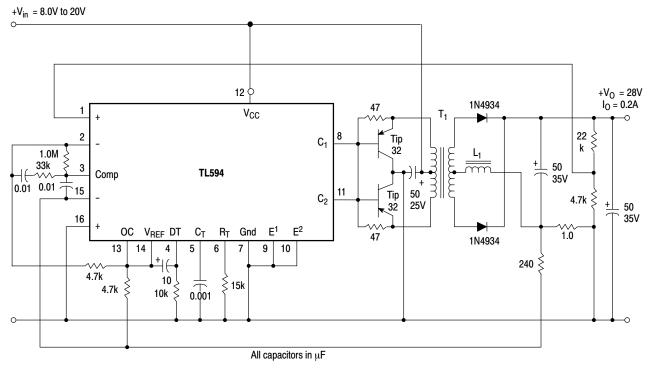

Figure 21. Pulse Width Modulated Push-Pull Converter

| Test                  | Conditions                                               | Results          | 14 25 mH @ 02 A                                                |

|-----------------------|----------------------------------------------------------|------------------|----------------------------------------------------------------|

| Line Regulation       | V <sub>in</sub> = 10 V to 40 V                           | 14 mV 0.28%      | L1 - 3.5 mH @ 0.3 A<br>T1 - Primary: 20T C.T. #28 AWG          |

| Load Regulation       | V <sub>in</sub> = 28 V, I <sub>O</sub> = 1.0 mA to 1.0 A | 3.0 mV 0.06%     | Secondary: 12OT C.T. #36 AWG<br>Core: Ferroxcube 1408P-L00-3CB |

| Output Ripple         | V <sub>in</sub> = 28 V, I <sub>O</sub> = 1.0 A           | 65 mVpp P.A.R.D. |                                                                |

| Short Circuit Current | $V_{in}$ = 28 V, $R_L$ = 0.1 $\Omega$                    | 1.6 A            |                                                                |

| Efficiency            | V <sub>in</sub> = 28 V, I <sub>O</sub> = 1.0 A           | 71%              |                                                                |

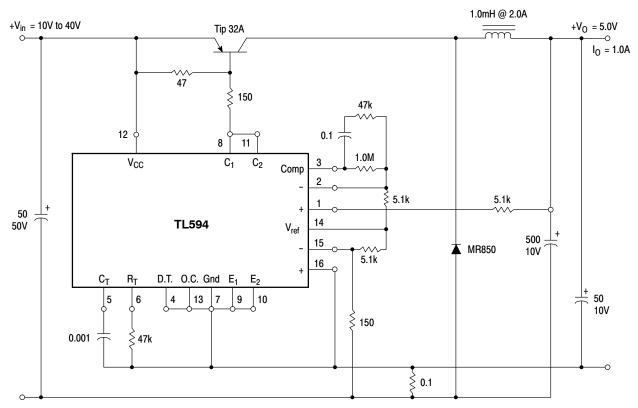

Figure 22. Pulse Width Modulated Step-Down Converter

| Test                  | Conditions                                        | Results          |

|-----------------------|---------------------------------------------------|------------------|

| Line Regulation       | V <sub>in</sub> = 8.0 V to 40 V                   | 3.0 mV 0.01%     |

| Load Regulation       | $V_{in}$ = 12.6 V, $I_{O}$ = 0.2 mA to 200 mA     | 5.0 mV 0.02%     |

| Output Ripple         | V <sub>in</sub> = 12.6 V, I <sub>O</sub> = 200 mA | 40 mVpp P.A.R.D. |

| Short Circuit Current | $V_{in}$ = 12.6 V, $R_L$ = 0.1 $\Omega$           | 250 mA           |

| Efficiency            | V <sub>in</sub> = 12.6 V, I <sub>O</sub> = 200 mA | 72%              |

### **ORDERING INFORMATION**

| Device       | Operating Temperature Range | Package              | Shipping <sup>†</sup> |

|--------------|-----------------------------|----------------------|-----------------------|

| TL594CDR2G   | −40 to 85°C                 | SOIC-16<br>(Pb-Free) | 2500 Tape & Reel      |

| TL594CDTBR2G | −40 to 85°C                 | TSSOP-16*            | 2500 Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. \*This package is inherently Pb–Free.

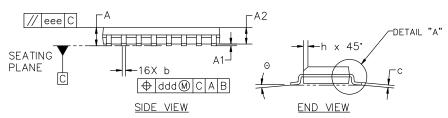

#### SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

**DATE 18 OCT 2024**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2018.

- 2. DIMENSION IN MILLIMETERS. ANGLE IN DEGREES.

- 3. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD PROTRUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15mm PER SIDE.

- 5. DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127mm TOTAL IN EXCESS OF THE 6 DIMENSION AT MAXIMUM MATERIAL CONDITION.

| MILLIMETERS |          |          |          |  |  |  |

|-------------|----------|----------|----------|--|--|--|

| DIM         | MIN      | NOM      | MAX      |  |  |  |

| А           | 1.35     | 1.55     | 1.75     |  |  |  |

| A1          | 0.10     | 0.18     | 0.25     |  |  |  |

| A2          | 1.25     | 1.37     | 1.50     |  |  |  |

| b           | 0.35     | 0.42     | 0.49     |  |  |  |

| С           | 0.19     | 0.22     | 0.25     |  |  |  |

| D           |          | 9.90 BSC |          |  |  |  |

| E           | 6.00 BSC |          |          |  |  |  |

| E1          | 3.90 BSC |          |          |  |  |  |

| е           | 1.27 BSC |          |          |  |  |  |

| h           | 0.25     |          | 0.50     |  |  |  |

| L           | 0.40     | 0.83     | 1.25     |  |  |  |

| L1          |          | 1.05 REF |          |  |  |  |

| Θ           | 0.       |          | 7.       |  |  |  |

| TOLERAN     | CE OF FC | RM AND   | POSITION |  |  |  |

| aaa         |          | 0.10     |          |  |  |  |

| bbb         |          | 0.20     |          |  |  |  |

| ccc         |          | 0.10     |          |  |  |  |

| ddd         |          | 0.25     | ·        |  |  |  |

| eee         |          | 0.10     |          |  |  |  |

#### RECOMMENDED MOUNTING FOOTPRINT

\*FOR ADDITIONAL INFORMATION ON OUR PB-FREE STRATEGY AND SOLDERING DETAILS, PLEASE DOWNLOAD THE onsemi SOLDERING AND MOUNTING TECHNIQUES REFERENCE MANUAL, SOLDERRM/D

| DOCUMENT NUMBER: | 98ASB42566B              | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.37 1 | .27P                                                                                                                                                                              | PAGE 1 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

### **SOIC-16 9.90x3.90x1.37 1.27P** CASE 751B

ISSUE M

**DATE 18 OCT 2024**

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code A = Assembly Location

WL = Wafer Lot

Y = Year

WW = Work Week

G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| STYLE 1:                              |                                                                                        | STYLE 2:                              |                                                             | STYLE 3:                              | S                                                                                                                                   | TYLE 4: |                   |

|---------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|

|                                       | COLLECTOR                                                                              | PIN 1.                                | CATHODE                                                     | PIN 1.                                | COLLECTOR, DYE #1                                                                                                                   | PIN 1.  | COLLECTOR, DYE #1 |

|                                       | BASE                                                                                   | 2.                                    | ANODE                                                       | 2.                                    | BASE. #1                                                                                                                            | 2.      |                   |

| 3.                                    | EMITTER                                                                                | 3.                                    | NO CONNECTION                                               | 3.                                    | EMITTER. #1                                                                                                                         | 3.      |                   |

| 4.                                    | NO CONNECTION                                                                          | 4.                                    | CATHODE                                                     | 4.                                    | COLLECTOR, #1                                                                                                                       | 4.      | COLLECTOR, #2     |

| 5.                                    | EMITTER                                                                                | 5.                                    | CATHODE                                                     | 5.                                    | COLLECTOR, #2                                                                                                                       | 5.      | COLLECTOR, #3     |

| 6.                                    | BASE                                                                                   | 6.                                    | NO CONNECTION                                               | 6.                                    | BASE, #2                                                                                                                            | 6.      | COLLECTOR, #3     |

| 7.                                    | COLLECTOR                                                                              | 7.                                    | ANODE                                                       | 7.                                    | EMITTER, #2                                                                                                                         | 7.      | COLLECTOR, #4     |

| 8.                                    | COLLECTOR                                                                              | 8.                                    | CATHODE                                                     | 8.                                    | COLLECTOR, #2                                                                                                                       | 8.      | COLLECTOR, #4     |

| 9.                                    | BASE                                                                                   | 9.                                    | CATHODE                                                     | 9.                                    | COLLECTOR, #3                                                                                                                       | 9.      | BASE, #4          |

| 10.                                   | EMITTER                                                                                | 10.                                   | ANODE                                                       | 10.                                   | BASE, #3                                                                                                                            | 10.     | EMITTER, #4       |

| 11.                                   | NO CONNECTION                                                                          | 11.                                   | NO CONNECTION                                               | 11.                                   | EMITTER, #3                                                                                                                         | 11.     |                   |

|                                       | EMITTER                                                                                | 12.                                   | CATHODE                                                     | 12.                                   |                                                                                                                                     | 12.     |                   |

| 13.                                   | BASE                                                                                   | 13.                                   |                                                             | 13.                                   | COLLECTOR, #4                                                                                                                       | 13.     | BASE, #2          |

| 14.                                   | COLLECTOR                                                                              | 14.                                   | NO CONNECTION                                               | 14.                                   | BASE, #4                                                                                                                            | 14.     |                   |

| 15.                                   | EMITTER                                                                                | 15.                                   | ANODE                                                       | 15.                                   | EMITTER, #4                                                                                                                         | 15.     |                   |

| 16.                                   | COLLECTOR                                                                              | 16.                                   | CATHODE                                                     | 16.                                   | COLLECTOR, #4                                                                                                                       | 16.     | EMITTER, #1       |

|                                       |                                                                                        |                                       |                                                             |                                       |                                                                                                                                     |         |                   |

| STYLE 5:                              |                                                                                        | STYLE 6:                              |                                                             | STYLE 7:                              |                                                                                                                                     |         |                   |

| PIN 1.                                | DRAIN, DYE #1                                                                          | PIN 1.                                | CATHODE                                                     | PIN 1.                                | SOURCE N-CH                                                                                                                         |         |                   |

| 2.                                    | DRAIN, #1                                                                              | 2.                                    | CATHODE                                                     | 2.                                    | COMMON DRAIN (OUTPUT)                                                                                                               |         |                   |

| 3.                                    | DRAIN, #2                                                                              | 3.                                    | CATHODE                                                     | 3.                                    | COMMON DRAIN (OUTPUT)                                                                                                               |         |                   |

| 4.                                    | DRAIN, #2                                                                              | 4.                                    | CATHODE                                                     | 4.                                    | GATE P-CH                                                                                                                           |         |                   |

| 5.                                    | DRAIN, #3                                                                              | 5.                                    |                                                             | 5.                                    | COMMON DRAIN (OUTPUT)                                                                                                               |         |                   |

| 6.                                    | DRAIN, #3                                                                              | 6.                                    |                                                             | 6.                                    | COMMON DRAIN (OUTPUT)                                                                                                               |         |                   |

| 7.                                    | DRAIN, #4                                                                              | 7.                                    | CATHODE                                                     | 7.                                    | COMMON DRAIN (OUTPUT)                                                                                                               |         |                   |

| 0                                     |                                                                                        |                                       |                                                             |                                       |                                                                                                                                     |         |                   |

| 8.                                    | DRAIN, #4                                                                              |                                       | CATHODE                                                     | 8.                                    | SOURCE P-CH                                                                                                                         |         |                   |

|                                       | GATE, #4                                                                               | 9.                                    | ANODE                                                       | 9.                                    | SOURCE P-CH                                                                                                                         |         |                   |

| 9.<br>10.                             | GATE, #4<br>SOURCE, #4                                                                 | 9.<br>10.                             | ANODE<br>ANODE                                              | 9.<br>10.                             | SOURCE P-CH<br>COMMON DRAIN (OUTPUT)                                                                                                |         |                   |

| 9.<br>10.<br>11.                      | GATE, #4<br>SOURCE, #4<br>GATE, #3                                                     | 9.<br>10.<br>11.                      | ANODE<br>ANODE<br>ANODE                                     | 9.<br>10.<br>11.                      | SOURCE P-CH<br>COMMON DRAIN (OUTPUT)<br>COMMON DRAIN (OUTPUT)                                                                       |         |                   |

| 9.<br>10.<br>11.<br>12.               | GATE, #4<br>SOURCE, #4<br>GATE, #3<br>SOURCE, #3                                       | 9.<br>10.<br>11.<br>12.               | ANODE<br>ANODE<br>ANODE<br>ANODE                            | 9.<br>10.<br>11.<br>12.               | SOURCE P-CH<br>COMMON DRAIN (OUTPUT)<br>COMMON DRAIN (OUTPUT)<br>COMMON DRAIN (OUTPUT)                                              |         |                   |

| 9.<br>10.<br>11.<br>12.<br>13.        | GATE, #4<br>SOURCE, #4<br>GATE, #3<br>SOURCE, #3<br>GATE, #2                           | 9.<br>10.<br>11.<br>12.<br>13.        | ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE                   | 9.<br>10.<br>11.<br>12.<br>13.        | SOURCE P-CH<br>COMMON DRAIN (OUTPUT)<br>COMMON DRAIN (OUTPUT)<br>COMMON DRAIN (OUTPUT)<br>GATE N-CH                                 |         |                   |

| 9.<br>10.<br>11.<br>12.<br>13.<br>14. | GATE, #4<br>SOURCE, #4<br>GATE, #3<br>SOURCE, #3<br>GATE, #2<br>SOURCE, #2             | 9.<br>10.<br>11.<br>12.<br>13.<br>14. | ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE          | 9.<br>10.<br>11.<br>12.<br>13.        | SOURCE P-CH COMMON DRAIN (OUTPUT) COMMON DRAIN (OUTPUT) COMMON DRAIN (OUTPUT) GATE N-CH COMMON DRAIN (OUTPUT)                       |         |                   |

| 9.<br>10.<br>11.<br>12.<br>13.<br>14. | GATE, #4<br>SOURCE, #4<br>GATE, #3<br>SOURCE, #3<br>GATE, #2<br>SOURCE, #2<br>GATE, #1 | 9.<br>10.<br>11.<br>12.<br>13.<br>14. | ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE | 9.<br>10.<br>11.<br>12.<br>13.<br>14. | SOURCE P-CH COMMON DRAIN (OUTPUT) COMMON DRAIN (OUTPUT) COMMON DRAIN (OUTPUT) GATE N-CH COMMON DRAIN (OUTPUT) COMMON DRAIN (OUTPUT) |         |                   |

| 9.<br>10.<br>11.<br>12.<br>13.<br>14. | GATE, #4<br>SOURCE, #4<br>GATE, #3<br>SOURCE, #3<br>GATE, #2<br>SOURCE, #2             | 9.<br>10.<br>11.<br>12.<br>13.<br>14. | ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE<br>ANODE          | 9.<br>10.<br>11.<br>12.<br>13.        | SOURCE P-CH COMMON DRAIN (OUTPUT) COMMON DRAIN (OUTPUT) COMMON DRAIN (OUTPUT) GATE N-CH COMMON DRAIN (OUTPUT)                       |         |                   |

| DOCUMENT NUMBER: | 98ASB42566B Electronic versions are uncontrolled except when accessed directly from the Document Repositor Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |      |             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.37 1                                                                                                                                                                   | .27P | PAGE 2 OF 2 |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

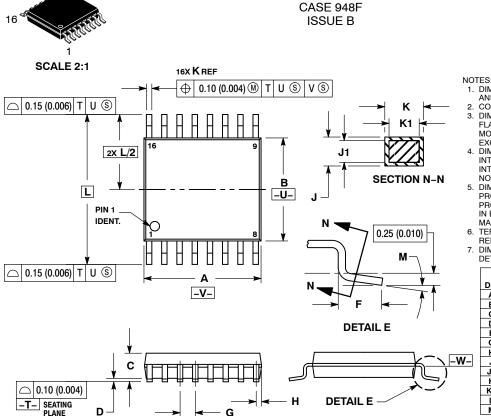

**DATE 19 OCT 2006**

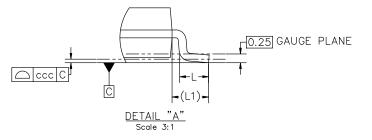

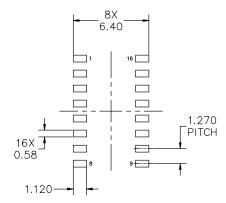

TSSOP-16 WB

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT

- EXCEED 0.15 (0.006) PER SIDE.

DIMENSION B DOES NOT INCLUDE

INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL

- IN TERLEAD FLASH OH PROTHOSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.90        | 5.10 | 0.193     | 0.200 |

| В   | 4.30        | 4.50 | 0.169     | 0.177 |

| С   |             | 1.20 |           | 0.047 |

| D   | 0.05        | 0.15 | 0.002     | 0.006 |

| F   | 0.50        | 0.75 | 0.020     | 0.030 |

| G   | 0.65 BSC    |      | 0.026 BSC |       |

| Н   | 0.18        | 0.28 | 0.007     | 0.011 |

| J   | 0.09        | 0.20 | 0.004     | 0.008 |

| J1  | 0.09        | 0.16 | 0.004     | 0.006 |

| K   | 0.19        | 0.30 | 0.007     | 0.012 |

| K1  | 0.19        | 0.25 | 0.007     | 0.010 |

| L   | 6.40 BSC    |      | 0.252 BSC |       |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |

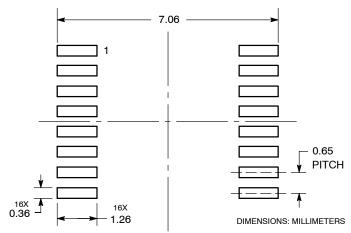

#### **RECOMMENDED** SOLDERING FOOTPRINT\*

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXX = Specific Device Code Α = Assembly Location

= Wafer Lot L = Year W = Work Week G or • = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASH70247A | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TSSOP-16    |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales