**TO-92 (TO-226)** CASE 29-11 **ISSUE AM**

**DATE 09 MAR 2007**

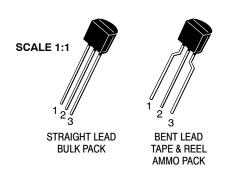

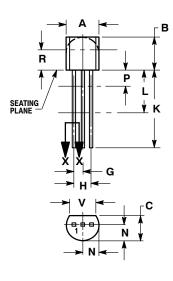

STRAIGHT LEAD **BULK PACK**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982.

CONTROLLING DIMENSION: INCH.

CONTOUR OF PACKAGE BEYOND DIMENSION R

IS UNCONTROLLED.

- LEAD DIMENSION IS UNCONTROLLED IN P AND BEYOND DIMENSION K MINIMUM.

|     | INC   | HES   | MILLIMETERS |       |  |

|-----|-------|-------|-------------|-------|--|

| DIM | MIN   | MAX   | MIN         | MAX   |  |

| Α   | 0.175 | 0.205 | 4.45        | 5.20  |  |

| В   | 0.170 | 0.210 | 4.32        | 5.33  |  |

| С   | 0.125 | 0.165 | 3.18        | 4.19  |  |

| D   | 0.016 | 0.021 | 0.407       | 0.533 |  |

| G   | 0.045 | 0.055 | 1.15        | 1.39  |  |

| Н   | 0.095 | 0.105 | 2.42        | 2.66  |  |

| J   | 0.015 | 0.020 | 0.39        | 0.50  |  |

| K   | 0.500 |       | 12.70       |       |  |

| L   | 0.250 |       | 6.35        |       |  |

| N   | 0.080 | 0.105 | 2.04        | 2.66  |  |

| P   |       | 0.100 |             | 2.54  |  |

| R   | 0.115 |       | 2.93        |       |  |

| ٧   | 0.135 |       | 3.43        |       |  |

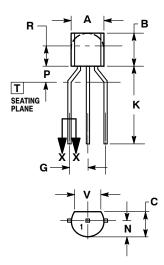

**BENT LEAD TAPE & REEL** AMMO PACK

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- AND BEYOND DIMENSION K MINIMUM.

|     | MILLIMETERS |      |  |  |  |  |

|-----|-------------|------|--|--|--|--|

| DIM | MIN MAX     |      |  |  |  |  |

| Α   | 4.45        | 5.20 |  |  |  |  |

| В   | 4.32        | 5.33 |  |  |  |  |

| С   | 3.18        | 4.19 |  |  |  |  |

| D   | 0.40        | 0.54 |  |  |  |  |

| G   | 2.40        | 2.80 |  |  |  |  |

| J   | 0.39        | 0.50 |  |  |  |  |

| K   | 12.70       |      |  |  |  |  |

| N   | 2.04        | 2.66 |  |  |  |  |

| P   | 1.50        | 4.00 |  |  |  |  |

| R   | 2.93        |      |  |  |  |  |

| V   | 3.43        |      |  |  |  |  |

## **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42022B    | Electronic versions are uncontrolled except when accessed directly from the Document R Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | TO-92 (TO-226) |                                                                                                                                                                        | PAGE 1 OF 2 |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves onsem and of 15GTI in are trademarks of Semiconductor Components industries, LLC due onsem or its substitutines in the Office States and/or other countries. Onsem reserves the right to make changes without further notice to any products herein. onsem makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

# **TO-92 (TO-226)** CASE 29-11 ISSUE AM

# **DATE 09 MAR 2007**

| STYLE 1:<br>PIN 1.<br>2.<br>3.  | EMITTER<br>BASE<br>COLLECTOR        | STYLE 2:<br>PIN 1.<br>2.<br>3.  | BASE<br>EMITTER<br>COLLECTOR               | STYLE 3:<br>PIN 1.<br>2.<br>3.  | ANODE<br>ANODE<br>CATHODE           | STYLE 4:<br>PIN 1.<br>2.<br>3.  | CATHODE<br>CATHODE<br>ANODE       | STYLE 5:<br>PIN 1.<br>2.<br>3.  | DRAIN<br>SOURCE<br>GATE           |

|---------------------------------|-------------------------------------|---------------------------------|--------------------------------------------|---------------------------------|-------------------------------------|---------------------------------|-----------------------------------|---------------------------------|-----------------------------------|

| STYLE 6:<br>PIN 1.<br>2.<br>3.  | GATE<br>SOURCE & SUBSTRATE<br>DRAIN | STYLE 7:<br>PIN 1.<br>2.<br>3.  | SOURCE<br>DRAIN<br>GATE                    | STYLE 8:<br>PIN 1.<br>2.<br>3.  | DRAIN<br>GATE<br>SOURCE & SUBSTRATE | STYLE 9:<br>PIN 1.<br>2.<br>3.  | BASE 1<br>EMITTER<br>BASE 2       | STYLE 10:<br>PIN 1.<br>2.<br>3. | CATHODE<br>GATE<br>ANODE          |

| STYLE 11:<br>PIN 1.<br>2.<br>3. | ANODE<br>CATHODE & ANODE<br>CATHODE | STYLE 12:<br>PIN 1.<br>2.<br>3. | MAIN TERMINAL 1<br>GATE<br>MAIN TERMINAL 2 | STYLE 13:<br>PIN 1.<br>2.<br>3. | ANODE 1<br>GATE<br>CATHODE 2        | STYLE 14:<br>PIN 1.<br>2.<br>3. | EMITTER<br>COLLECTOR<br>BASE      | STYLE 15:<br>PIN 1.<br>2.<br>3. | ANODE 1<br>CATHODE<br>ANODE 2     |

| STYLE 16:<br>PIN 1.<br>2.<br>3. | ANODE<br>GATE<br>CATHODE            | STYLE 17:<br>PIN 1.<br>2.<br>3. | COLLECTOR<br>BASE<br>EMITTER               | STYLE 18:<br>PIN 1.<br>2.<br>3. | ANODE<br>CATHODE<br>NOT CONNECTED   | STYLE 19:<br>PIN 1.<br>2.<br>3. | GATE<br>ANODE<br>CATHODE          | STYLE 20:<br>PIN 1.<br>2.<br>3. | NOT CONNECTED<br>CATHODE<br>ANODE |

| STYLE 21:<br>PIN 1.<br>2.       | COLLECTOR<br>EMITTER                | STYLE 22:<br>PIN 1.             | SOURCE<br>GATE                             | STYLE 23:<br>PIN 1.<br>2.       | GATE<br>SOURCE<br>DRAIN             | STYLE 24:<br>PIN 1.<br>2.       | EMITTER                           | STYLE 25:<br>PIN 1.<br>2.       | MT 1                              |

|                                 | Vcc                                 | STYLE 27:<br>PIN 1.<br>2.<br>3. | MT<br>SUBSTRATE<br>MT                      | STYLE 28:<br>PIN 1.<br>2.<br>3. | CATHODE<br>ANODE<br>GATE            | PIN 1.                          | NOT CONNECTED<br>ANODE<br>CATHODE | PIN 1.<br>2.                    | DRAIN<br>GATE                     |

| 2.                              | GATE<br>DRAIN<br>SOURCE             | STYLE 32:<br>PIN 1.<br>2.<br>3. | BASE<br>COLLECTOR<br>EMITTER               | STYLE 33:<br>PIN 1.<br>2.<br>3. | RETURN<br>INPUT<br>OUTPUT           | STYLE 34:<br>PIN 1.<br>2.<br>3. | INPUT<br>GROUND<br>LOGIC          | PIN 1.                          | GATE                              |

| DOCUMENT NUMBER: 98ASB42022B Electronic versions are uncontrolled except when are Printed versions are uncontrolled except when stam |                |  |             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------|--|-------------|--|--|

| DESCRIPTION:                                                                                                                         | TO-92 (TO-226) |  | PAGE 2 OF 2 |  |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.