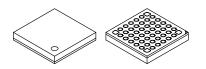

## LFLGA49 5x5 / FLGA49J CASE 569AC ISSUE A

**DATE 17 JAN 2014**

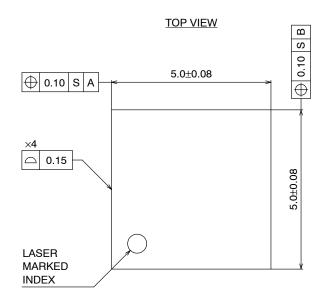

# 0.45±0.03 0.45±0.03 0.55 Q F E D C B A

0.65

**BOTTOM VIEW**

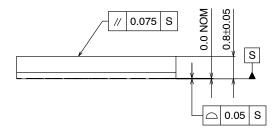

## SIDE VIEW

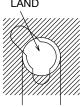

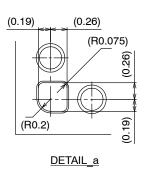

## NSMD Off set Via type

Aperture of Solder Resist

## GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

Y = Year

45-Ø0.35±0.03

0.03 (M) S A B

M = Month

DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: |                       | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | LFLGA49 5X5 / FLGA49J |                                                                                                                                                                                     | PAGE 1 OF 2 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

**DATE 17 JAN 2014**

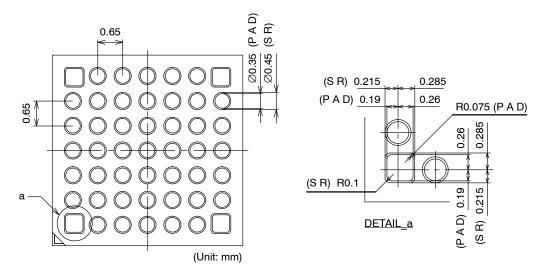

## **SOLDERING FOOTPRINT\***

#### NOTES:

- 1. The measurements are not to guarantee but for reference only.

- 2. Module level verification after set designing must be implemented. Validating solderbility and Reliability verification for joint areas such as Exposed Die-pad and must be carried out. Drawing above is a design applicable for NSMD pad specification. For SMD pad specification, layout of SR opening size specified as PKG terminal size = Pad size is to be complied.

| DOCUMENT NUMBER: | 98AON67020E           | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | LFLGA49 5X5 / FLGA49J |                                                                                                                                                                                     | PAGE 2 OF 2 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.