## Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

## **AN-9087**

# **600V Motion SPM® 3 ver5 Series Thermal Performance Information**

## Overview

Semiconductor devices are very sensitive to junction temperature. As the junction temperature increases, the operating characteristic of a device is altered and the failure rate increases exponentially. This makes the thermal design of the package very important in the device development stage and in applications. In particular, contact pressure or mounting torque can affect thermal performance. This application note shows a correlation between the mounting torque and the thermal resistance.

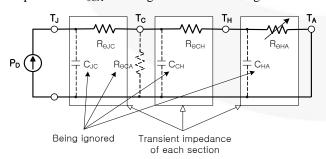

To gain insight into the device's thermal performance, it is common to introduce thermal resistance, which is defined as the difference in temperature between two adjacent isothermal surfaces divided by the total power flow between them. For semiconductor devices, junction temperature, T<sub>J</sub>, and reference temperature, Tx, are typically used. The amount of power flow is equal to the power dissipation of a device during operation. The selection of a reference point is arbitrary, but the hottest spot on the back of a device on which a heat sink is attached is usually chosen. This is called junction-to-case thermal resistance,  $R_{\theta JC}$ . When the reference point is an ambient temperature, it is called junction-to-ambient thermal resistance,  $R_{\theta JA}$ . Both are used for characterization of a device's thermal performance.  $R_{\theta JC}$ is usually used for a device mounted on a heat-sink, while  $R_{\theta JA}$  is for a device used without a heat sink. Figure 1 shows a thermal network of heat flow from junction-to-ambient for the motion SPM, including a heat sink. The dotted component of  $R_{\theta CA}$  can be ignored due to its large value.

Figure 1. Transient Thermal Equivalent Circuit with Heat Sink

The thermal resistance of motion SPM is defined as:

$$R_{\theta JC} = \frac{T_J - T_C}{P_D} \tag{1}$$

where  $R_{\theta JC}$  (°C/W) is the junction-to-case thermal resistance and  $P_D$  (W),  $T_J$  (°C), and  $T_C$  (°C) are power dissipation per device, junction temperature, and case reference temperature, respectively. By replacing  $T_C$  with ambient temperature ( $T_A$ ), the junction-to-ambient thermal resistance  $R_{\theta JA}$  can be obtained as:

$$R_{\theta JA} = \frac{T_J - T_A}{P_D} \tag{2}$$

where  $R_{\theta JA}$  indicates the total thermal performance of the SPM, including the heat sink.  $R_{\theta JA}$  is basically a summation of thermal resistances;  $R_{\theta JC}$ ,  $R_{\theta CH}$  and  $R_{\theta HA}$ :

$$R_{\theta,IA} = R_{\theta,IC} + R_{\theta CH} + R_{\theta HA} \tag{3}$$

where  $R_{\theta CH}$  is contact thermal resistance between the package case and the heat sink, where the gap is filled with thermal grease, and  $R_{\theta HA}$  is heat sink thermal resistance. From Equation (3), it is clear that minimizing not only  $R_{\theta JC}$ , but also  $R_{\theta CH}$  and  $R_{\theta HA}$ , is essential to maximize the power capability of the SPM. An infinite heat sink would result if  $R_{\theta CH}$  and  $R_{\theta HA}$  are assumed to be zero and the case temperature,  $T_C$ , would be locked at the fixed ambient temperature,  $T_A$ . Usually, the value of  $R_{\theta CH}$  is proportional to the thermal grease thickness and governed by the skills at the assembly site, while  $R_{\theta HA}$  can be adjusted slihgtly by selecting an appropriate heat sink.

In practical operations, the power loss,  $P_D$ , is not a constant DC value, but rather an AC value. Therefore, the transient RC equivalent circuit shown in Figure 1 should be considered. For pulsed power loss, the thermal capacitance delays the rise in junction temperature and thus permits a heavier loading of the 600 V Motion SPM 3 Series.

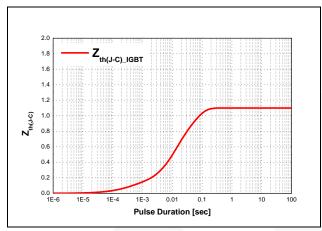

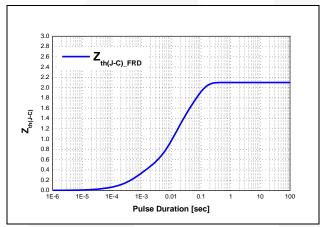

Figure 2 and Figure 3 show the thermal impedance curves of FSBB30CH60D. The thermal resistance goes into

AN-9087 APPLICATION NOTE

saturation in less than one second. Other types of Motion SPM products also show similar characteristics.

Figure 2. Thermal Impedance Curve IGBT of FSBB30CH60D

Figure 3. Thermal Impedance Curve FRD of FSBB30CH60D

If more details are required, please refer to *AN-9071*, which shows the thermal performance of the SPM 45 Series associated with various types of heat sinks.

## Measurement Method of T<sub>J</sub>

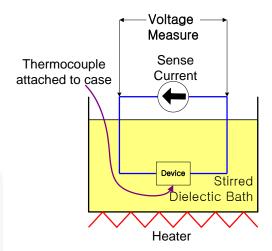

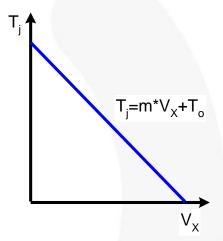

At the thermal resistance test,  $T_J$ ,  $T_C$  (or  $T_A$ ), and  $P_D$  should be measured. Since  $T_C$ ,  $T_A$ , and  $P_D$  can be measured directly, the only unknown constant is the junction temperature,  $T_J$ . The Electrical Test Method (ETM) is widely used to measure the junction temperature. The ETM method is based on the relationship between forward-drop voltage and junction temperature. This relationship is an intrinsic electro-thermal property of semiconductor junctions and is found to be nearly linear when a constant forward-biased current (sense current) is applied. This voltage drop of the junction is called Temperature Sensitive Parameter (TSP). Figure 4 illustrates the concept of measuring the voltage drop vs. junction temperature for a diode. The device under test (DUT) is embedded in hot fluid to be heated to desired testing temperatures.

Figure 4. Illustration of the Bath Method for TSP Measurement

Figure 5. Example of a TSP Plot with Constant Sense Current

When the DUT attains thermal equilibrium with the hot fluid, a sense current is applied to the junction. Then the voltage drop across the junction is measured as a function of the junction temperatures. The amount of sense current should be small enough not to heat the DUT. For instance,  $1-10~\mathrm{mA}$  can be used, depending on the device type. The measurements are repeated over a specific temperature range with some specified temperature steps. Figure 9 shows a typical result.

The relationship between the junction temperature and voltage drop at a given temperature can be expressed as:

$$T_J = m * V_X + T_O \tag{4}$$

The slope, m (°CV) and the temperature coordinate-intercept,  $T_O$  (°C), are used to quantify this straight line relationship. The reciprocal of the slope is often referred to as the "K factor (V/°C)." In this case,  $V_X$  (V) is the TSP.

For semiconductor junctions; the slope, m, of the straight line in Figure 5 is always negative, i.e., the forward conduction voltage decreases with increasing junction

temperature. This process of obtaining Equation (4) is called the calibration procedure for a given device.

During the thermal resistance measurement test, the junction temperature can be estimated from the measurement of the voltage drop at a given sense current during the calibration procedure and Equation (4). The TSP varies by device. If a specific device does not have the diode voltage TSP, transistor saturation voltage can be used instead. Gate turn-on voltage can be used as TSP for an IGBT or a MOSFET.

## **Measurement Procedure**

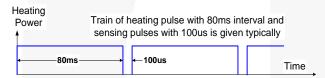

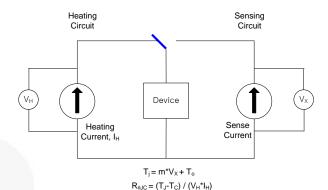

The thermal resistance test begins by applying a continuous power of known current and voltage to the DUT. The continuous power heats up the DUT to a thermally equilibrated state. While the device is heating, a continuous train of sampling pulses monitors the TSP, i.e., the voltage drop or the same as the junction temperature. The TSP sampling pulse must provide a sense current equal to that used during the calibration procedure for obtaining equation (4). While monitoring the TSP, adjust the applied power so as to insure a sufficient rise in  $T_J$ . Adjusting the applied power to achieve a  $T_J$  increase of about  $100^{\circ}$ C above the reference temperature will generate enough temperature difference to ensure a good measurement resolution. A typical example is shown in Figure 6.

Figure 6. Example of a Power and Sample Pulses Train During the  $R_{\rm JC}$  Measurement of a SPM-IGBT

The TSP sampling time must be very short so as not to allow for any appreciable cooling of the junction prior to reapplying power. The power and sensing pulse train shown in Figure 6 has a duty cycle of 99.9%, which for all practical purposes is considered to be continuous power. Obviously, most of the total power is applied to the DUT in Figure 7.

Once  $T_J$  reaches thermal equilibrium, its value along with the reference temperature  $T_C$  and applied power P is recorded. Using the measured values and equation (1), the junction-to-case thermal resistance  $R_{\theta JC}$  can be estimated.  $R_{\theta JC}$  here indicates the ability of a device to dissipate power in an ideal environment, that is, mounted with an infinite or temperature-controlled heat sink.

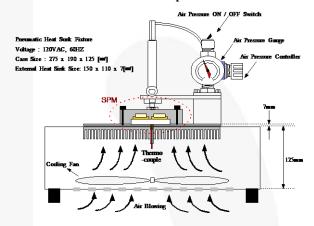

Figure 8 shows the thermal resistance measurement environment for SPMs. The SPM is placed on a heat sink having a large heat carrying capacity. Thermal grease is applied between the SPM and heat sink to prevent an air gap.

Figure 7. Illustration of the Thermal Resistance Test Method

Concept

Figure 8. The Thermal Measurement Environment of the SPM

## Measurement Results of T<sub>J</sub>

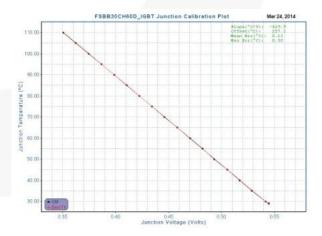

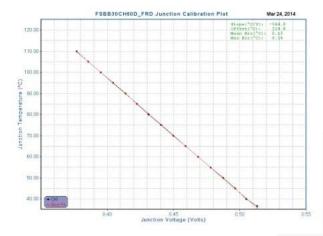

The figures below are measurement results of device junction calibration of **FSBB30CH60D**: Figure 9 is for IGBT and Figure 1010 for FRD. The slope, m (°C/V), and the temperature coordinate-intercept,  $T_o$  (°C), are shown in Table 1.

Figure 9. Results of Device Junction Calibration for IGBT

Figure 10. Results of Device Junction Calibration for FRD

Table 1. m (°C/V) and Temperature Coordinate-Intercept,  $T_0$  (V) for FNA21012A

| Device      |      | m(°C/V) | TO(°C) | Sensing<br>Current |  |

|-------------|------|---------|--------|--------------------|--|

| FSBB30CH60D | IGBT | -419.9  | 257.3  | 10 mA              |  |

|             | FRD  | -544    | 314.8  |                    |  |

## Thermal Resistance, R<sub>θJC</sub>

The thermal resistance from junction to case,  $R_{\theta JC}$ , can be calculated from Equation (1). Usaully, the themal resistance is measured at two different points, package center and chip center. Table 2 shows values measured at chip center.

Table 2. R<sub>0JC</sub>: Thermal Resistance, °C/W

| Classification | SPL | P(W)  | TJ   | TC   | RθJC |

|----------------|-----|-------|------|------|------|

| FSBB30CH60D    | #1  | 28.74 | 51.0 | 31.9 | 0.66 |

| Chip Center    | #2  | 28.59 | 51.6 | 32.7 | 0.66 |

The  $R_{\theta JC}$  on SPM product datasheets is based on chip center values and has margin to cover manufacturing variations.

## **Actual Measure Point**

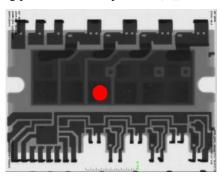

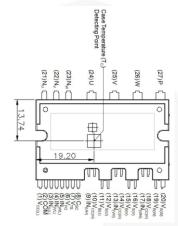

Figure 11 shows real measuring points and Figure 12 shows the detecting point of case temperature (T<sub>C</sub>) in a datasheet.

Figure 11. Actual Measurement Points

Figure 12. Case Temperature Detecting Point for Datasheet Specification

The  $R_{\theta JC}$ \_chip center is measured at the red point, while the IGBT at the same red point is directly heated. The  $R_{\theta JC}$ \_chip center is not affected by the package warpage and the heat sink warpage because this point is contact ahead of the rest part.

The  $R_{\theta JC}$ -package center is measured at the red point when the IGBT in yellow point is heated.

## **Related Resources**

FSBB30CH60D - 600V Motion SPM® 3 ver5 Series- Product Folder

AN-9071 – Smart Power Module-SPM<sup>TM</sup> in μMini DIP SPM Thermal Performance Information

AN-9085 – 600V Motion SPM® 3 ver5 Series, User's Guide

AN-9086 – 600V Motion SPM<sup>®</sup> 3 Package Mounting Guide

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

- Life support devices or systems are devices or systems which, (a)

are intended for surgical implant into the body, or (b) support or

sustain life, or (c) whose failure to perform when properly used in

accordance with instructions for use provided in the labeling, can

be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative