# AND9368/D

CMOS 16-BIT MICROCONTROLLER LC885800 SERIES USER'S MANUAL

www.onsemi.com

### **APPLICATION NOTE**

Microcontroller Business Unit ON Semiconductor

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the desi

| Chapter 1 Overview1-1                          |

|------------------------------------------------|

| 1.1 Overview1-1                                |

| 1.2 Features ······1-1                         |

| 1.3 Pinout                                     |

| 1.4 System Block Diagram ······1-7             |

| 1.5 Pin Functions ······1-8                    |

| 1.6 Port Output Types ······ 1-10              |

|                                                |

| Chapter 2 Internal System Configuration2-1     |

| 2.1 Memory Space2-1                            |

| 2.1.1 Program/Data Space 2-2                   |

| 2.1.2 Data/Program Stack/SFR Space 2-2         |

| 2.2 Program Counter (PC)2-3                    |

| 2.3 General-purpose Registers2-4               |

| 2.3.1 Overview                                 |

| 2.3.2 R0 to R72-4                              |

| 2.3.3 R82-4                                    |

| 2.3.4 R9 2-4                                   |

| 2.3.5 R10 to R132-4                            |

| 2.3.6 R14 (PSW)                                |

| 2.3.7 R15 (SP) 2-5                             |

| 2.4 Program Memory (ROM) ·····2-6              |

| 2.5 Data Memory (RAM)·····2-6                  |

| 2.6 Special Function Registers (SFRs)2-7       |

|                                                |

| Chapter 3 Peripheral System Configuration3-1   |

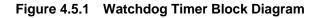

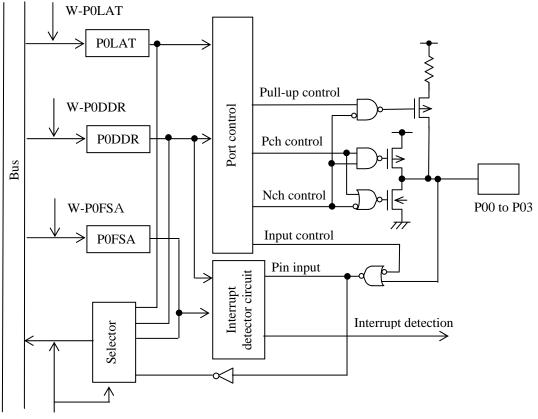

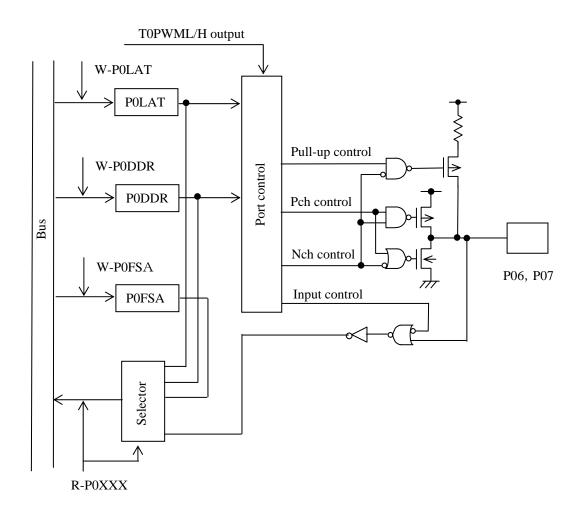

| 3.1 Port 0                                     |

| 3.1.1 Overview 3-1                             |

| 3.1.2 Functions                                |

| 3.1.3 Related Registers 3-2                    |

| 3.1.4 Register Settings and Port States 3-3    |

| 3.1.5 HALT, HOLD, and HOLDX Mode Operation 3-3 |

| 3.2 Port 1                                     |

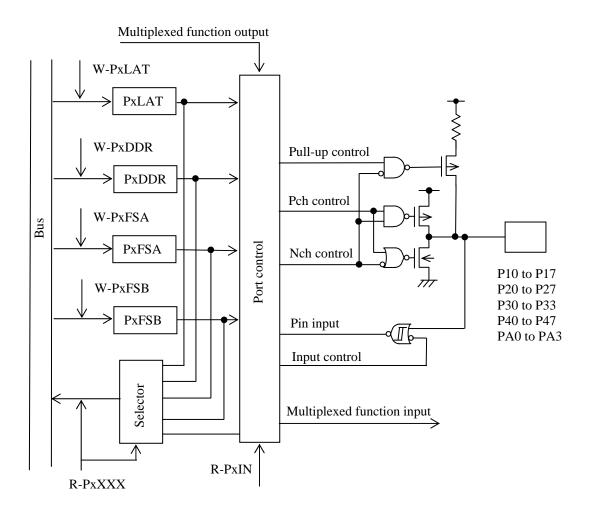

| 3.2.1 Overview                                 |

| 3.2.2 Functions                                |

| 3.2.3 Related Registers 3-4                    |

| 3.2.4 Register Settings and Port States        |

| 3.2.5 HALT, HOLD, and HOLDX Mode Operation 3-9 |

| 3.3 Port 2                                     |

| 3.3.1  | Overview                             |

|--------|--------------------------------------|

| 3.3.2  | Functions                            |

| 3.3.3  | Related Registers                    |

| 3.3.4  | Register Settings and Port States    |

| 3.3.5  | HALT, HOLD, and HOLDX Mode Operation |

| 3.4 Po | rt 3 3-16                            |

| 3.4.1  | Overview                             |

| 3.4.2  | Functions3-16                        |

| 3.4.3  | Related Registers                    |

| 3.4.4  | Register Settings and Port States    |

| 3.4.5  | HALT, HOLD, and HOLDX Mode Operation |

| 3.5 Po | rt 4 3-20                            |

| 3.5.1  | Overview                             |

| 3.5.2  | Functions                            |

| 3.5.3  | Related Registers 3-20               |

| 3.5.4  | Register Settings and Port States    |

| 3.5.5  | HALT, HOLD, and HOLDX Mode Operation |

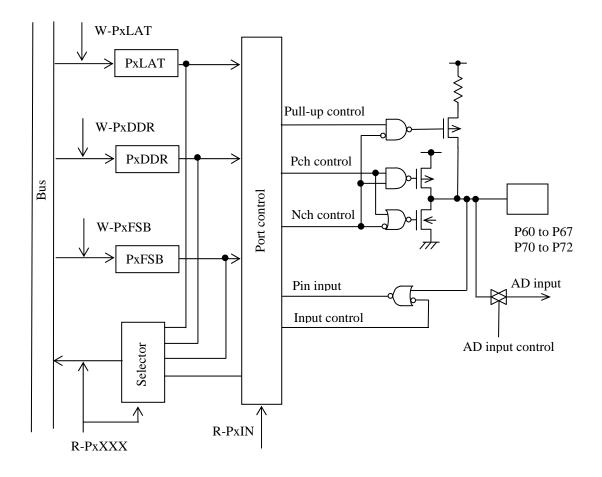

| 3.6 Po | rt 6 3-26                            |

| 3.6.1  | Overview                             |

| 3.6.2  | Functions······3-26                  |

| 3.6.3  | Related Registers ·······3-26        |

| 3.6.4  | Register Settings and Port States    |

| 3.6.5  | HALT, HOLD, and HOLDX Mode Operation |

| 3.7 Po | rt 7 3-30                            |

| 3.7.1  | Overview                             |

| 3.7.2  | Functions······3-30                  |

| 3.7.3  | Related Registers ·······3-30        |

| 3.7.4  | Register Settings and Port States    |

| 3.7.5  | HALT, HOLD, and HOLDX Mode Operation |

| 3.8 Po | rt A ····· 3-32                      |

| 3.8.1  | Overview                             |

| 3.8.2  | Functions                            |

| 3.8.3  | Related Registers                    |

| 3.8.4  | Register Settings and Port States    |

| 3.8.5  | HALT, HOLD, and HOLDX Mode Operation |

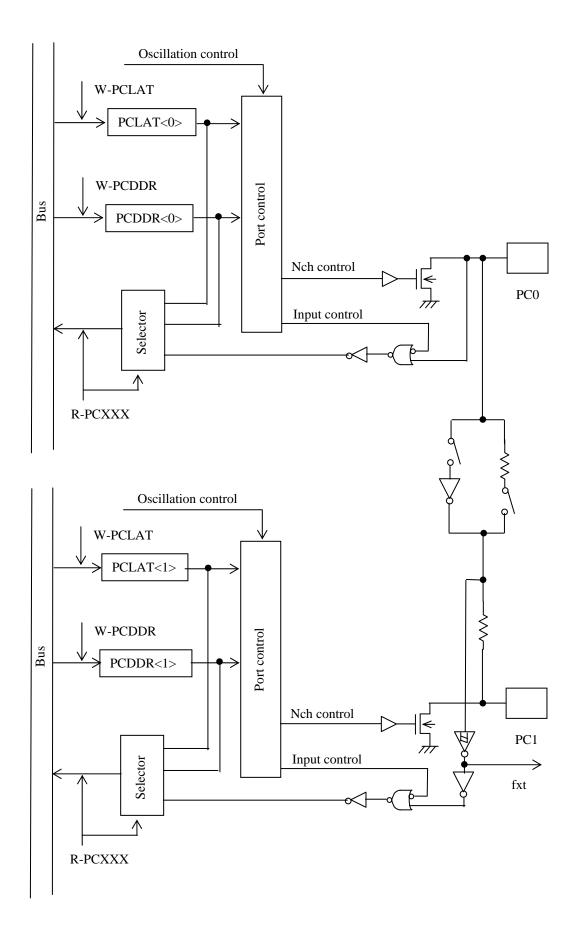

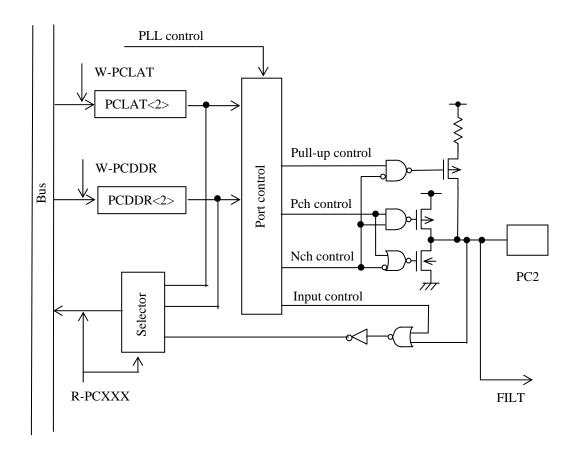

| 3.9 Po | rt C 3-37                            |

| 3.9.1  | Overview                             |

| 3.9.2  | Functions                            |

| 3.9.3  | Related Registers                    |

| 3.9.4  | Register Settings and Port States    |

|        |                                      |

|          | HALT, HOLD, and HOLDX Mode Operation                              |

|----------|-------------------------------------------------------------------|

| 3.10 Ex  | ternal Interrupt Functions (INTn)······ 3-39                      |

| 3.10.1   | Overview                                                          |

| 3.10.2   | Functions 3-39                                                    |

| 3.10.3   | Related Registers                                                 |

| 3.10.4   | INTn Input Mode Port Settings ······3-45                          |

| 3.11 Po  | rt 0 Interrupt Functions ······ 3-47                              |

| 3.11.1   | Overview                                                          |

| 3.11.2   | Functions                                                         |

|          | Related Registers                                                 |

|          | Port 0 Interrupt Settings                                         |

| 3.12 Tin | ner 0(T0)                                                         |

| 3.12.1   | Overview3-50                                                      |

| 3.12.2   | Functions ·······3-50                                             |

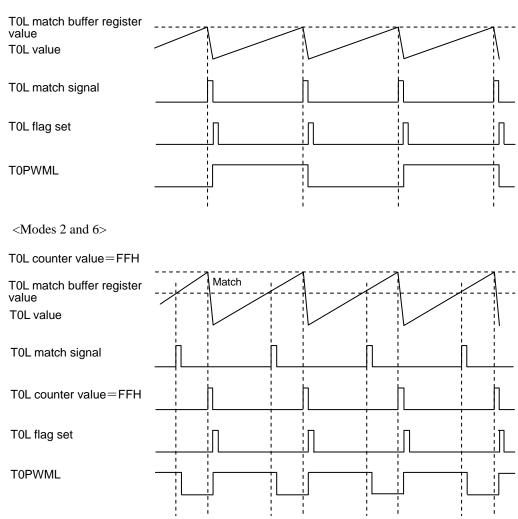

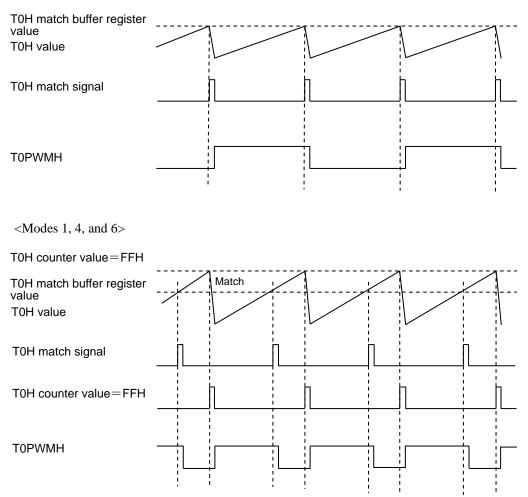

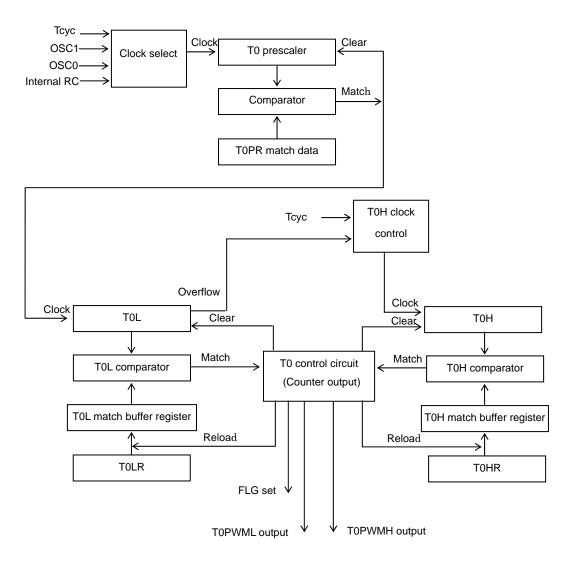

| 3.12.3   | Circuit Configuration ······3-52                                  |

| 3.12.4   | Related Registers ·······3-56                                     |

| 3.12.5   | Timer 0 Output Port Settings ···································· |

| 3.13 Tin | ner 1(T1)                                                         |

| 3.13.1   | Overview3-59                                                      |

| 3.13.2   | Functions ·······3-59                                             |

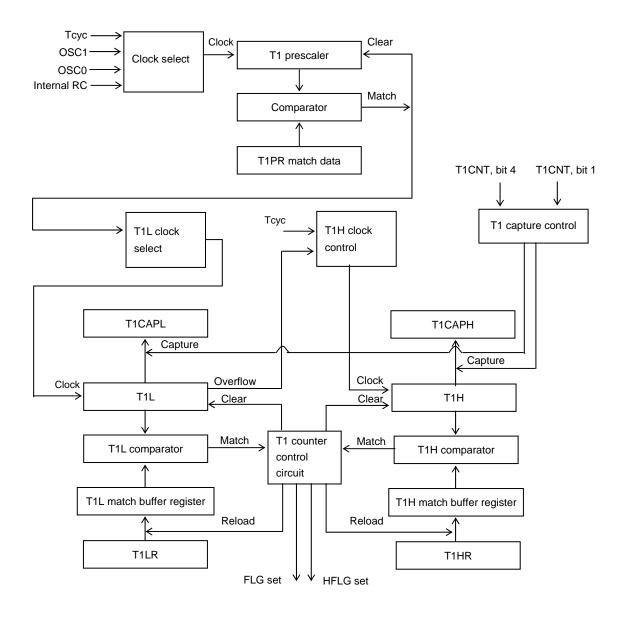

| 3.13.3   | Circuit Configuration ······3-60                                  |

| 3.13.4   | Related Registers ······3-63                                      |

| 3.14 Tin | ner 2(T2)                                                         |

| 3.14.1   | Overview3-65                                                      |

| 3.14.2   | Functions ·······3-65                                             |

| 3.14.3   | Circuit Configuration ·······3-66                                 |

| 3.14.4   | Related Registers ······3-71                                      |

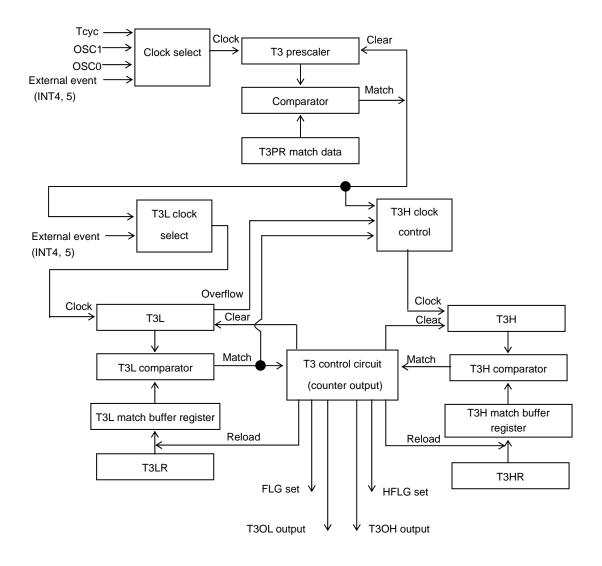

| 3.15 Tin | ner 3(T3)                                                         |

| 3.15.1   | Overview                                                          |

| 3.15.2   | Functions                                                         |

| 3.15.3   | Circuit Configuration ······3-76                                  |

| 3.15.4   | Related Registers ······3-81                                      |

| 3.15.5   | Timer 3 Output Port Settings                                      |

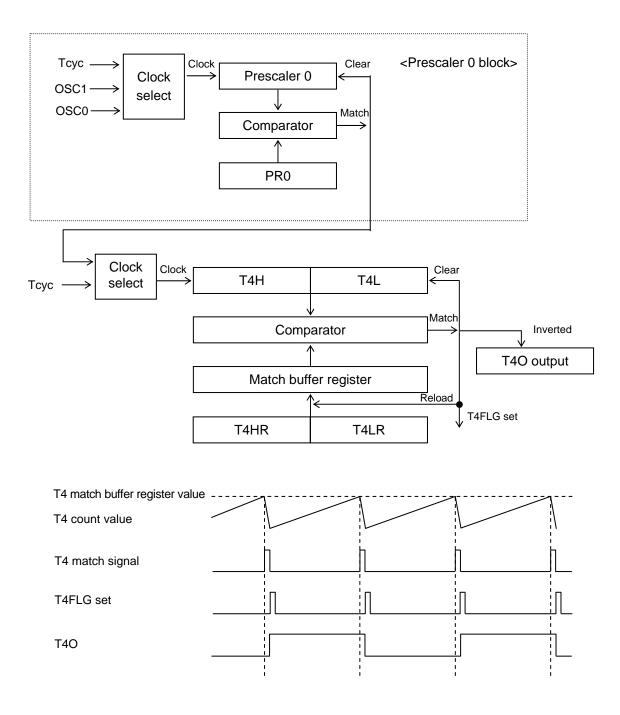

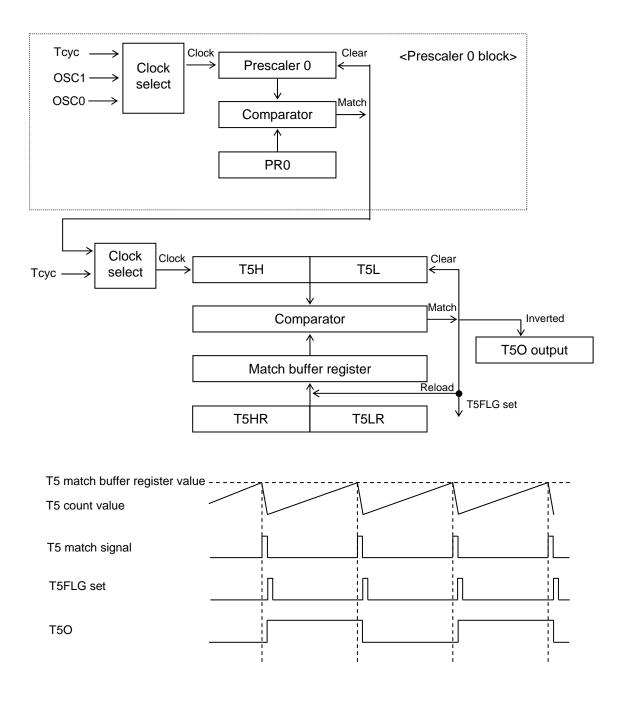

| 3.16 Tin | ner 4 and Timer 5 (T4, T5)                                        |

| 3.16.1   | Overview                                                          |

| 3.16.2   | Functions                                                         |

| 3.16.3   | Circuit Configuration ·······3-86                                 |

| 3.16.4   | Related Registers ······3-90                                      |

| 3.16.5   | Timer 4 and Timer 5 Output Port Settings                          |

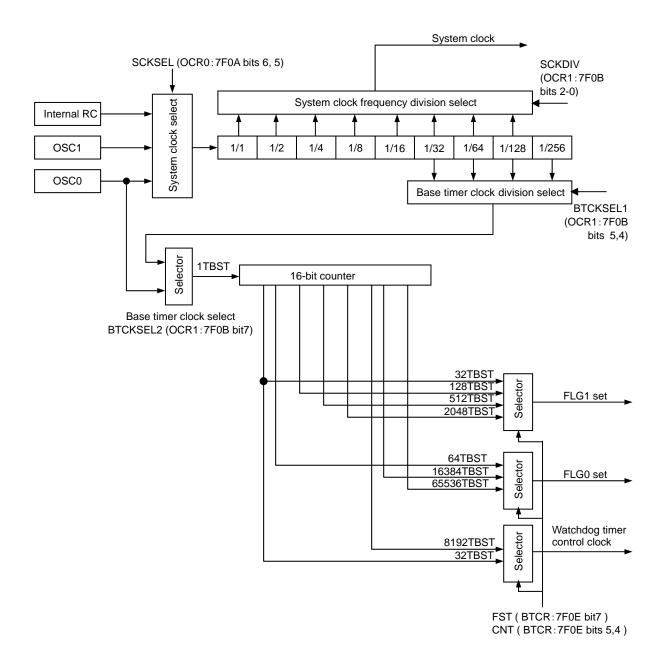

| 3.17 Ba  | se Timer                                                          |

| 3.17.1  | Overview                                                                  |

|---------|---------------------------------------------------------------------------|

| 3.17.2  | Functions                                                                 |

| 3.17.3  | Circuit Configuration                                                     |

| 3.17.4  | Related Registers ······3-95                                              |

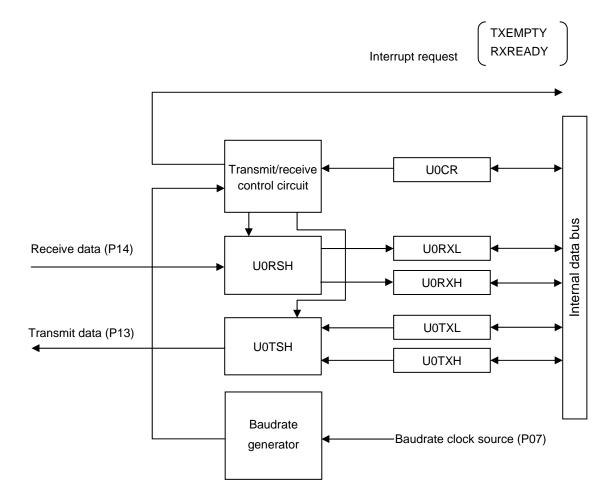

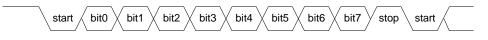

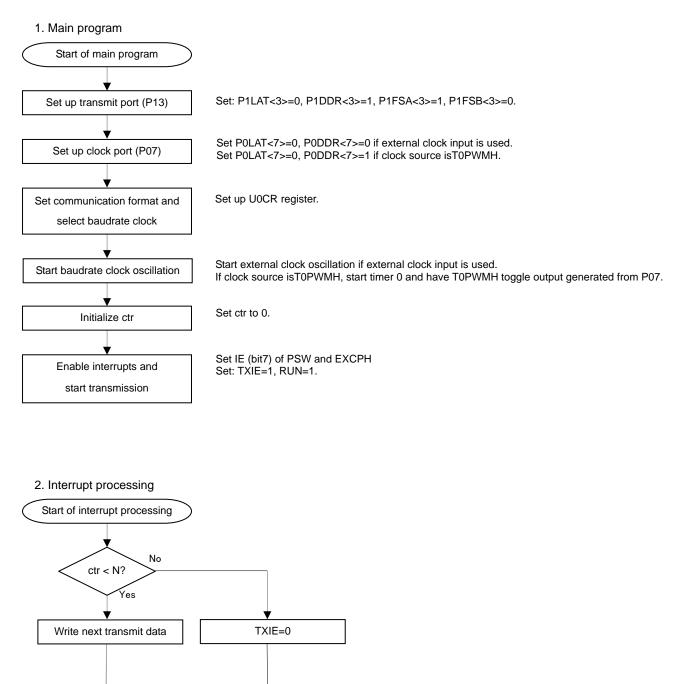

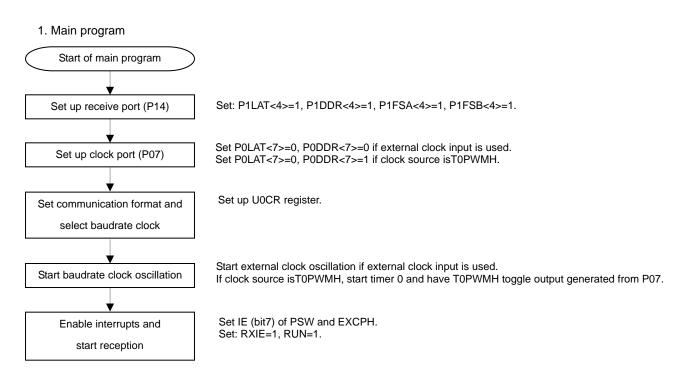

| 3.18 As | ynchronous Serial Interface 0 (UART0)······ 3-96                          |

| 3.18.1  | Overview                                                                  |

| 3.18.2  | Functions                                                                 |

| 3.18.3  | Circuit Configuration                                                     |

| 3.18.4  | Related Registers ······3-99                                              |

| 3.18.5  | UART0 Communication Format Examples 3-101                                 |

| 3.18.6  | UART0 Communication Examples                                              |

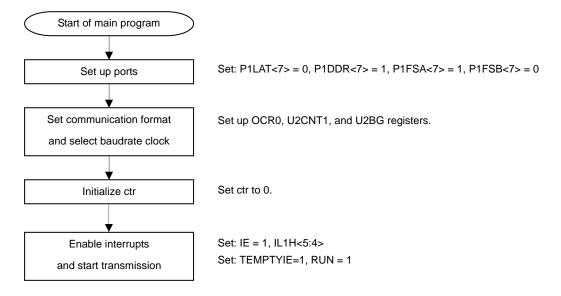

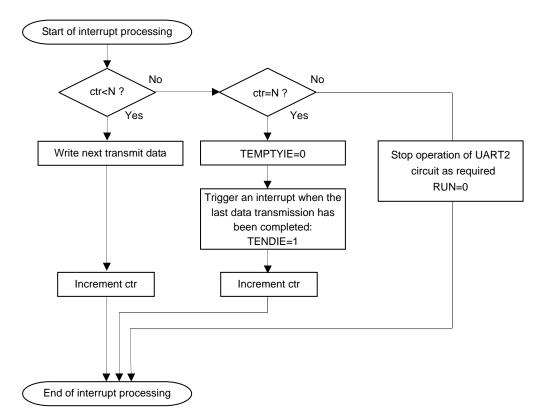

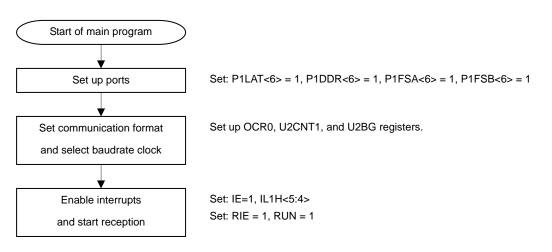

| 3.19 As | ynchronous Serial Interface 2 (UART2)······ 3-105                         |

| 3.19.1  | Overview                                                                  |

| 3.19.2  | Functions 3-105                                                           |

| 3.19.3  | Circuit Configuration                                                     |

| 3.19.4  | Related Registers ······ 3-108                                            |

| 3.19.5  | UART2 Communication Format Examples                                       |

| 3.19.6  | UART2 Communication Examples                                              |

| 3.20 Se | rial Interface 0 (SIO0) ······ 3-114                                      |

| 3.20.1  | Overview                                                                  |

| 3.20.2  | Functions 3-114                                                           |

| 3.20.3  | Circuit Configuration ······ 3-115                                        |

| 3.20.4  | Related Registers 3-118                                                   |

| 3.20.5  | Configuring the Number of Transfer Bits                                   |

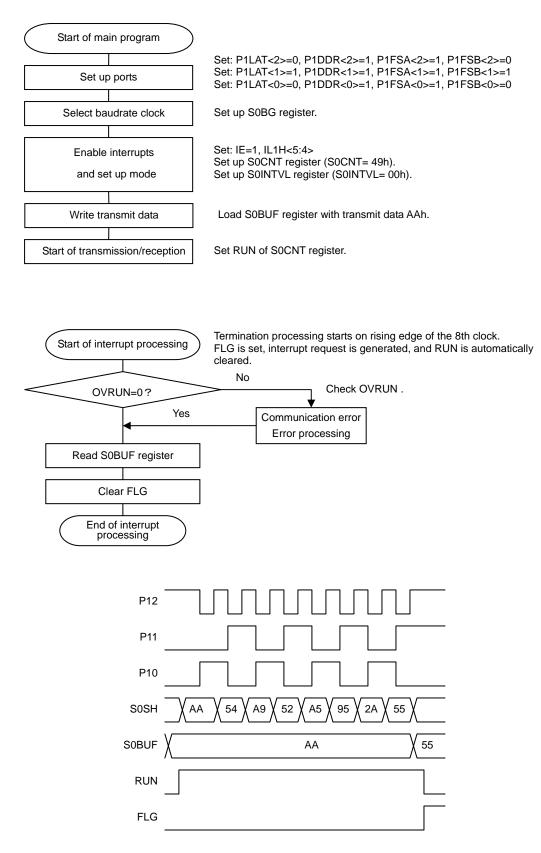

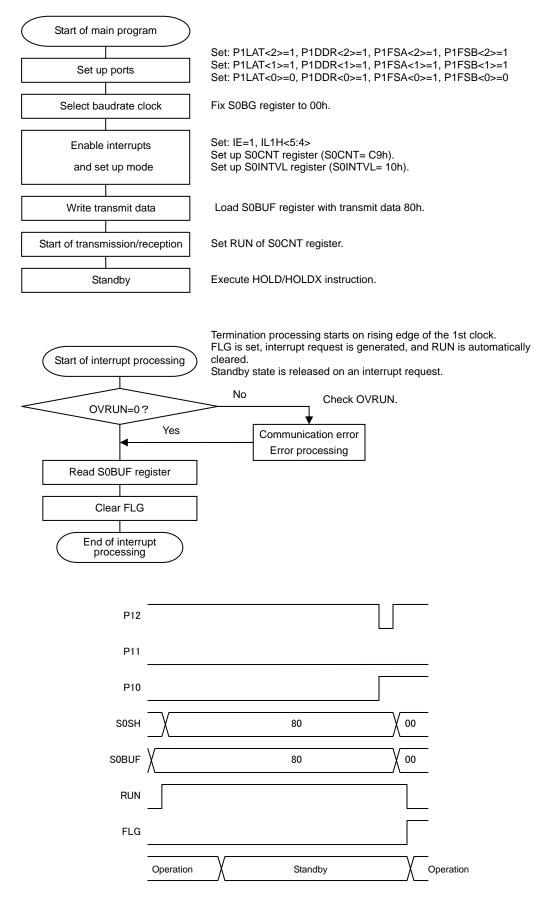

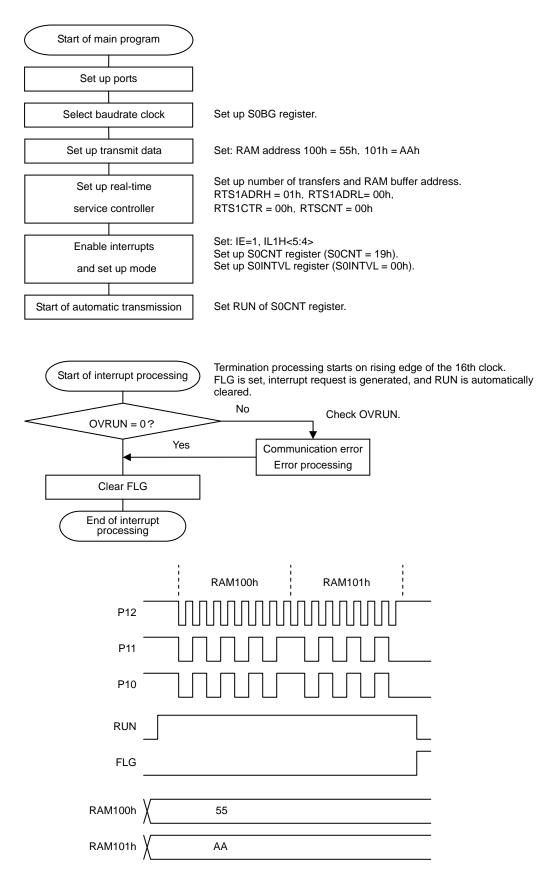

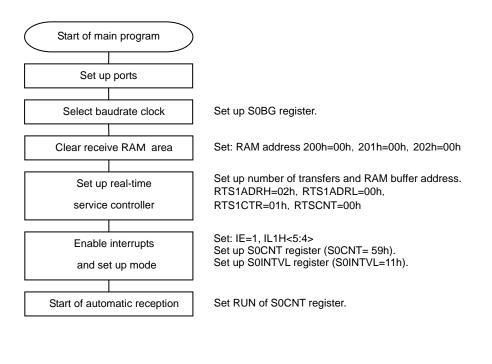

| 3.20.6  | SIO0 Communication Examples                                               |

| 3.21 Se | rial Interface 1 (SIO1) ······ 3-132                                      |

| 3.21.1  | Overview                                                                  |

| 3.21.2  | Functions 3-132                                                           |

| 3.21.3  | Circuit Configuration                                                     |

| 3.21.4  | Related Registers 3-136                                                   |

| 3.21.5  | Configuring the Number of Transfer Bits                                   |

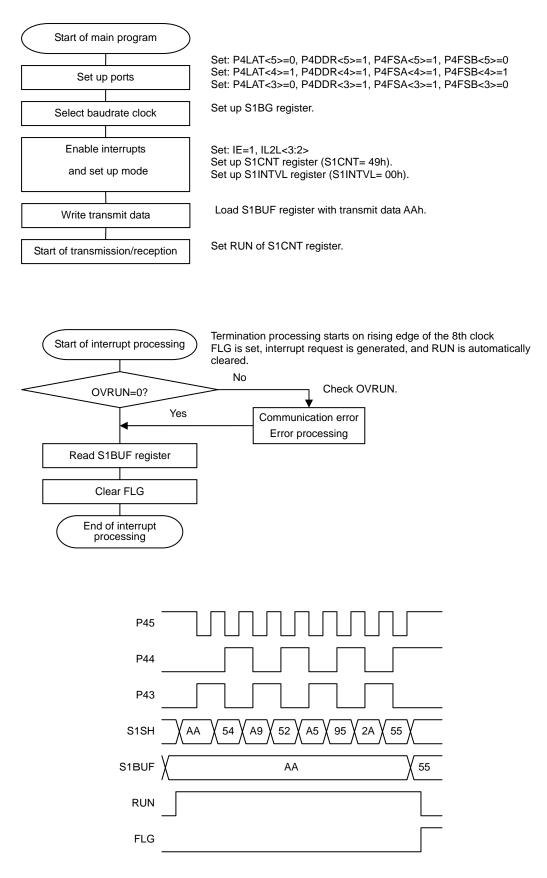

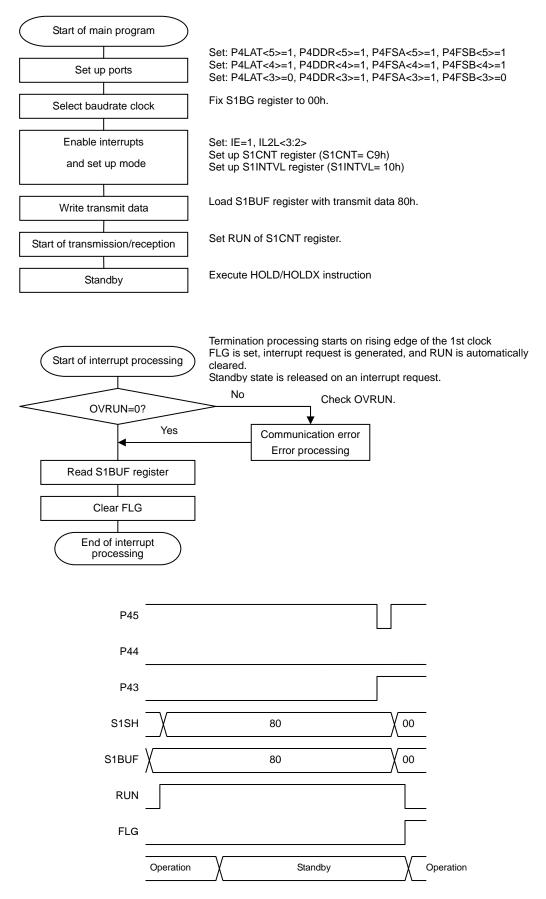

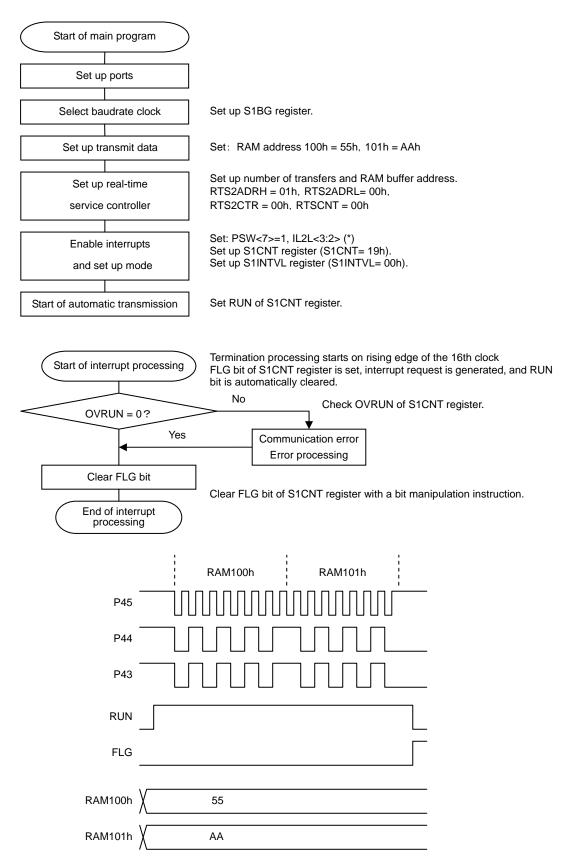

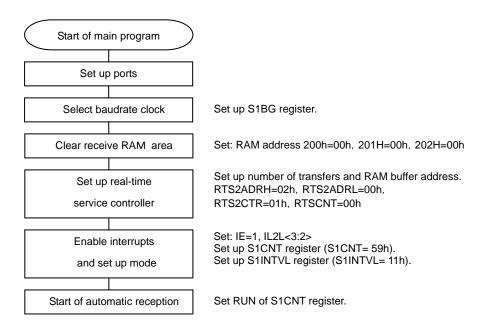

| 3.21.6  | SIO1 Communication Examples                                               |

| 3.22 SM | AIIC0 (Single Master I <sup>2</sup> C)       3-150                        |

| 3.22.1  | Overview                                                                  |

| 3.22.2  | Circuit Configuration 3-150                                               |

| 3.22.3  | Related Registers ······ 3-152                                            |

| 3.22.4  | Notes on the Configuration of the I <sup>2</sup> C Ports for Slow Setting |

| 3.22.5  | Waveform of Generated Clocks and SCL Rise Times                           |

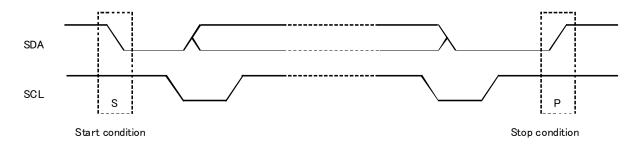

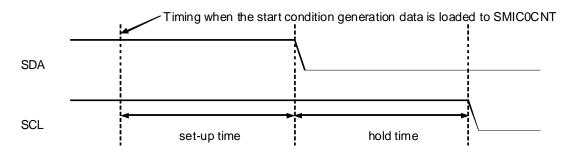

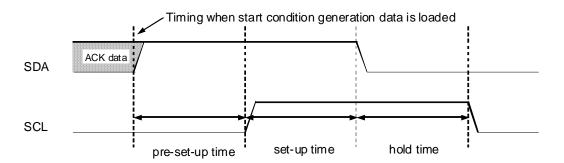

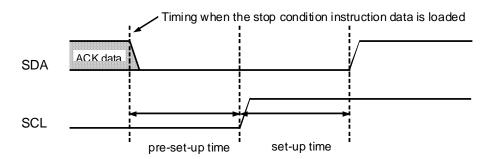

| 3.22.6  | Start Condition and Stop Condition                                        |

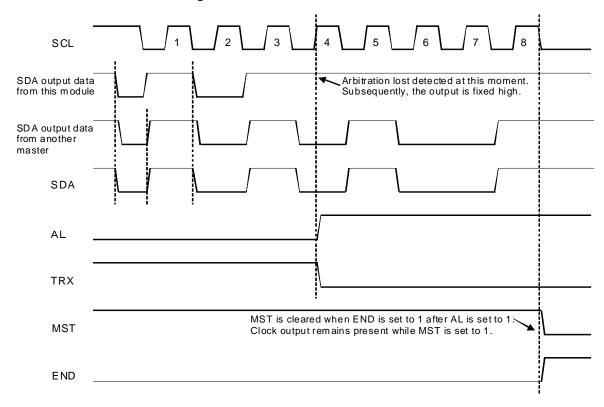

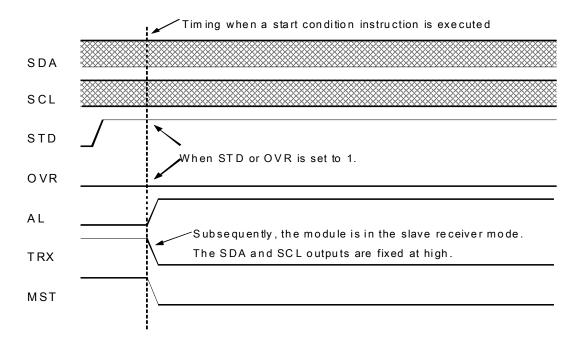

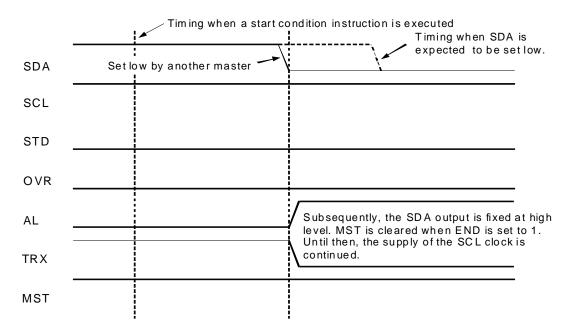

| 3.22.7  | Arbitration Lost                                                          |

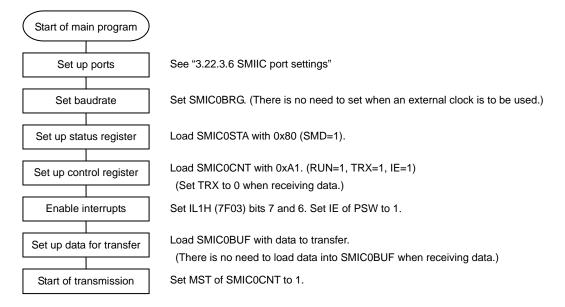

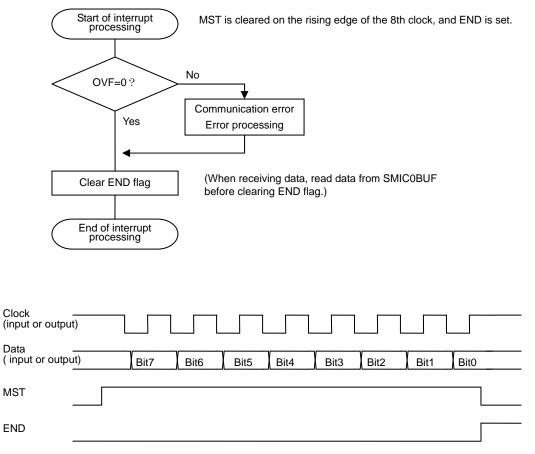

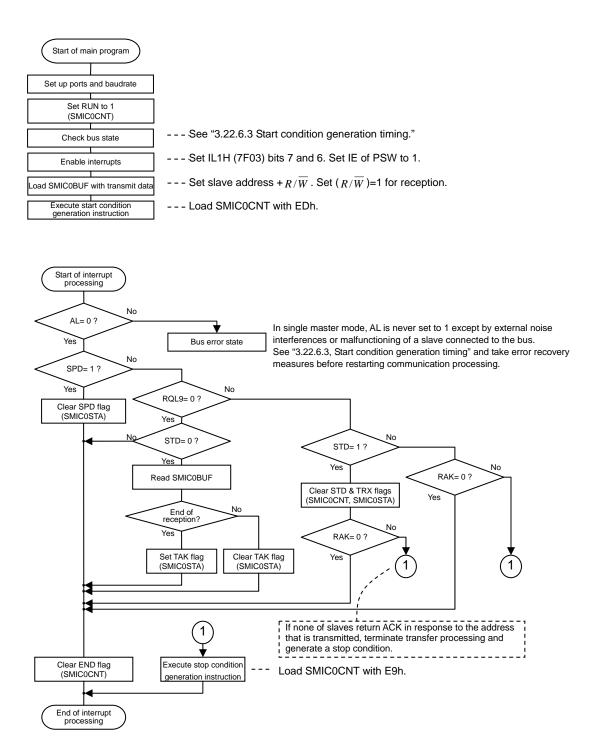

| 3.22.8    | Examples of Simple SIO Mode Communication                |

|-----------|----------------------------------------------------------|

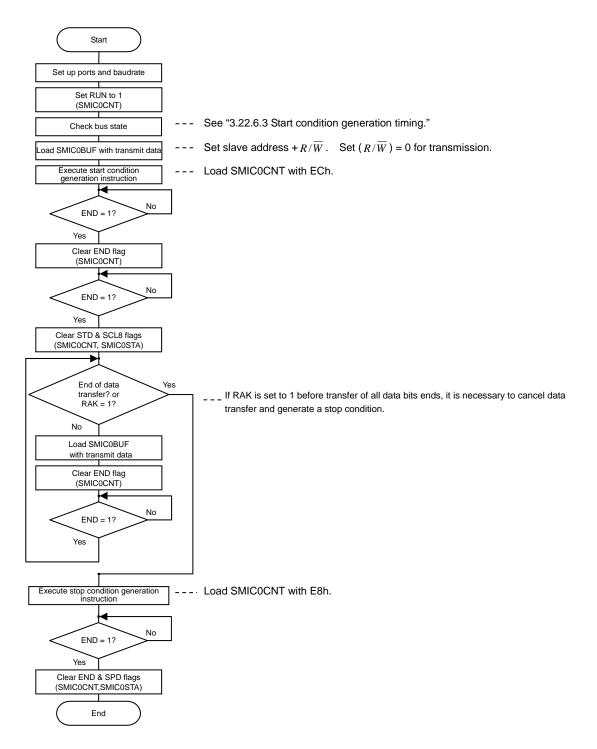

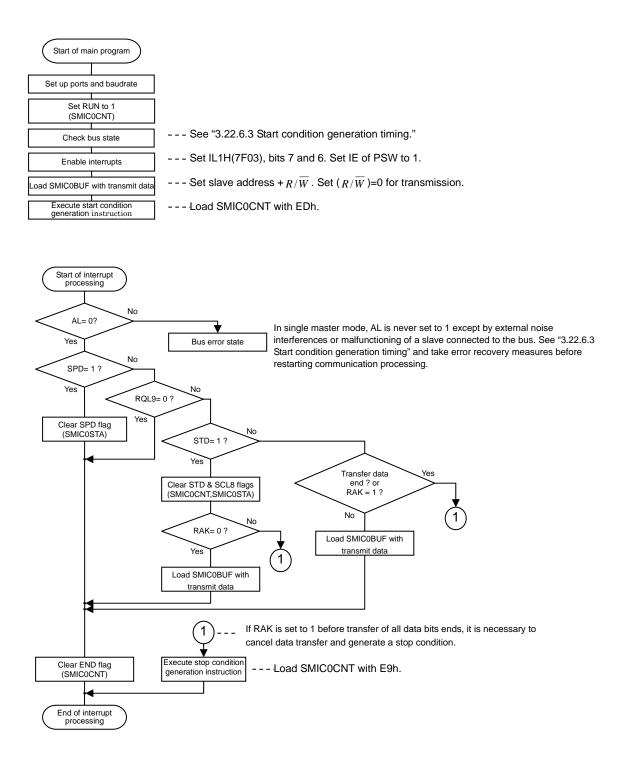

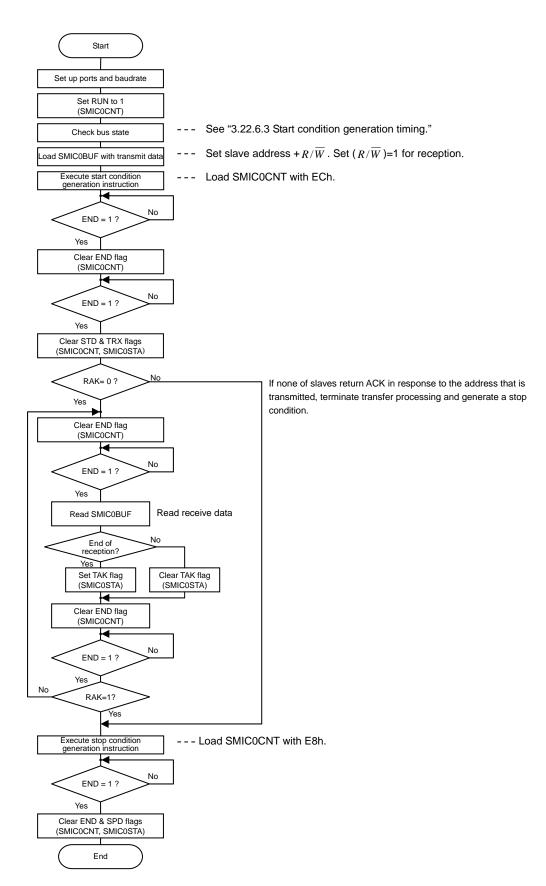

| 3.22.9    | Examples of Single Master I <sup>2</sup> C Communication |

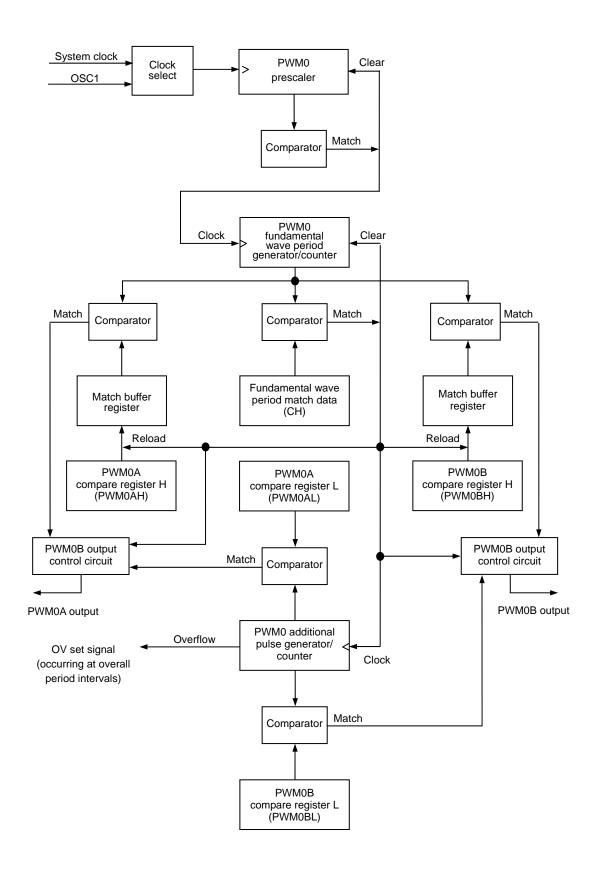

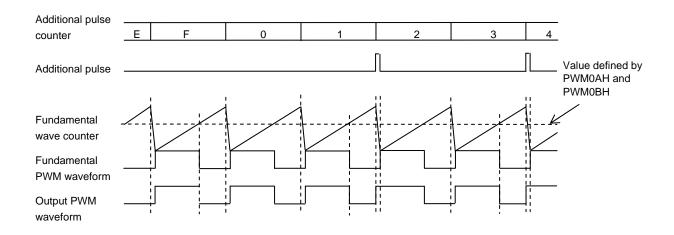

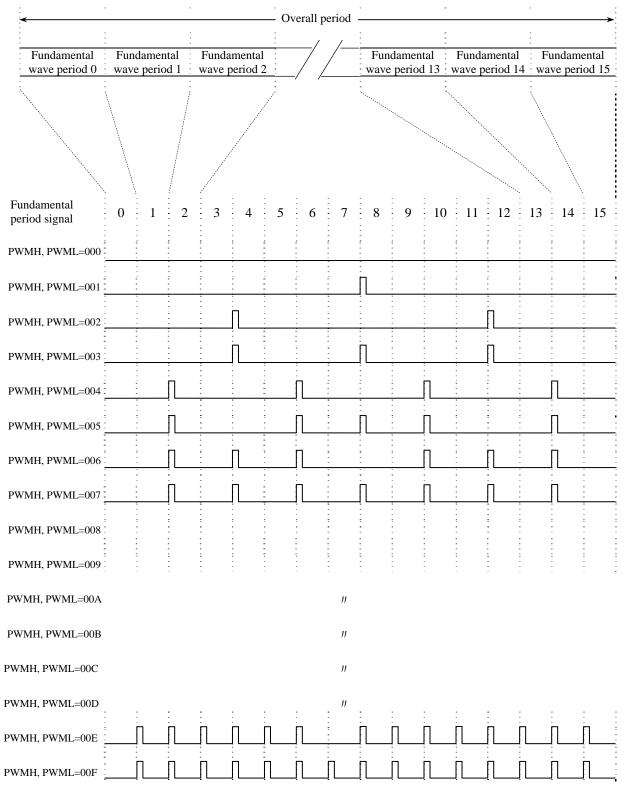

| 3.23 P\   | NM0 3-175                                                |

| 3.23.1    | Overview                                                 |

| 3.23.2    | Functions 3-175                                          |

| 3.23.3    | Circuit Configuration ······ 3-176                       |

| 3.23.4    | Related Registers ······ 3-179                           |

| 3.23.5    | PWM0 Output Port Settings                                |

| 3.24 AI   | D Converter ······ 3-184                                 |

| 3.24.1    | Overview                                                 |

| 3.24.2    | Functions ······ 3-184                                   |

| 3.24.3    | Circuit Configuration                                    |

| 3.24.4    | Related Registers 3-186                                  |

| 3.24.5    | AD Conversion Example 3-189                              |

| 3.24.6    | Hints on the Use of the AD Converter 3-190               |

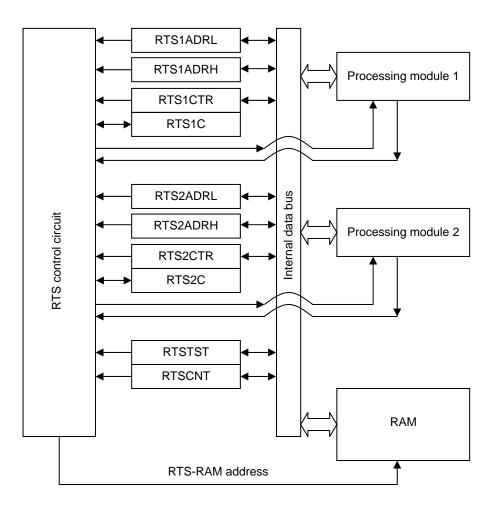

| 3.25 Re   | eal-time Service (RTS) ······ 3-192                      |

| 3.25.1    | Overview                                                 |

| 3.25.2    | Functions ······· 3-192                                  |

| 3.25.3    | Circuit Configuration 3-193                              |

| 3.25.4    | Related Registers ······ 3-195                           |

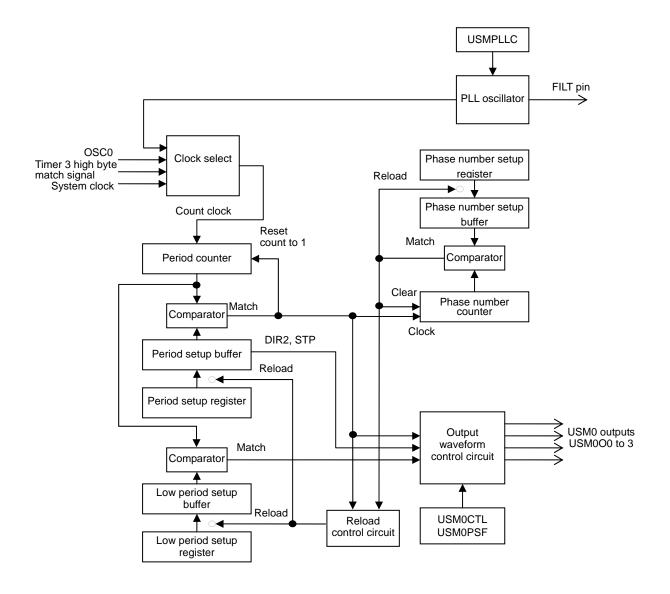

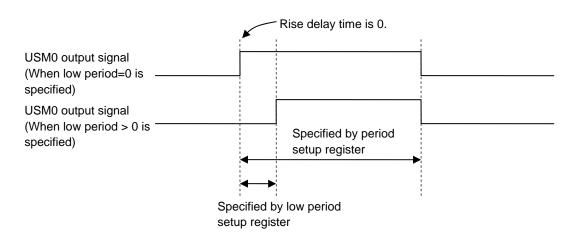

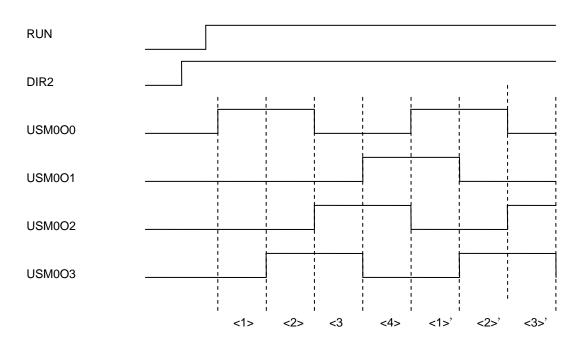

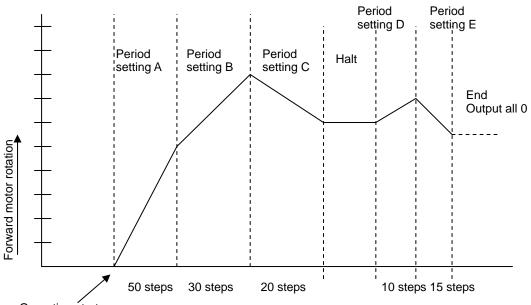

| 3.26 US   | SM0 ····· 3-197                                          |

| 3.26.1    | Overview                                                 |

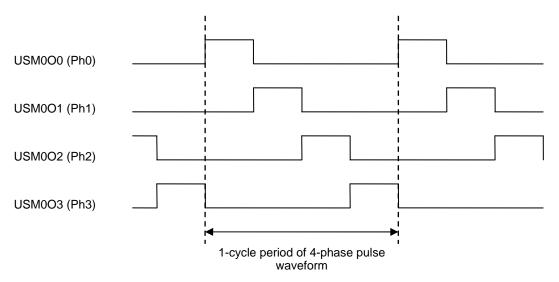

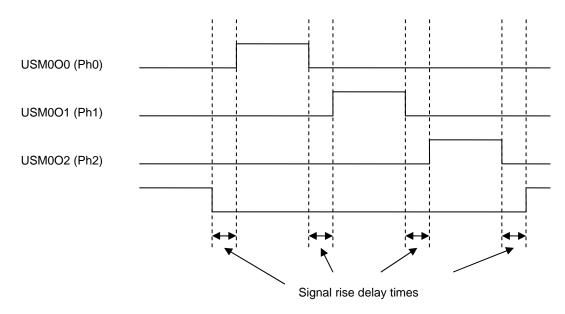

| 3.26.2    | Functions ······· 3-197                                  |

| 3.26.3    | Circuit Configuration 3-198                              |

| 3.26.4    | Related Registers ······ 3-202                           |

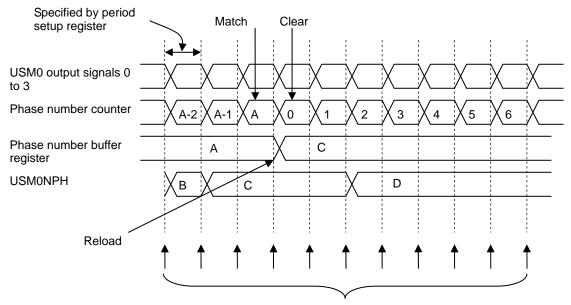

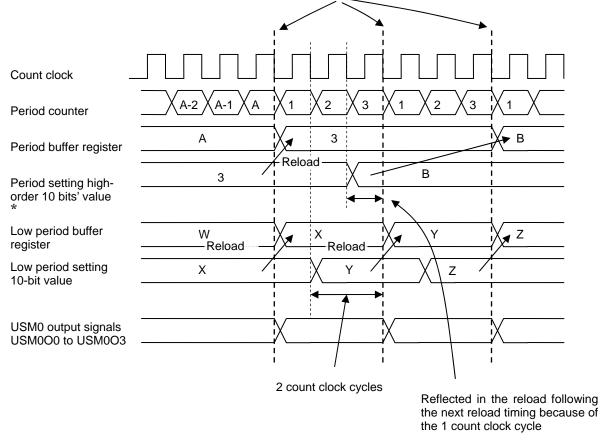

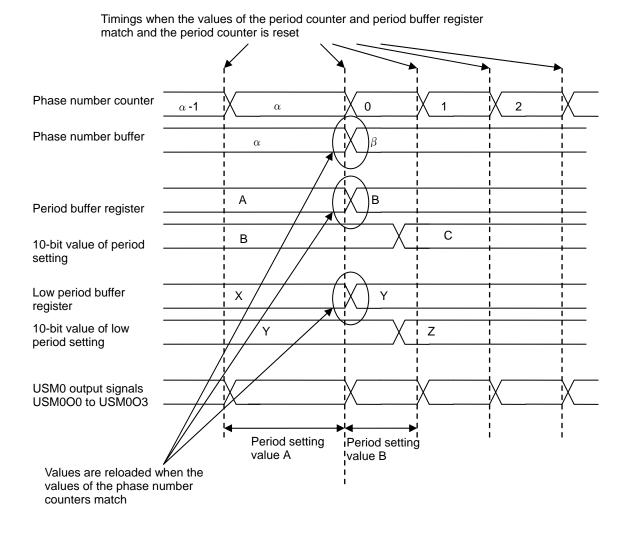

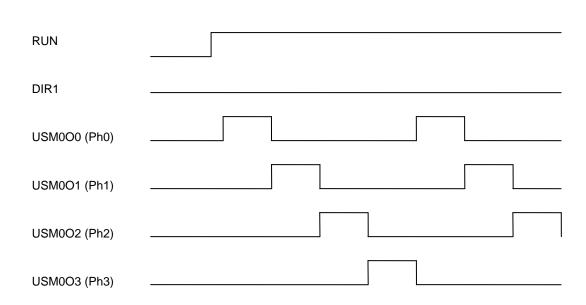

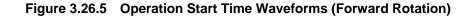

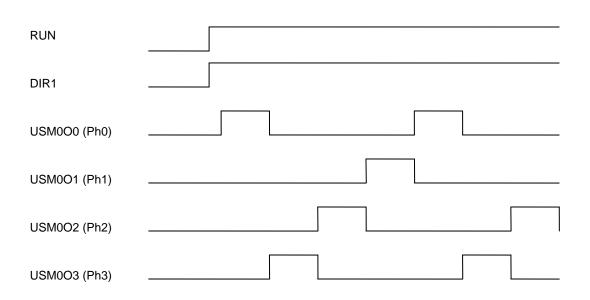

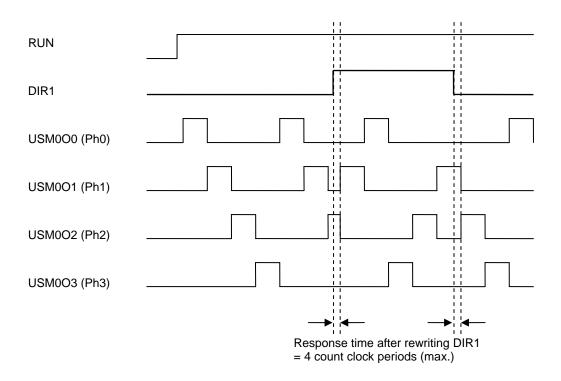

| 3.26.5    | Buffer Register Reload Timings 3-207                     |

| 3.26.6    | USM0 Port Settings 3-210                                 |

| 3.26.7    |                                                          |

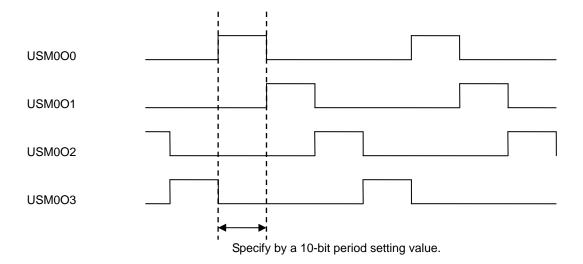

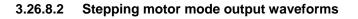

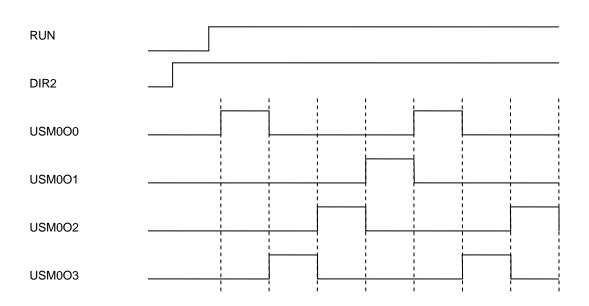

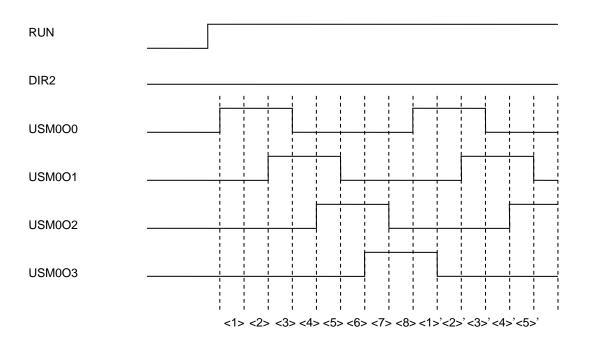

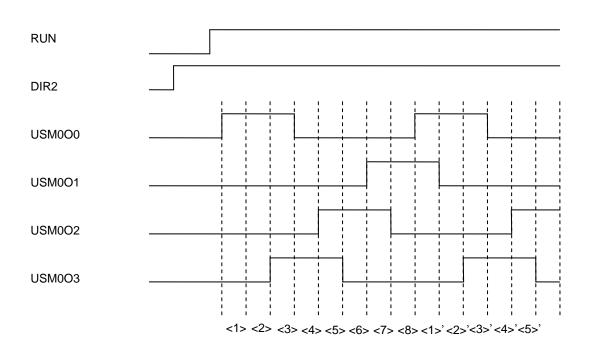

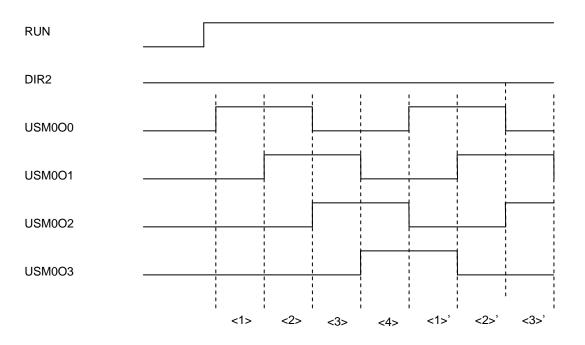

| 3.26.8    | Examples of USM0 Operation in Stepping Motor Mode        |

| 3.26.9    | Notes on Setting Registers 3-221                         |

| Chapter 4 | Control Functions4-1                                     |

| 4.1 Inte  | errupt Function4-1                                       |

| 4.1.1     | Overview 4-1                                             |

| 4.1.2     | Functions 4-1                                            |

| 4.1.3     | Table of Interrupts 4-2                                  |

| 4.1.4     | Related Registers 4-3                                    |

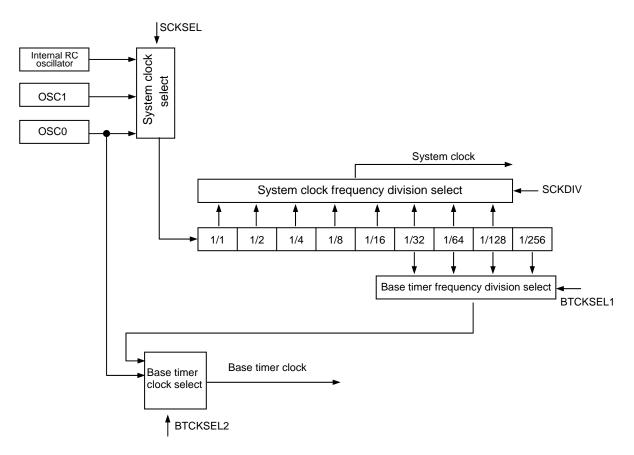

| 4.2 Sys   | stem Clock Generator Function 4-10                       |

| 4.2.1     | Overview4-10                                             |

| 4.2.2     | Functions4-10                                            |

| 4.2.3   | Circuit Configuration4-10          |

|---------|------------------------------------|

|         | Related Registers                  |

|         | 5                                  |

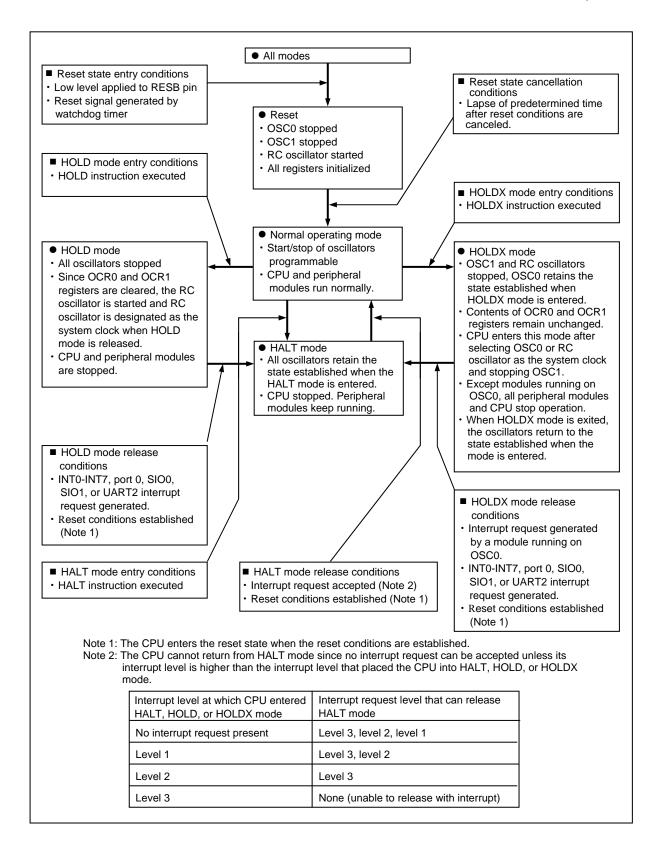

| 4.3 Sta | andby Function ······ 4-14         |

| 4.3.1   | Overview4-14                       |

| 4.3.2   | Functions4-14                      |

| 4.4 Re  | set Function4-20                   |

| 4.4.1   | Overview4-20                       |

| 4.4.2   | Functions4-20                      |

| 4.4.3   | Reset Time State4-20               |

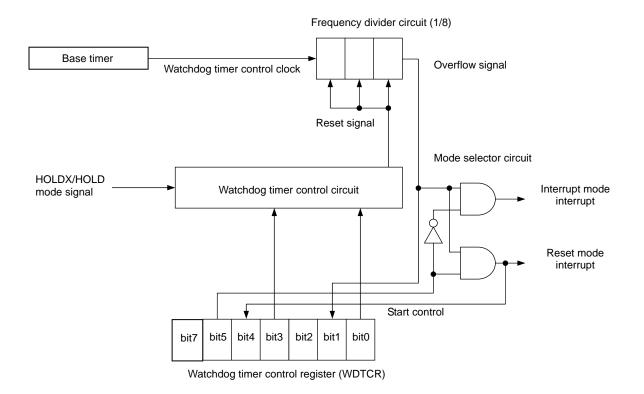

| 4.5 Wa  | atchdog Timer Function ······ 4-21 |

| 4.5.1   | Overview4-21                       |

| 4.5.2   | Functions4-21                      |

| 4.5.3   | Circuit Configuration4-21          |

| 4.5.4   | Related Registers                  |

| 4.5.5   | Using the Watchdog Timer4-24       |

# Chapter 5 Instructions (See separate manual)

# Appendixes

| Appendix-I  | Special Function Register (SFR) Map | · AI (1-9) |

|-------------|-------------------------------------|------------|

| Appendix-II | Port Block Diagrams                 | All (1-6)  |

# 1. Overview

## 1.1 Overview

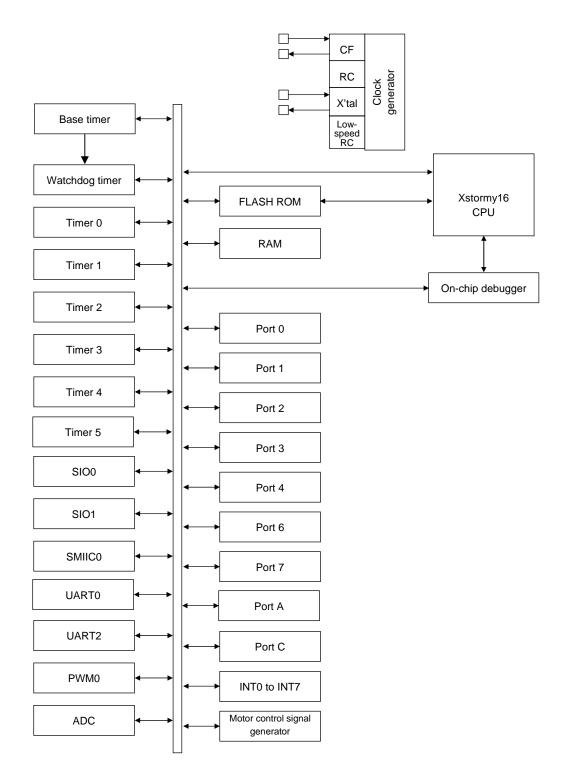

The LC885800 series is a 16-bit microcontroller that, centered around an Xstormy16 CPU, integrates on a single chip a number of hardware features such as 128K-byte flash ROM (onboard programmable), 6K-byte RAM, six 16-bit timers, a base timer serving as a time-of-day clock, two synchronous SIO interfaces (with automatic transfer function), a single master I<sup>2</sup>C/synchronous SIO interface, two asynchronous SIO (UART) interfaces, two multifrequency 12-bit PWM modules, a 12-bit resolution 11-channel AD converter, a watchdog timer, a motor drive signal generator circuit, a system clock frequency divider, a 40-source (24 modules) 16-vector interrupt feature, and on-chip debugging functions.

## 1.2 Features

### • CPU

- Xstormy16 CPU

- 4G bytes of address space

- General-purpose registers: 16 bits × 16

### • ROM

LC88F58B0A: 131072 × 8 bits (flash ROM)

- Block erasable in 128-byte units

- Can be written in 2-byte units

#### • RAM

LC88F58B0A: 6144 × 8 bits

#### • Instruction cycle time (Tcyc)

| Instruction<br>Cycle Time | Frequency<br>Division Ratio | System Clock Source       | Oscillation<br>Frequency |

|---------------------------|-----------------------------|---------------------------|--------------------------|

| 0.083 µs                  | 1/1                         | Ceramic oscillator (OSC1) | 12 MHz                   |

| 0.100 µs                  | 1/1                         | Ceramic oscillator (OSC1) | 10 MHz                   |

| 0.500 µs                  | 1/2                         | Ceramic oscillator (OSC1) | 4 MHz                    |

| 1 μs (typ)                | 1/1                         | Internal RC oscillator    | 1 MHz (typ)              |

| 30.5 µs                   | 1/1                         | Crystal oscillator (OSC0) | 32.768 kHz               |

#### • Ports

- Normal withstand voltage I/O ports Ports whose input/output can be specified in 1-bit units:

- Oscillator, normal withstand voltage output ports:

- Dedicated oscillator ports:

- Reset pin:

- Test pin:

- Power pins:

52 (P0n, P1n, P2n, P30 to P33, P4n, P6n, P70 to P72, PA0 to PA3, PC2)

2 (PC0, PC1)

2 (CF1, CF2)

1 (RESB)

1 (TEST)

6 (VSS1 to VSS3, VDD1 to VDD3)

#### <u>Overview</u>

## Timers

- Timer 0: 16-bit timer that supports PWM/toggle output

- 1) With a 5-bit prescaler

- 2) 8-bit PWM  $\times$  2/8-bit timer + 8-bit PWM mode selectable

- Clock source can be selected from among the system clock, OSC0, OSC1, and internal RC oscillator.

- Timer 1: 16-bit timer with a capture resistor

- 1) With a 5-bit prescaler

- 2) May be divided into 2 channels of 8-bit timer

- Clock source can be selected from among the system clock, OSC0, OSC1, and internal RC oscillator.

- Timer 2: 16-bit timer with a capture resistor

- 1) With a 4-bit prescaler

- 2) May be divided into 2 channels of 8-bit timer

- 3) Clock source can be selected from among the system clock, OSC0, OSC1, and external events.

- Timer 3: 16-bit timer that supports PWM/toggle output

- 1) With an 8-bit prescaler

- 2) 8-bit timer  $\times$  2/8-bit timer + 8-bit PWM mode selectable

- 3) Clock source can be selected from among the system clock, OSC0, OSC1, and external events.

- Timer 4: 16-bit timer that supports toggle output

- 1) Clock source can be selected from the system clock and prescaler 0.

- Timer 5: 16-bit timer that supports toggle output

- 1) Clock source can be selected from the system clock and prescaler 0.

- \* Prescaler 0 is a 4-bit configuration, and the clock source can be selected from among the system clock, OSC0, and OSC1.

- Base timer

- 1) Clock can be selected from OSC0 (32.768 kHz crystal oscillator) and frequency-divided output of the system clock.

- 2) An interrupt can be generated in 7 time schemes.

## Serial interfaces

- SIO0, SIO1: 8-bit synchronous SIO

- 1) LSB first/MSB first selectable

- 2) Supports less than 8-bit communication (1- to 8-bit data length can be specified)

- 3) Built-in 8-bit baudrate generator (4 to 512 Tcyc transfer clock)

- 4) Automatic continuous data transfer function (9 to 32768bits can be specified in 1-bit units)

- 5) Interval function (interval times of 0 to 64 tSCK)

- 6) Wakeup function

- SMIIC0: Single master I<sup>2</sup>C/8-bit synchronous SIO

- Mode 0: Single-master mode communication

- Mode 1: Synchronous 8-bit serial I/O (MSB first)

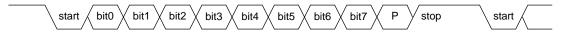

- UART0: Asynchronous SIO

- 1) Data length: 8 bits (LSB first)

- 2) Stop bits: 1 bit

- 3) Parity bits: None/even parity/odd parity

- 4) Transfer rate: 4/8 Tcyc

- 5) Baudrate source clock: P07 input signal (T0PWMH signal available as clock source)

- 6) Full duplex communication

- UART2: Asynchronous SIO

- 1) Data length: 8 bits (LSB first)

- 2) Stop bits: 1 bit

- 3) Parity bits: None/even parity/odd parity

- 4) Transfer rate: 8 to 4096 Tcyc

- 5) Baudrate source clock: System clock/OSC0/OSC1

- 6) Wakeup function

- 7) Full duplex communication

### • AD converter

- 1) 12-/ 8-bit converter resolution selectable

- 2) Analog inputs: 11 channels

- 3) Comparator mode

- 4) Automatic reference voltage generation

### • PWM

- PWM0: Multifrequency 12-bit PWM × 2 channels (PWM0A and PWM0B)

- 1) 2-channel pairs controlled independently of one another

- 2) Clock source can be selected from the system clock and OSC1

- 3) Built-in 8-bit prescaler: TPWMR0 = (Prescaler value + 1) × clock frequency

- 4) 8-bit fundamental wave PWM generator circuit + 4-bit additional pulse generator circuit

| 5) | Fundamental wave PWM mode        |                                         |  |

|----|----------------------------------|-----------------------------------------|--|

|    | Fundamental wave period:         | 16TPWMR0 to 256TPWMR0                   |  |

|    | High-level pulse width:          | 0 to (Fundamental wave period – TPWMR0) |  |

| 6) | Fundamental wave + additionation | al pulse mode                           |  |

|    | Fundamental wave period:         | 16TPWMR0 to 256TPWMR0                   |  |

|    | Overall period:                  | Fundamental wave period × 16            |  |

## Watchdog timer

- Driven by the base timer + internal watchdog-timer dedicated counter

- Interrupt or reset mode selectable

#### • Motor drive signal generator circuit

#### • Interrupts (peripheral function)

• 40 sources (24 module), 16 vector addresses

High-level pulse width:

1) Provides three levels of multiplex interrupt control. Any interrupt request of the level equal to or lower than the current interrupt is not accepted.

0 to (Overall period – PWMR0)

2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest level takes precedence over the other interrupts. For interrupts of the same level, the interrupt with the lowest vector address has priority.

| No. | Vector Address | Interrupt (Peripheral Function)     |

|-----|----------------|-------------------------------------|

| 1   | 08000H         | Watchdog timer (1)                  |

| 2   | 08004H         | Base timer (2)                      |

| 3   | 08008H         | Timer 0 (2)                         |

| 4   | 0800CH         | INT0 (1)                            |

| 5   | 08010H         |                                     |

| 6   | 08014H         | INT1 (1)                            |

| 7   | 08018H         | INT2 (1) / timer 1 (2) / UART2 (4)  |

| 8   | 0801CH         | INT3 (1) / timer 2 (4) / SMIIC0 (1) |

| 9   | 08020H         | INT4 (1) / timer 3 (2)              |

| 10  | 08024H         | INT5 (1) / timer 4 (1) / SIO1 (2)   |

| 11  | 08028H         | USM0 (3)                            |

| 12  | 0802CH         | PWM0 (1)                            |

| 13  | 08030H         | ADC (1) / timer 5 (1)               |

| 14  | 08034H         | INT6 (1)                            |

| 15  | 08038H         | INT7 (1) / SIO0 (2)                 |

| 16  | 0803CH         | Port 0 (3)                          |

• Three priority levels can be specified.

- When interrupts of the same level occur at the same time, the interrupt with the lowest vector address is processed first.

- The number enclosed in parentheses denotes the number of sources.

#### Interrupts (exception processing)

- 5 sources, 1 vector address

- 1) Interrupts of this type are enabled or disabled through the exception interrupt control register (EXCPL and EXCPH) and not affected by the global enable flag.

- 2) Exception processing interrupts take precedence over interrupts that are generated by any of the peripheral functions. Consequently, no interrupt request is accepted while an exception interrupt is being processed.

| No. | Vector Address | Interrupt (Exception Processing) |

|-----|----------------|----------------------------------|

| 1   | 08080H         | Exception processing (5)         |

• The number enclosed in parentheses indicates the number of interrupt sources.

#### • Subroutine stack: 6K-byte RAM area

- Subroutine calls that automatically save PSW, interrupt vector calls: 6 bytes

- Subroutine calls that do not automatically save PSW: 4 bytes

#### • Multiplication/division instructions

- 16 bits × 16 bits (Execution time: 18 Tcyc)

- 16 bits ÷ 16 bits (Execution time: 18 to 19 Tcyc)

- 32 bits ÷ 16 bits (Execution time: 18 to 19 Tcyc)

#### Oscillator circuits

- RC oscillator circuit (internal): For system clock

- OSC1 (CF oscillator circuit): For system clock (CF1, CF2)

- OSC0 (crystal oscillator circuit): For low-speed system clock (XT1, XT2)

- Low-speed RC oscillator circuit (internal): For system clock used when the main oscillation is stopped

- PLL circuit (internal): For motor drive signal generator circuit

#### • System clock frequency divider function

- Can run on low current.

- System clock frequency can be set to 1/1 to 1/128 of base system frequency.

### • Standby function

- HALT mode: Halts instruction execution while allowing the peripheral circuits to continue operation.

- 1) Oscillation is not halted automatically.

- 2) Released by a system reset or occurrence of an interrupt.

- HOLD mode: Suspends instruction execution and the operation of the peripheral circuits.

- 1) OSC1, internal RC, and OSC0 oscillators automatically stop.

- 2) There are five ways of releasing HOLD mode.

- <1> Setting the reset pin to a low level

- <2> Setting at least one of the INT0, INT1, INT2, INT3, INT4, INT5, INT6, and INT7 pins to the specified level

- <3> Establishing an interrupt source at P0INT, P04INT, or P05INT

- <4> Establishing an interrupt source at SIO0 or SIO1

- <5> Establishing an interrupt source at UART2

- HOLDX mode: Suspends instruction execution and the operation of the peripheral circuits except those which run on OSC0.

- 1) OSC1 and internal RC oscillators automatically stop operation.

- 2) OSC0 retains the state that is established when HOLDX mode is entered.

- 3) There are six ways of releasing HOLDX mode.

- <1> Setting the reset pin to a low level

- <2> Setting at least one of the INT0, INT1, INT2, INT3, INT4, INT5, INT6, and INT7 pins to the specified level

- <3> Establishing an interrupt source at POINT, PO4INT, or PO5INT

- <4> Establishing an interrupt source at SIO0 or SIO1

- <5> Establishing an interrupt source at UART2

- <6> Establishing an interrupt source in the base timer circuit

### Package form

• SQFP64  $(10 \times 10)$  Lead-free type

### • On-chip debugger function

- Supports software debugging with the IC mounted on the target board.

- Supports source line debugging, tracing, and breakpoint setting.

- Single-wire communication

#### • Development tools

• On-chip debugger: EOCUIF1 + LC88F58B0A

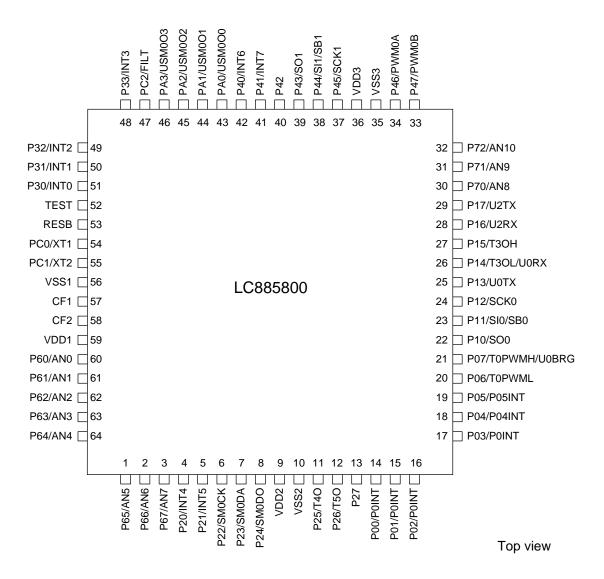

## 1.3 Pinout

SQFP64 (10 × 10) (lead-free product)

# 1.4 System Block Diagram

# 1.5 Pin Functions

|            | I/O | Description                                                                   |  |  |

|------------|-----|-------------------------------------------------------------------------------|--|--|

| VSS1,VSS2, | -   | – power supply pin                                                            |  |  |

| VSS3       |     |                                                                               |  |  |

| VDD1,VDD2  | -   | + power supply pin                                                            |  |  |

| VDD3       |     |                                                                               |  |  |

| Port 0     | I/O | • 8-bit I/O port                                                              |  |  |

| P00 to P07 |     | • I/O specifiable in 1-bit units                                              |  |  |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units                   |  |  |

|            |     | • Port 0 interrupt input (P00 to P03, P04, P05)                               |  |  |

|            |     | • HOLD release input (P00 to P03, P04, P05)                                   |  |  |

|            |     | • Pin functions                                                               |  |  |

|            |     | P06 : Timer 0L output                                                         |  |  |

|            |     | P07 : Timer 0H output / UART0 clock input                                     |  |  |

| Port 1     | I/O | • 8-bit I/O port                                                              |  |  |

| P10 to P17 |     | • I/O specifiable in 1-bit units                                              |  |  |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units                   |  |  |

|            |     | • Pin functions                                                               |  |  |

|            |     | P10: SIO0 data output                                                         |  |  |

|            |     | P11: SIO0 data input / bus I/O                                                |  |  |

|            |     | P12: SIO0 clock I/O                                                           |  |  |

|            |     | P13: UART0 transmit                                                           |  |  |

|            |     | P14: Timer 3L output / UART0 receive                                          |  |  |

|            |     | P15: Timer 3H output                                                          |  |  |

|            |     | P16: UART2 receive                                                            |  |  |

|            |     | P17: UART2 transmit                                                           |  |  |

| Port 2     | I/O | • 8-bit I/O port                                                              |  |  |

| P20 to P27 |     | • I/O specifiable in 1-bit units                                              |  |  |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units                   |  |  |

|            |     | • Pin functions                                                               |  |  |

|            |     | P20: INT4 input / HOLD release input/timer 3 event input / timer 2L capture   |  |  |

|            |     | input / timer 2H capture input                                                |  |  |

|            |     | P21: INT5 input / HOLD release input /timer 3 event input / timer 2L capture  |  |  |

|            |     | input / timer 2H capture input                                                |  |  |

|            |     | P22: SMIIC clock I/O                                                          |  |  |

|            |     | P23: SMIIC data bus I/O                                                       |  |  |

|            |     | P24: SMIIC data (used in 3-wire SIO mode)                                     |  |  |

|            |     | P25: Timer 4 output                                                           |  |  |

|            |     | P26: Timer 5 output                                                           |  |  |

|            |     | • Interrupt acknowledge type                                                  |  |  |

|            |     | INT4, INT5: H level, L level, H edge, L edge, both edges                      |  |  |

| Port 3     | I/O | • 4-bit I/O port                                                              |  |  |

| P30 to P33 |     | • I/O specifiable in 1-bit units                                              |  |  |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units                   |  |  |

|            |     | • Pin functions                                                               |  |  |

|            |     | P30 : INT0 input / HOLD release input /timer 2L capture input                 |  |  |

|            |     | P31 : INT1 input / HOLD release input /timer 2H capture input                 |  |  |

|            |     | P32 : INT2 input / HOLD release input /timer 2 event input / timer 2L capture |  |  |

|            |     | input                                                                         |  |  |

|            |     | P33 : INT3 input / HOLD release input /timer 2 event input / timer 2H capture |  |  |

|            |     | input                                                                         |  |  |

|            |     | • Interrupt acknowledge type                                                  |  |  |

|            |     | INT0 to INT3: H level, L level, H edge, L edge, both edges                    |  |  |

|            |     |                                                                               |  |  |

|            | I/O | Description                                                 |

|------------|-----|-------------------------------------------------------------|

| Port 4     | I/O | • 8-bit I/O port                                            |

| P40 to P47 |     | • I/O specifiable in 1-bit units                            |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units |

|            |     | • Pin functions                                             |

|            |     | P40 : INT6 input/HOLD release input                         |

|            |     | P41 : INT7 input/HOLD release input                         |

|            |     | P43 : SIO1 data output                                      |

|            |     | P44 : SIO1 data input/bus I/O                               |

|            |     | P45 : SIO1 clock I/O                                        |

|            |     | P46 : PWM0A output                                          |

|            |     | P47 : PWM0B output                                          |

|            |     | • Interrupt acknowledge type                                |

|            |     | INT6, INT7: H level, L level, H edge, L edge, both edges    |

| Port 6     | I/O | • 8-bit I/O port                                            |

| P60 to P67 |     | • I/O specifiable in 1-bit units                            |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units |

|            |     | • Pin functions                                             |

|            |     | AN0 (P70) to AN7 (P61): AD converter input port             |

| Port 7     | I/O | • 3-bit I/O port                                            |

| P70 to P72 |     | • I/O specifiable in 1-bit units                            |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units |

|            |     | • Pin functions                                             |

|            |     | AN8 (P70) to AN10 (P72): AD converter input port            |

| Port A     | I/O | • 4-bit I/O port                                            |

| PA0 to PA3 |     | • I/O specifiable in 1-bit units                            |

|            |     | • Pull-up resistors can be turned on and off in 1-bit units |

|            |     | Multiplexed pin functions                                   |

|            |     | PA0 : USM0 output 0                                         |

|            |     | PA1 : USM0 output 1                                         |

|            |     | PA2 : USM0 output 2                                         |

|            |     | PA3 : USM0 output 3                                         |

| Port C     | I/O | • 3-bit I/O port                                            |

| PC0 to PC2 |     | • Output specifiable in 1-bit units                         |

|            |     | • Pin functions                                             |

|            |     | PC0 : 32.768kHz crystal resonator input                     |

|            |     | PC1 : 32.768kHz crystal resonator output                    |

|            |     | PC2 : Connected to PLL filter circuit                       |

| RESB       | I/O | • Reset pin                                                 |

| TEST       | I/O | • TEST pin                                                  |

|            | 1/0 | Used to communicate with on-chip debugger                   |

| CF1        | Ι   | Ceramic resonator input                                     |

| CF2        | 0   | Ceramic resonator output                                    |

# 1.6 Port Output Types

The table below lists the types of port outputs and the presence/absence of a pull-up resistor. Data can be read into any input port even if it is in the output mode.

| Port                     | Options Selected<br>in Units of | Option<br>Type | Output Type                          | Pull-up Resistor |

|--------------------------|---------------------------------|----------------|--------------------------------------|------------------|

| P00 to P07<br>P10 to P17 | 1 bit<br>(programmable)         | 1              | CMOS                                 | Programmable     |

| P10 to P17<br>P20 to P27 | (programmable)                  |                |                                      |                  |

| P30 to P33               |                                 | 2              | N-channel open drain                 |                  |

| P40 to P47               |                                 |                |                                      |                  |

| P60 to P67               |                                 |                |                                      |                  |

| P70 to P72               |                                 |                |                                      |                  |

| PA0 to PA3               |                                 |                |                                      |                  |

| PC0                      | _                               | _              | N-channel open drain                 | None             |

|                          |                                 |                | (32.768kHz crystal resonator input)  |                  |

| PC1                      | _                               | -              | N-channel open drain                 | None             |

|                          |                                 |                | (32.768kHz crystal resonator output) |                  |

| PC2                      | _                               | _              | CMOS                                 | Programmable     |

# 2. Internal System Configuration

## 2.1 Memory Space

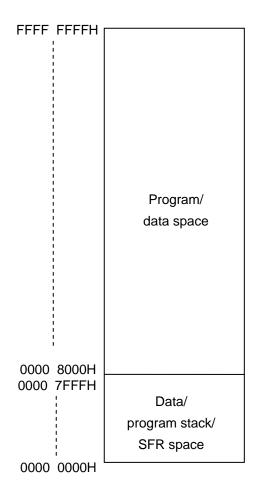

Xstormy 16 can control 4G bytes of linear address memory. 32K bytes from 0000\_0000H to 0000\_7FFFH of the 4G-byte memory address space can be controlled with instructions and are used for CPU operations and to provide peripheral functions.

Approximately 4G bytes of memory from 0000\_8000H to FFFF\_FFFFH are used to store programs and data and subjected to control by the program counter (PC). They can also be controlled with instructions as data storage area in the same manner as the memory space from 0000\_0000h to 0000\_7FFFh.

Figure 2.1.1 Xstormy 16 Memory Space

### 2.1.1 Program/Data Space

The program/data space has a size of approximately 4G bytes and extends from addresses 0000\_8000H to FFFF\_FFFH. The size of the memory that is actually incorporated in the microcontroller varies with the type of the microcontroller. 256 bytes out of the program/data space are used to define options. This area cannot be used as a program area.

## 2.1.2 Data/Program Stack/SFR Space

The data/program stack/SFR space has a size of 32K bytes and extends from 0000\_0000H to 0000\_7FFFH. The size of the RAM (data/program stack) and SFR that is actually incorporated in the microcontroller varies with the type of the microcontroller.

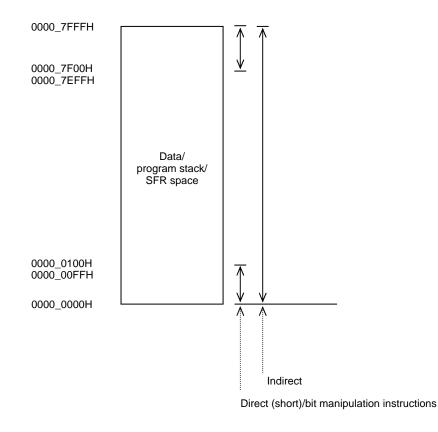

As shown in Figure 2.1.2, the instructions that can be used differ according to the address range of the data/program stack/SFR space.

#### Figure 2.1.2 Data/Program Stack/SFR Space Address Map

When the PC value is stored in RAM during the execution of a subroutine which automatically saves the PSW value or on an interrupt, the low-order 16 bits of the PC are stored in SP in RAM (assuming that SP represents the current stack pointer value) and the high-order 16 bits in SP + 2, and the PSW value in SP + 4, resulting in SP = SP + 6. If a call is made to a subroutine which does not automatically save the PSW value, the low-order 16 bits of the PC are stored in SP in RAM and the high-order 16 bits in SP + 2, resulting in SP = SP + 4.

## 2.2 Program Counter (PC)

The program counter (PC) is 32 bits long and allows linear access to up to approximately 4G bytes of memory space from 0000\_8000h to FFFF\_FFFh.

Since all CPU instructions are 2 bytes in length, their least significant bit is invalid and assumed to be 0.

When executing a branch or subroutine instruction, when accepting an interrupt, or when a reset is generated, the value corresponding to each operation is loaded into the PC.

Table 2.2.1 lists the values that are loaded into the PC when the respective operations are performed.

|           |                 | Operation                         | PC Value                                      |

|-----------|-----------------|-----------------------------------|-----------------------------------------------|

|           | Reset/Watchd    | og timer                          | 0000_8000H                                    |

|           | Base timer      |                                   | 0000_8004H                                    |

|           | Timer 0         |                                   | 0000_8008H                                    |

|           | INT0            |                                   | 0000_800CH                                    |

|           |                 |                                   | 0000_8010H                                    |

|           | INT1            |                                   | 0000_8014H                                    |

|           | INT2 / Timer    | 1 / UART2                         | 0000_8018H                                    |

| ıpt       | INT3 / Timer    | 2 / SMIICO                        | 0000_801CH                                    |

| Interrupt | INT4 / Timer    | 3                                 | 0000_8020H                                    |

| Into      | INT5 / Timer    | 4 / SIO1                          | 0000_8024H                                    |

|           | USM0            |                                   | 0000_8028H                                    |

|           | PWM0            |                                   | 0000_802CH                                    |

|           | ADC / Timer     | 5                                 | 0000_8030H                                    |

|           | INT6            |                                   | 0000_8034H                                    |

|           | INT7 / SIO0     |                                   | 0000_8038H                                    |

|           | Port0           |                                   | 0000_803CH                                    |

|           | Exception pro   | cessing                           | 0000_8080H                                    |

| Unc       | conditional     | JMPF a24                          | PC = a24                                      |

| bra       | nch instruction | JMP Rb, Rs                        | PC = Rb << 16 + Rs                            |

|           |                 | ,<br>,                            | Rb: Contents of base register                 |

|           |                 |                                   | Rs: Contents of general-purpose register      |

|           |                 | BR r12                            | PC = PC + 2 + r12[-2048  to  + 2047]          |

|           |                 | BR Rs                             | PC = PC + 2 + Rs[-32768  to  + 32768]         |

|           |                 |                                   | Rs: Contents of general-purpose register      |

| Cor       | nditional       | BGE, BNC, BLT, BC, BGT, BHI, BLE, | PC= PC+nb+r12[-2048 to +2048]                 |

| bra       | nch instruction | BLS, BPL, BNV, BMI, BV, BNZ, BZ,  | or                                            |

|           |                 | BN, BP                            | PC = PC+nb+r8[-128  to  +127]                 |

|           |                 |                                   | nb: Instruction byte count                    |

| CA        | LL instruction  | CALLF a24                         | PC = a24                                      |

|           |                 | CALL Rb, Rs                       | PC = Rb << 16 + Rs                            |

|           |                 | ICALL Rb, Rs                      | Rb: Contents of base register                 |

|           |                 |                                   | Rs: Contents of general-purpose register      |

|           |                 | CALLR r12                         | PC = PC + 2 + r12[-2048  to  +2047]           |

|           |                 | ICALLR r12                        |                                               |

|           |                 | CALLR Rs                          | PC = PC + 2 + Rs[-32768  to  +32768]          |

|           |                 | ICALLR Rs                         |                                               |

| Ret       |                 | RET, IRET                         | PC32  to  00 = (SP)                           |

| inst      | ruction         |                                   | (SP) denotes the contents of the RAM location |

|           |                 |                                   | designated by the stack pointer value SP.     |

Table 2.2.1 Values Loaded in the PC

## 2.3 General-purpose Registers

## 2.3.1 Overview

This series of microcontrollers is provided with 16 general-purpose registers (R0 to R15).

Only the low-order 8 bits of these registers are used for execution in byte mode. The high-order 8 bits of a general-purpose register are loaded with 0 when these bits are loaded with data in byte mode.

| Name      | Symbol | Description                                                             |

|-----------|--------|-------------------------------------------------------------------------|

| R0 to R13 |        | 16-bit general-purpose registers                                        |

| R14       | PSW    | Used as a 16-bit register that indicates the state of the CPU.          |

| R15       | SP     | 16-bit register that is implicitly used as the subroutine stack pointer |

|           |        | Bit 0 of the SP must always be set to 0.                                |

## 2.3.2 R0 to R7

R0 to R7 are 16-bit registers that are used to store data and address values in various types of operations.

## 2.3.3 R8

- 1) R8 is a 16-bit register that is used to store data and address values in various types of operations.

- 2) It is used as a base address register by the 1-word MOVF instruction.

- 3) It is used as a base address register by the 2-word MOVF instruction.

- 4) It is used to designate PC32 to PC16 during the CALL, ICALL, and JMP instructions.

## 2.3.4 R9

- 1) R9 is a 16-bit register that is used to store data and address values in various types of operations.

- 2) It is used as a base address register by the 2-word MOVF instruction.

- 3) It is used to designate PC32 to PC16 during the CALL, ICALL, and JMP instructions.

## 2.3.5 R10 to R13

- 1) R10 to R13 are 16-bit registers that are used to store data and address values in various types of operations.

- 2) They are used as base address registers by the 2-word MOVF instruction.

## 2.3.6 R14 (PSW)

| Bit | Symbol | Description                                                                                                                                                                                                                          |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Z8     | Set to 1 when the low-order 8 bits of data are set to 0 during data transfer and arithmetic operation.                                                                                                                               |

| 1   | Z16    | Set to 1 when the data is set to 0 during data transfer and arithmetic operation. Z16 behaves in the same manner as Z8 during an 8-bit transfer operation.                                                                           |

| 2   | СҮ     | <ul><li>The value of CY changes in the following two cases:</li><li>Loaded with a carry or borrow from bit 15 as the result of arithmetic operation.</li><li>The value of CY changes with the shift or rotate instruction.</li></ul> |

| 3   | HC     | Loaded with a carry or borrow from bit 3 as a result of arithmetic operation.                                                                                                                                                        |

| 4   | OV     | Loaded with the overflow bit as a result of arithmetic operation.                                                                                                                                                                    |

| 5   | Р      | Set to 1 when the total number of data 1 during data transfer and arithmetic operation is an odd number.                                                                                                                             |

| 6   | S      | Stores the most significant bit of the last handled data.                                                                                                                                                                            |

| 7   | IE     | Enables interrupts.<br>* All types of interrupts are suppressed unless this bit is set to 1.                                                                                                                                         |

| 8   | IL0    | Control the interrupt level.                                                                                                                                                                                                         |

| 9   | IL1    | * When IE = 1, the CPU accepts the interrupt requests with an interrupt level higher                                                                                                                                                 |

| 10  | IL2    | than the one specified by IL2 to IL0.                                                                                                                                                                                                |

| 11  | WS     | Write control for exception interrupt control register. (0/1: disable/ enable)                                                                                                                                                       |

| 12  | N0     | Referenced by the instructions that designate registers with the values of N3 to N0.                                                                                                                                                 |

| 13  | N1     | These bits are loaded with the address of the general-purpose register that was used                                                                                                                                                 |

| 14  | N2     | for data transfer and arithmetic operation.                                                                                                                                                                                          |

| 15  | N3     |                                                                                                                                                                                                                                      |

R14 (PSW) is a 16-bit register that is used to save the state of the CPU.

Note: When MUL, DIV, DIVLH, SDIV, and SDIVLH instructions are executed, the flags change as follows. Z8, Z16, P, S: Changes according to the arithmetic operation results R0. HC, OV, N0 to N3: Cleared.

CY: The same value as S flag in the case of SDIV and SDIVLH instructions. Cleared in other instructions.

## 2.3.7 R15 (SP)

R15 (SP) is a 16-bit register that is used implicitly as the stack pointer for subroutines.

Since R15 is used as the subroutine stack pointer, it is necessary to make sure that bit 0 of the SP is always set to 0.

The value of the SP changes as follows:

| 1) | When a PUSH instruction is executed: | RAM(SP) = DATA, SP = SP + 2        |

|----|--------------------------------------|------------------------------------|

| 2) | When a CALL, CALLF, or CALLR         |                                    |

|    | instruction is executed:             | RAM(SP) = PCL, SP = SP + 2,        |

|    |                                      | RAM(SP) = PCH, SP = SP + 2         |

| 3) | When an ICALL, ICALLF, or ICALLR     |                                    |

|    | instruction is executed:             | RAM(SP) = PCL, SP = SP + 2,        |

|    |                                      | RAM(SP) = PCH, SP = SP + 2,        |

|    |                                      | RAM(SP) = PSW, SP = SP + 2         |

| 4) | When a POP instruction is executed:  | SP = SP - 2, $DATA = RAM$ ( $SP$ ) |

| 5) | When a RET instruction is executed:  | SP = SP - 2, $PCH = RAM$ ( $SP$ ), |

|    |                                      | SP = SP - 2, $PCL = RAM$ ( $SP$ )  |

|    |                                      |                                    |

#### **System Configuration**

6) When an IRET instruction is executed:

SP = SP - 2, PSW = RAM (SP), SP = SP - 2, PCH = RAM (SP), SP = SP - 2, PCL = RAM (SP)

\* PCL represents bits 0 to 15 of the PC (program counter) and PCH represents bits 16 to 31 of the PC.

## 2.4 Program Memory (ROM)

This series of microcontrollers incorporates a program memory (ROM) that is allocated to the program/data space as shown below.

| Model Name | Address                 | ROM Size    |

|------------|-------------------------|-------------|

| LC88F58B0A | 0000_8000H to 0002_7FFF | 128 K bytes |

Note: This series of microcontrollers uses the 256-byte area from 0002\_7F00 to 0002\_7FFF as the option area. This area cannot be used as a program area.

## 2.5 Data Memory (RAM)

This series of microcontrollers incorporates the RAM that is used as a data memory or program stack as shown below.

| Model Name | Address                  | RAM Size   |

|------------|--------------------------|------------|

| LC88F58B0A | 0000_0000H to 0000_17FFH | 6144 bytes |

## 2.6 Special Function Registers (SFRs)

This series of microcontrollers has special function registers allocated to addresses 0000\_7F00H to 0000\_7FFFH. They are used to control the peripheral module functions. The SFRs are listed in Table 2.6.1. For the definition of the registers in the SFR area, refer to individual register descriptions.

| Symbol | Address | R/W | Name                                           | Initial Value |

|--------|---------|-----|------------------------------------------------|---------------|

|        | 7F00    |     |                                                |               |

|        | 7F01    |     |                                                |               |

| IL1L   | 7F02    | R/W | Interrupt level setting register 1L            | 0000_0000     |

| IL1H   | 7F03    | R/W | Interrupt level setting register 1H            | 0000_0000     |

| IL2L   | 7F04    | R/W | Interrupt level setting register 2L            | 0000_0000     |

| IL2H   | 7F05    | R/W | Interrupt level setting register 2H            | 0000_0000     |

|        | 7F06    |     |                                                |               |

|        | 7F07    |     |                                                |               |

| EXCPL  | 7F08    | R/W | Exception interrupt control register low byte  | 0000_0000     |

| EXCPH  | 7F09    | R/W | Exception interrupt control register high byte | LL00_L0L0     |

| OCR0   | 7F0A    | R/W | Oscillation control register 0                 | 0000_0000     |

| OCR1   | 7F0B    | R/W | Oscillation control register 1                 | 0L00_L000     |

| WDTCR  | 7F0C    | R/W | Watchdog timer control register                | 0L00_0000     |

| RAND   | 7F0D    |     | System reserved register                       |               |

| BTCR   | 7F0E    | R/W | Base timer control register                    | 0000_0000     |

| PWRDET | 7F0F    |     | System reserved register                       |               |

| TOLR   | 7F10    | R/W | Timer 0 period setting register low byte       | 0000_0000     |

| TOHR   | 7F11    | R/W | Timer 0 period setting register high byte      | 0000_0000     |

| TOCNT  | 7F12    | R/W | Timer 0 control register                       | 0000_0000     |

| TOPR   | 7F13    | R/W | Timer 0 prescaler                              | 0000_0000     |

| T1LR   | 7F14    | R/W | Timer 1 period setting register low byte       | 0000_0000     |

| T1HR   | 7F15    | R/W | Timer 1 period setting register high byte      | 0000_0000     |

| T1CNT  | 7F16    | R/W | Timer 1 control register                       | 0000_0000     |

| T1PR   | 7F17    | R/W | Timer 1 prescaler                              | 0000_0000     |

| T2LR   | 7F18    | R/W | Timer 2 period setting register low byte       | 0000_0000     |

| T2HR   | 7F19    | R/W | Timer 2 period setting register high byte      | 0000_0000     |

| T2L    | 7F1A    | R   | Timer 2 counter                                | 0000_0000     |

| T2H    | 7F1B    | R   | Timer 2 counter                                | 0000_0000     |

| T2CNT0 | 7F1C    | R/W | Timer 2 control register 0                     | 0000_0000     |

| T2CNT1 | 7F1D    | R/W | Timer 2 control register 1                     | LLL0_0000     |

| T2CNT2 | 7F1E    | R/W | Timer 2 control register2                      | 000L_0000     |

|        | 7F1F    |     |                                                |               |

| ADCR   | 7F20    | R/W | AD converter control register                  | 0000_0000     |

| ADMR   | 7F21    | R/W | AD converter mode register                     | 0000_0000     |

| ADRL   | 7F22    | R/W | AD converter result register low byte          | 0000_0000     |

| ADRH   | 7F23    | R/W | AD converter result register high byte         | 0000_0000     |

Table 2.6.1 List of SFRs

Note 1: Null columns represent reserved areas and must not be accessed.

| Symbol  | Address | R/W | Name                                      | Initial Value |

|---------|---------|-----|-------------------------------------------|---------------|

|         | 7F24    |     |                                           |               |

|         | 7F25    |     |                                           |               |

|         | 7F26    |     |                                           |               |

|         | 7F27    |     |                                           |               |

| T3LR    | 7F28    | R/W | Timer 3 period setting register low byte  | 0000_0000     |

| T3HR    | 7F29    | R/W | Timer 3 period setting register high byte | 0000_0000     |

| T3L     | 7F2A    | R/W | Timer 3 counter                           | 0000_0000     |

| ТЗН     | 7F2B    | R/W | Timer 3 counter                           | 0000_0000     |

| T3CNT0  | 7F2C    | R/W | Timer 3 control register 0                | 0000_0000     |

| T3CNT1  | 7F2D    | R/W | Timer 3 control register 1                | LLLL_L000     |

| T3PR    | 7F2E    | R/W | Timer 3 prescaler control register        | 0000_0000     |

|         | 7F2F    |     |                                           |               |

| SOCNT   | 7F30    | R/W | SIO0 control register                     | 0000_0000     |

| SOBG    | 7F31    | R/W | SIO0 baudrate control register            | 0000_0000     |

| SOBUF   | 7F32    | R/W | SIO0 data buffer                          | 0000_0000     |

| SOINTVL | 7F33    | R/W | SIO0 interval register                    | 0000_0000     |

| S1CNT   | 7F34    | R/W | SIO1 control register                     | 0000_0000     |

| S1BG    | 7F35    | R/W | SIO1 baudrate control register            | 0000_0000     |

| S1BUF   | 7F36    | R/W | SIO1 data buffer                          | 0000_0000     |

| S1INTVL | 7F37    | R/W | SIO1 interval register                    | 0000_0000     |

| U0CR    | 7F38    | R/W | UART0 control register                    | 0000_1000     |

|         | 7F39    |     |                                           |               |

| U0RXL   | 7F3A    | R/W | UART0 receive register low byte           | 0000_0000     |

| U0RXH   | 7F3B    | R/W | UART0 receive register high byte          | LLLL_LL00     |

| U0TXL   | 7F3C    | R/W | UART0 transmit register low byte          | 0000_0000     |

| U0TXH   | 7F3D    | R/W | UART0 transmit register high byte         | LLLL_LLH0     |

|         | 7F3E    |     |                                           |               |

|         | 7F3F    |     |                                           |               |

| POLAT   | 7F40    | R/W | Port 0 data latch                         | 0000_0000     |

| POIN    | 7F41    | R   | Port 0 input address                      | XXXX_XXXX     |

| PODDR   | 7F42    | R/W | Port 0 direction control register         | 0000_0000     |

| POFSA   | 7F43    | R/W | Port 0 function control register A        | 0000_0000     |

| P1LAT   | 7F44    | R/W | Port 1 data latch                         | 0000_0000     |

| P1IN    | 7F45    | R   | Port 1 input address                      | XXXX_XXXX     |

| P1DDR   | 7F46    | R/W | Port 1 direction control register         | 0000_0000     |

| P1FSA   | 7F47    | R/W | Port 1 function control register A        | 0000_0000     |

| P2LAT   | 7F48    | R/W | Port 2 data latch                         | 0000_0000     |

| P2IN    | 7F49    | R   | Port 2 input address                      | XXXX_XXXX     |

| P2DDR   | 7F4A    | R/W | Port 2 direction control register         | 0000_0000     |

| P2FSA   | 7F4B    | R/W | Port 2 function control register A        | 0000_0000     |

| P3LAT   | 7F4C    | R/W | Port 3 data latch                         | LLLL_0000     |

| P3IN    | 7F4D    | R   | Port 3 input address                      | XXXX_XXXX     |

| P3DDR   | 7F4E    | R/W | Port 3 direction control register         | LLLL_0000     |

| P3FSA   | 7F4F    | R/W | Port 3 function control register A        | LLLL_0000     |

| Symbol    | Address | R/W | Name                                         | Initial Value |

|-----------|---------|-----|----------------------------------------------|---------------|

| P4LAT     | 7F50    | R/W | Port 4 data latch                            | 0000_0000     |

| P4IN      | 7F51    | R   | Port 4 input address                         | XXXX_XXXX     |

| P4DDR     | 7F52    | R/W | Port 4 direction control register            | 0000_0000     |

| P4FSA     | 7F53    | R/W | Port 4 function control register A           | 0000_0000     |

|           | 7F54    |     |                                              |               |

|           | 7F55    |     |                                              |               |

|           | 7F56    |     |                                              |               |

|           | 7F57    |     |                                              |               |

| P6LAT     | 7F58    | R/W | Port 6 data latch                            | 0000_0000     |

| P6IN      | 7F59    | R   | Port 6 input address                         | XXXX_XXXX     |

| P6DDR     | 7F5A    | R/W | Port 6 direction control register            | 0000_0000     |

|           | 7F5B    |     |                                              |               |

| P7LAT     | 7F5C    | R/W | Port 7 data latch                            | LLLL_L000     |

| P7IN      | 7F5D    | R   | Port 7 input address                         | LLLL_LXXX     |

| P7DDR     | 7F5E    | R/W | Port 7 direction control register            | LLLL_L000     |

|           | 7F5F    |     |                                              |               |

| SMIC0CNT  | 7F60    | R/W | I <sup>2</sup> C control register 0          | 0000_0000     |

| SMICOSTA  | 7F61    | R/W | I <sup>2</sup> C status register 0           | 0000_0000     |

| SMIC0BRG  | 7F62    | R/W | I <sup>2</sup> C baudrate control register 0 | 0000_0000     |

| SMICOBUF  | 7F63    | R/W | I <sup>2</sup> C data buffer 0               | 0000_0000     |

|           | 7F64    |     |                                              |               |

|           | 7F65    |     |                                              |               |

|           | 7F66    |     |                                              |               |

|           | 7F67    |     |                                              |               |

| SMICOPCNT | 7F68    | R/W | I <sup>2</sup> C port control register 0     | LLLL_0000     |

|           | 7F69    |     |                                              |               |

|           | 7F6A    |     |                                              |               |

|           | 7F6B    |     |                                              |               |

| U2CNT0    | 7F6C    | R/W | UART2 control register 0                     | 0010_0000     |

| U2CNT1    | 7F6D    | R/W | UART2 control register 1                     | 0000_0000     |

| U2TBUF    | 7F6E    | R/W | UART2 transmit data register                 | 0000_0000     |

| U2RBUF    | 7F6F    | R   | UART2 receive data register                  | 0000_0000     |

|           | 7F70    |     |                                              |               |

|           | 7F71    |     |                                              |               |

|           | 7F72    |     |                                              |               |

|           | 7F73    |     |                                              |               |

| U2BG      | 7F74    | R/W | UART2 baudrate control register              | 0000_0000     |

|           | 7F75    |     |                                              |               |

| FSR0      | 7F76    |     | System reserved register                     |               |

|           | 7F77    |     |                                              |               |

|           | 7F78    |     |                                              |               |

|           | 7F79    |     |                                              |               |

|           | 7F7A    |     |                                              |               |

|           | 7F7B    |     |                                              |               |

| Symbol         | Address      | R/W | Name                                      | Initial Value |

|----------------|--------------|-----|-------------------------------------------|---------------|

|                | 7F7C         |     |                                           |               |

|                | 7F7D         |     |                                           |               |

|                | 7F7E         |     |                                           |               |

|                | 7F7F         |     |                                           |               |

| USM0CTL        | 7F80         | R/W | USM0 control register                     | 0000_0000     |

| <b>USM0NPH</b> | 7F81         | R/W | USM0 phase number setup register          | 0000_0000     |

| <b>USM0TWL</b> | 7F82         | R/W | USM0 period setup register low byte       | 0000_0000     |

| USM0TWH        | 7F83         | R/W | USM0 period setup register high byte      | 00LL_0000     |

| USM0LPL        | 7F84         | R/W | USM0 low period setup register low byte   | 0000_0000     |

| USM0LPH        | 7F85         | R/W | USM0 low period setup register high byte  | LOOL_LLOO     |

| USM0PSF        | 7F86         | R/W | USM0 output waveform setup register       | 0000_L000     |

|                | 7F87         |     |                                           |               |

| USM0PLLC       | 7F88         | R/W | USM0 PLL control register                 | 0L00_0000     |

|                | 7F89         |     |                                           |               |

|                | 7F8A         |     |                                           |               |

|                | 7F8B         |     |                                           |               |

|                | 7F8C         |     |                                           |               |

|                | 7F8D         |     |                                           |               |

|                | 7F8E         |     |                                           |               |

|                | 7F8F         |     |                                           |               |

|                | 7F90         |     |                                           |               |

|                | 7F91         |     |                                           |               |

|                | 7F92         |     |                                           |               |

|                | 7F93         |     |                                           |               |

|                | 7F94         |     |                                           |               |

|                | 7F95         |     |                                           |               |

|                | 7F96         |     |                                           |               |

|                | 7F97         |     |                                           |               |

|                | 7F98         |     |                                           |               |

|                | 7F99         |     |                                           |               |

|                | 7F9A         |     |                                           |               |

|                | 7F9B<br>7F9C |     |                                           |               |

|                | 7F9C<br>7F9D |     |                                           |               |

|                | 7F9E         |     |                                           |               |

|                | 7F9F         |     |                                           |               |

| T4LR           | 7FA0         | R/W | Timer 4 period setting register low byte  | 0000_0000     |

| T4HR           | 7FA1         | R/W | Timer 4 period setting register low byte  | 0000_0000     |

| T5LR           | 7FA2         | R/W | Timer 5 period setting register low byte  | 0000 0000     |

| T5HR           | 7FA3         | R/W | Timer 5 period setting register high byte | 0000_0000     |

| T45CNT         | 7FA4         | R/W | Timer 45 control register                 | 0000_0000     |

|                | 7FA5         |     |                                           |               |

|                | 7FA6         |     |                                           |               |

|                | 7FA7         |     |                                           |               |

| Symbol | Address | R/W | Name                               | Initial Value |

|--------|---------|-----|------------------------------------|---------------|

|        | 7FA8    |     |                                    |               |

|        | 7FA9    |     |                                    |               |

| PWM0AL | 7FAA    | R/W | PWM0A compare register L           | 0000_LLLL     |

| PWM0AH | 7FAB    | R/W | PWM0A compare register H           | 0000_0000     |

| PWM0BL | 7FAC    | R/W | PWM0 B compare register L          | 0000_LLLL     |

| PWM0BH | 7FAD    | R/W | PWM0 B compare register H          | 0000_0000     |

| PWM0C  | 7FAE    | R/W | PWM0 control register              | 0000_0000     |

| PWM0PR | 7FAF    | R/W | PWM0 prescaler                     | 0000_0000     |

|        | 7FB0    |     |                                    |               |

|        | 7FB1    |     |                                    |               |

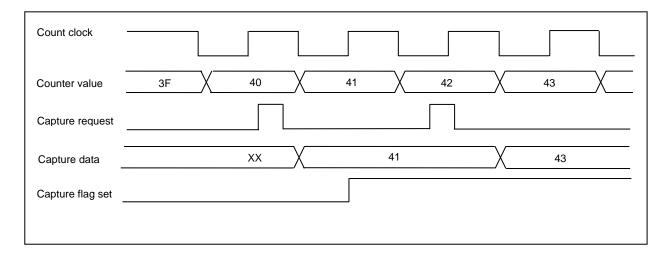

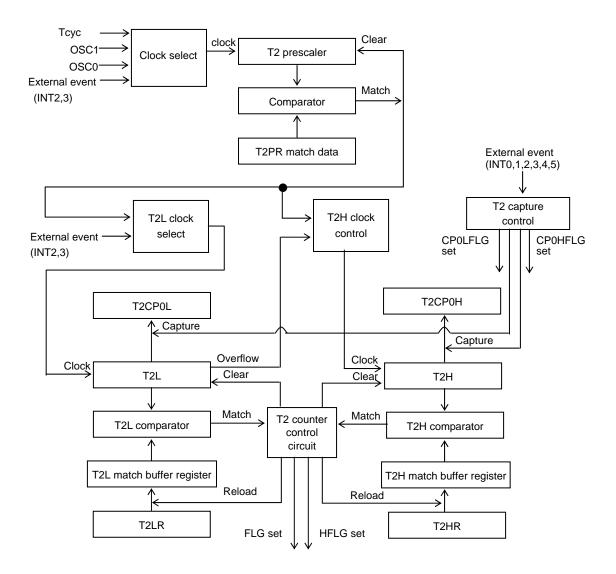

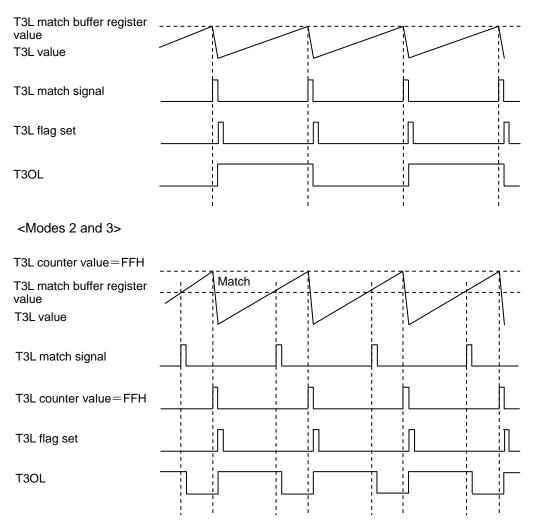

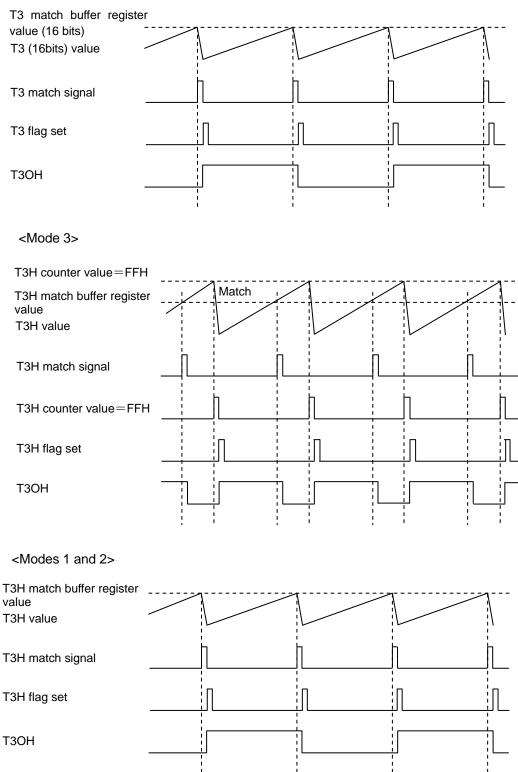

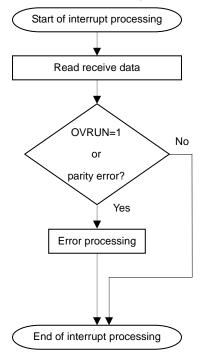

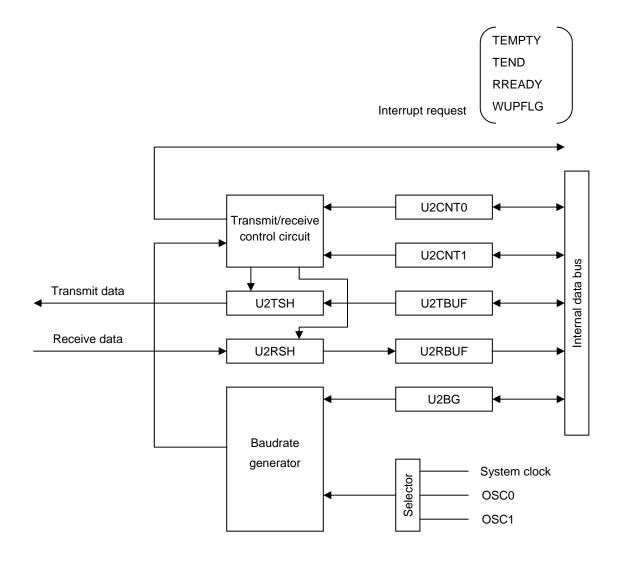

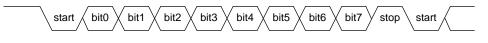

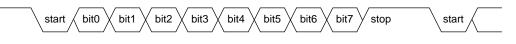

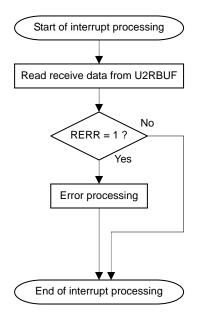

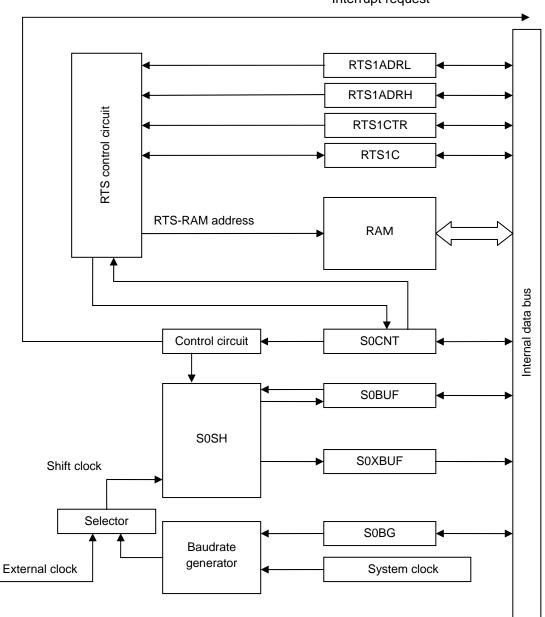

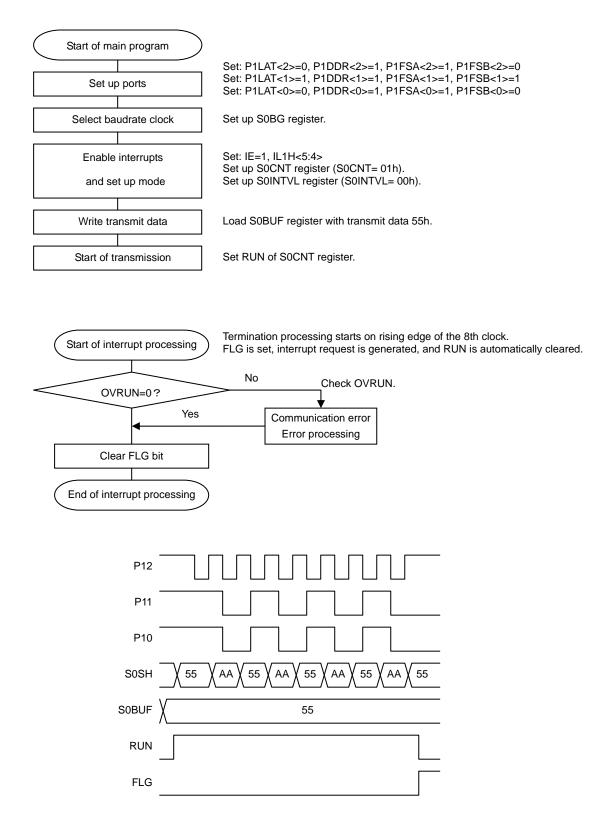

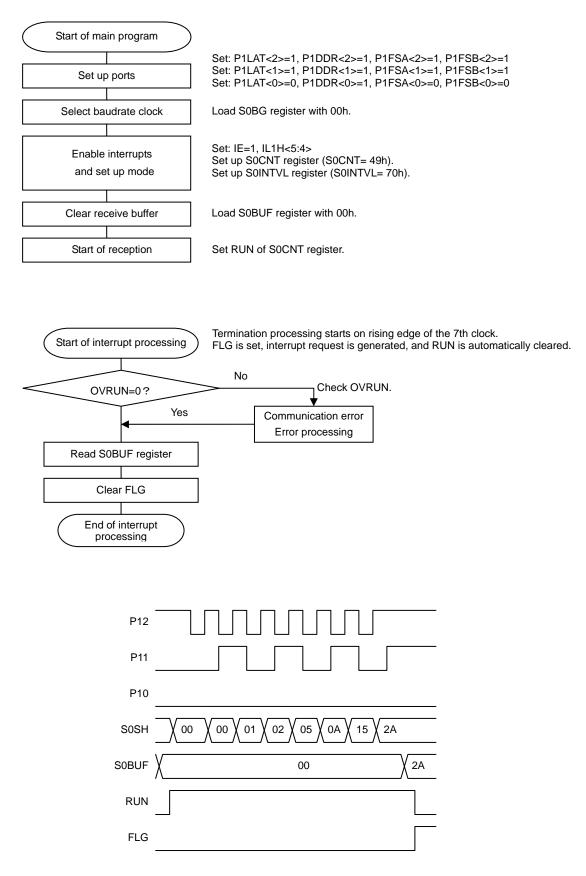

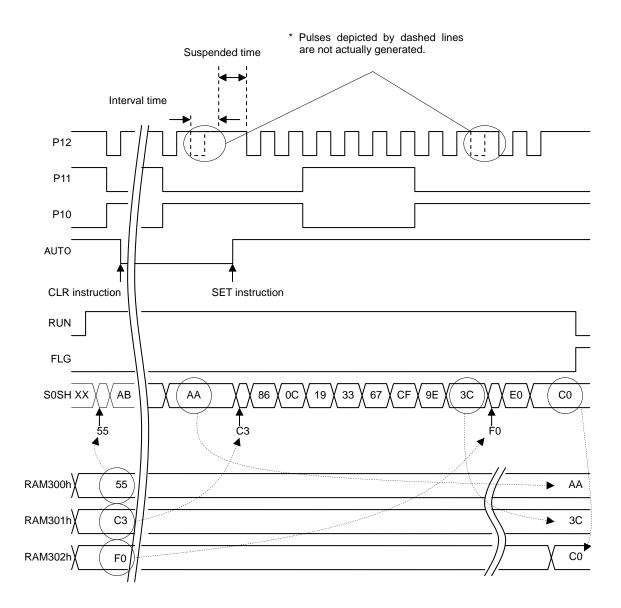

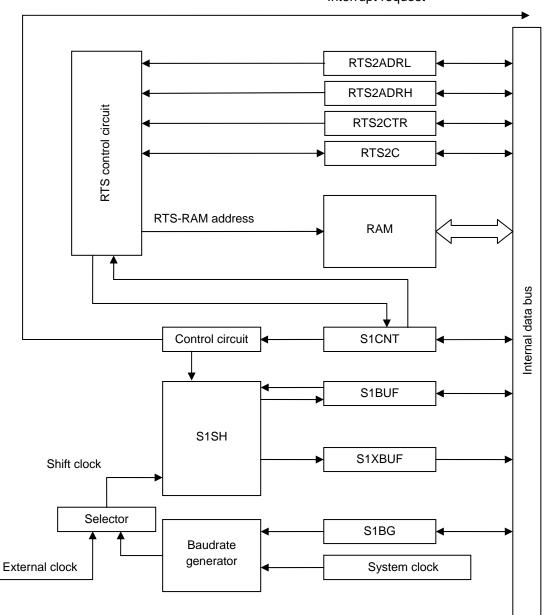

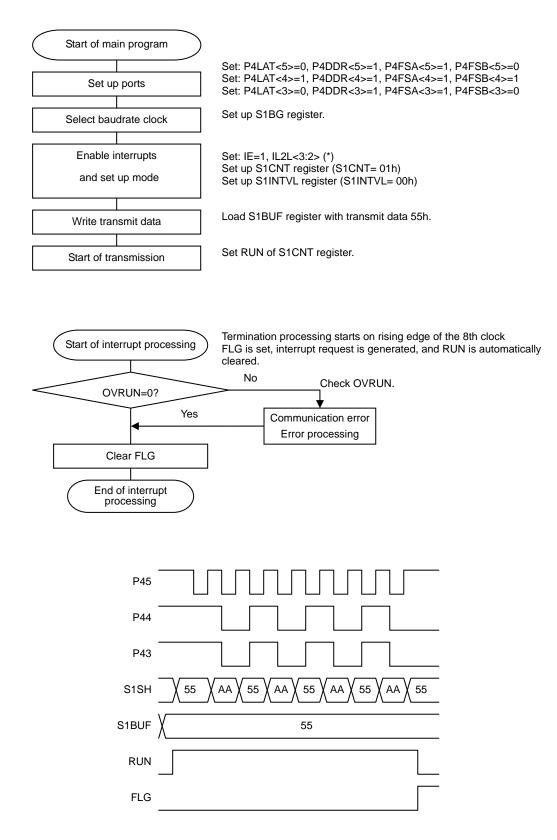

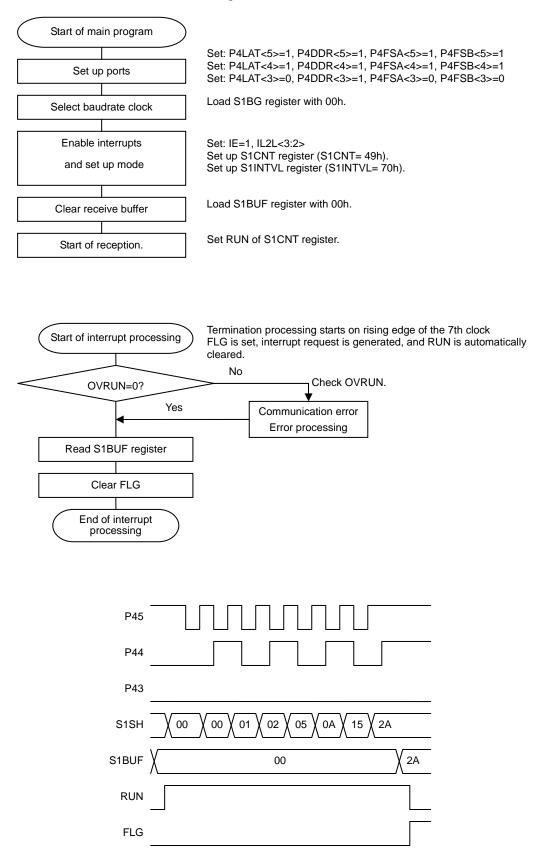

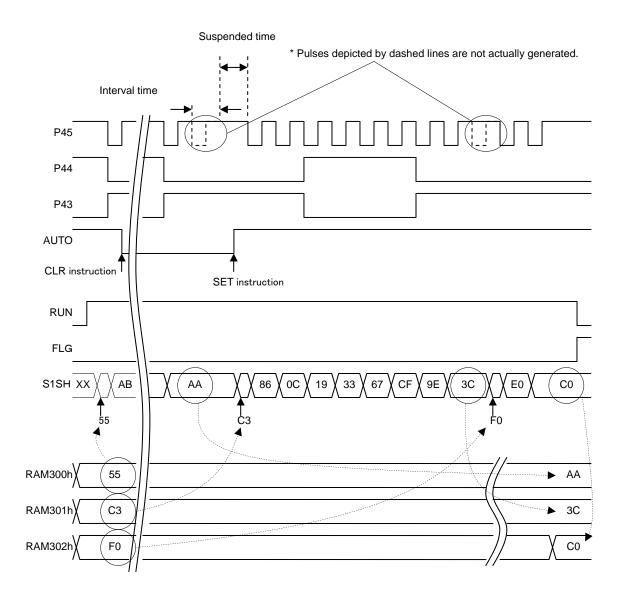

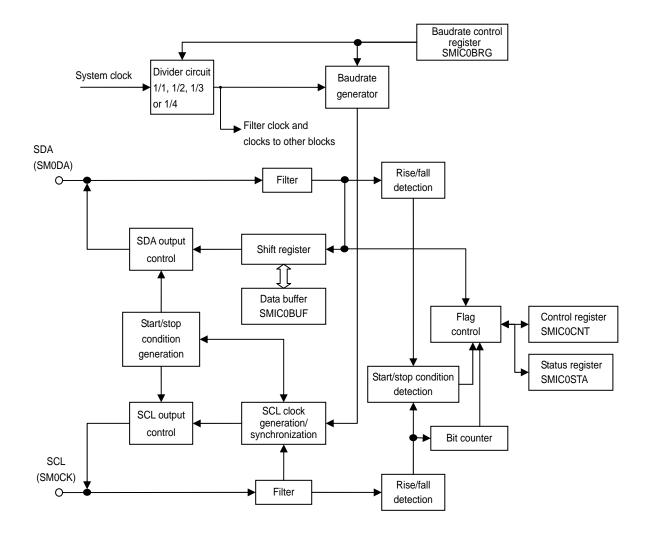

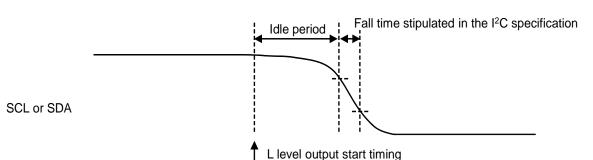

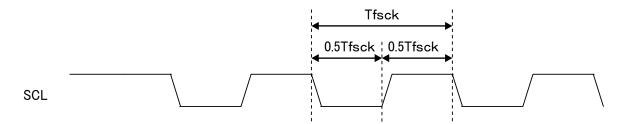

|        | 7FB2    |     |                                    |               |