**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# STK681-332-E STK681-352-E

# Intelligent Power Module DC Brush Motor Driver Application Note

#### Overview

The STK681-332-E and STK681-352-E are IPM (Intelligent Power Module) for use in current control forward/reverse DC motor driver with brush.

#### Features

- Allows forward, reverse, and brake operations in accordance with the external input signal.

- 12A peak startup output current and 12A peak brake output current.

- On-chip output short-circuits detection function.

- Connecting an external current detection resistor allows overcurrent detection and peak current control in the PWM operation mode.

- Obviate the need to design for the dead time in order to turn off the upper- and lower drive devices, when switching between the forward and reverse operation mode.

#### Applications

• Office photocopiers, printers, etc.

#### **Selection Guide**

| Parameter                                  | STK681-332-E | STK681-352-E |

|--------------------------------------------|--------------|--------------|

| Operating supply voltage 1 V <sub>CC</sub> | 10 to 38V    | 18 to 29V    |

| Operating supply voltage 2 V <sub>DD</sub> | 5V±5%        | No need      |

| Output current (Tc=105°C)                  | 5A           | 3.8A         |

| Brake current                              | 12A          | 12A          |

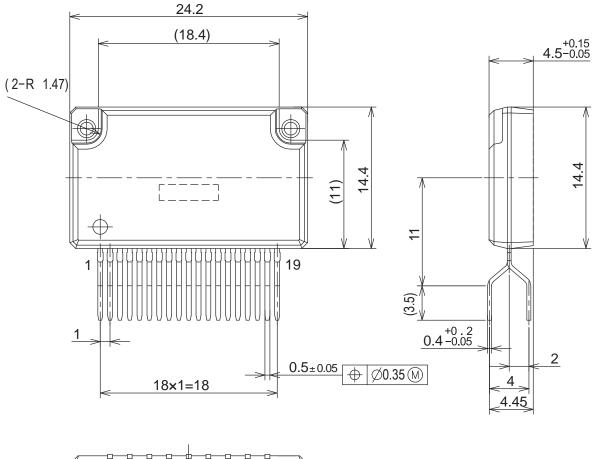

#### **Package Dimensions**

STK681-332-E STK681-352-E unit : mm (typ)

**SIP19 24.2x14.4** CASE 127BA ISSUE O

Recommend hole size for Lead Frame on PCB; 0.9 mm (max)

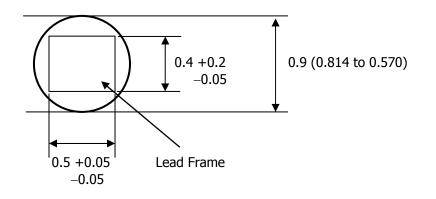

# Pin Assignment STK681-332-E

STK681-352-E

|        | Г  |            |            |  |

|--------|----|------------|------------|--|

| CND    | 4  | $\bigcirc$ |            |  |

| GND    | 1  | $\bigcirc$ |            |  |

| GND    | 2  |            |            |  |

| GND    | 3  |            |            |  |

| OUT2   | 4  |            |            |  |

| N.C    | 5  |            |            |  |

| OUT2   | 6  |            |            |  |

| VCC    | 7  |            | လု         |  |

| OUT1   | 8  |            | TK         |  |

| VCC    | 9  |            | 58         |  |

| OUT1   | 10 |            | ц<br>Ц     |  |

| N.C    | 11 |            | STK681-352 |  |

| N.C    | 12 |            | •          |  |

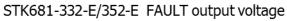

| FAULT  | 13 |            |            |  |

| S.GND  | 14 |            |            |  |

| N.C    | 15 |            |            |  |

| IN1    | 16 |            |            |  |

| IN2    | 17 |            |            |  |

| ENABLE | 18 |            |            |  |

| Vref   | 19 |            |            |  |

|        |    |            |            |  |

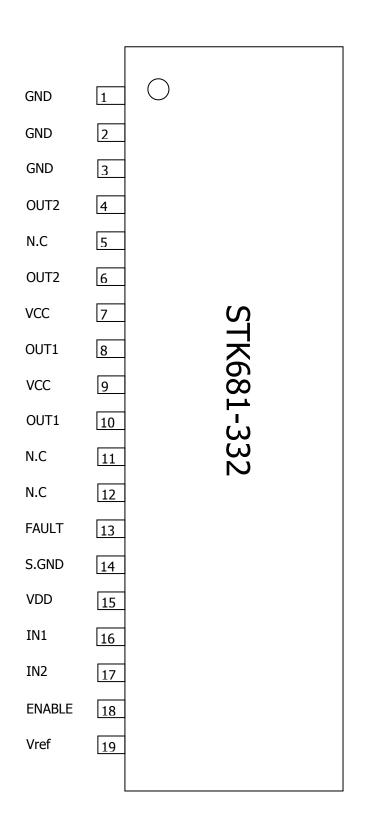

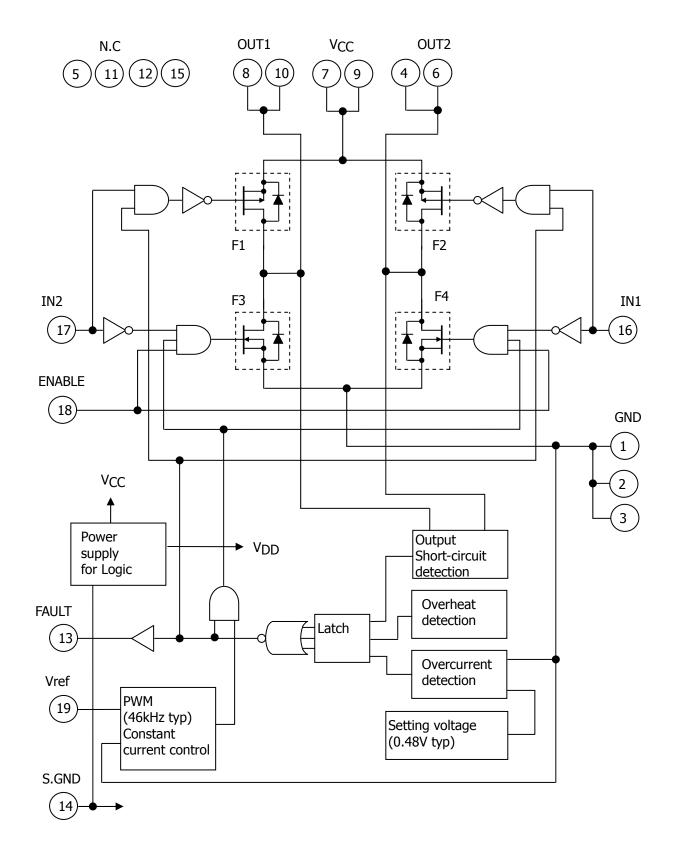

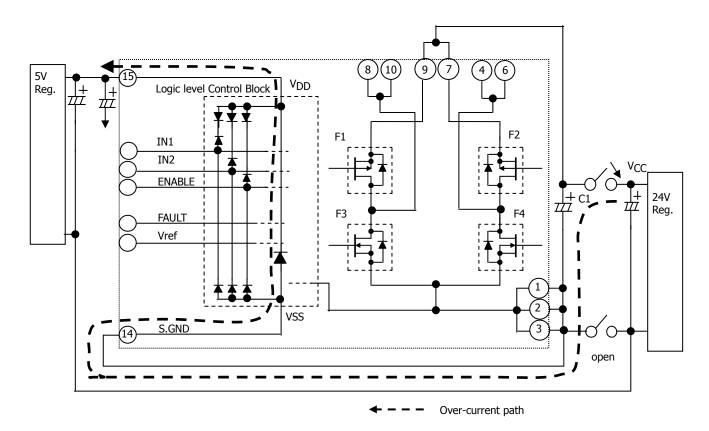

#### **Block Diagram**

STK681-332-E

STK681-352-E

#### **Specifications**

Absolute Maximum Ratings at Tc=25°C

| Parameter                       | Sumbol              | Canditian                                                                                        | Ratin          |            |      |

|---------------------------------|---------------------|--------------------------------------------------------------------------------------------------|----------------|------------|------|

| Parameter                       | Symbol              | Condition                                                                                        | STK681-332     | STK681-352 | unit |

| Maximum supply voltage 1        | V <sub>CC</sub> max | V <sub>DD</sub> =0V                                                                              | 52 3           |            | V    |

| Maximum supply<br>voltage 2     | V <sub>DD</sub> max | No signal                                                                                        | –0.3 tc        | 6.0        | V    |

| Input voltage                   | VIN max             | Logic input pins                                                                                 | –0.3 to        | 6.0        | V    |

| Output current1                 | Io1max              | V <sub>DD</sub> =5.0V,<br>DC current                                                             | 8.5            | 6.4        | А    |

| Output current2                 | Io2max              | V <sub>DD</sub> =5.0V,<br>Pulse current: 5ms                                                     | 12             | -          | А    |

|                                 |                     | Pulse current: 10ms                                                                              | -              | 8          | Α    |

| Brake current                   | IoBmax              | VDD=5.0V,<br>square wave<br>current, operating<br>time 15ms<br>(single pulse, low<br>side brake) | 12             | 12         | A    |

| Allowable power<br>dissipation  | PdPKmax             | No heat sink                                                                                     | 2.8            |            | W    |

| Operating substrate temperature | Тс                  | Metal surface<br>temperature of the<br>package                                                   | he -20 to +105 |            | °C   |

| Junction temperature            | Tjmax               |                                                                                                  | 150            | )          | °C   |

| Storage temperature             | Tstg                |                                                                                                  | –40 to ·       | °C         |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Allowable Operating Ratings at Ta=25°C

| Parameter                     | Symbol             | Condition                                                                                            | Ratin                | unit       |      |

|-------------------------------|--------------------|------------------------------------------------------------------------------------------------------|----------------------|------------|------|

| Parameter                     | Symbol             | Condition                                                                                            | STK681-332           | STK681-352 | unit |

| Operating supply voltage 1-1  | V <sub>CC</sub> -1 | With signals<br>applied(Tc=105°C)                                                                    | 10 to 38             | 10 to 20   | v    |

| Operating supply voltage 1-2  | V <sub>CC</sub> -2 | With signals<br>applied(Tc=90°C)                                                                     | 10 to 42             | 18 to 29   | v    |

| Operating supply<br>voltage 2 | V <sub>DD</sub>    | With signals<br>applied                                                                              | 5.0±5%               | -          | V    |

| Input voltage                 | VIN                |                                                                                                      | 0 to V <sub>DD</sub> | 0 to 5.5   | V    |

| Output current 1              | Io1                | V <sub>DD</sub> =5.0V, DC<br>current, Tc=80°C                                                        | 6.1                  | 4.6        | А    |

| Output current 2              | Io2                | V <sub>DD</sub> =5.0V, DC<br>current, Tc=105°C                                                       | 5                    | 3.8        | А    |

| Brake current                 | ІоВ                | V <sub>DD</sub> =5.0V, square<br>wave current,<br>operating time 2ms,<br>Low side brake,<br>Tc=105°C | 12                   | 12         | A    |

Refer to the graph for each conduction-period tolerance range for the output current and brake current.

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## Electrical Characteristics at Tc=25°C, V\_{CC}=24V, V\_{DD}=5.0V

| Parameter                                     | Symbol Conditions |                                  | Ratings |      |     |      |

|-----------------------------------------------|-------------------|----------------------------------|---------|------|-----|------|

| Parameter                                     |                   |                                  | min     | typ  | max | unit |

| V <sub>DD</sub> supply current(STK681-332-E)  | Icco              | Forward or reverse operation     |         | 6    | 9   | mA   |

| V <sub>CC</sub> supply current(STK681-352-E)  | Icco              | ENABLE=GND, IN1=IN2=3.3V         |         | 9.3  | 11  | mA   |

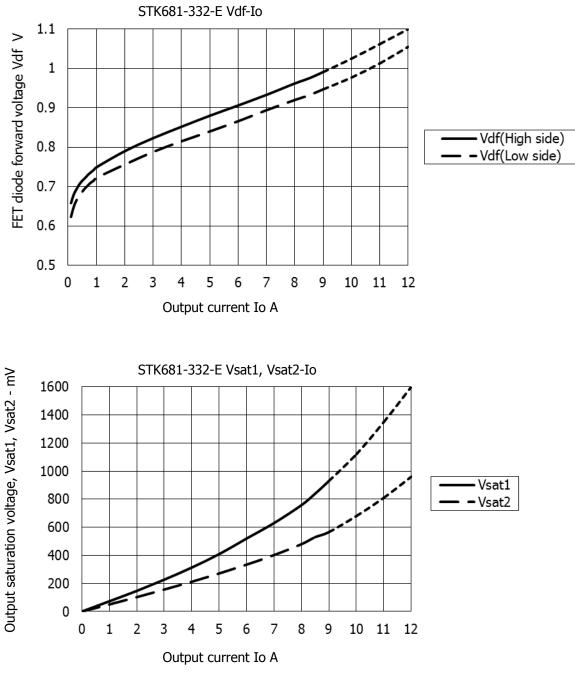

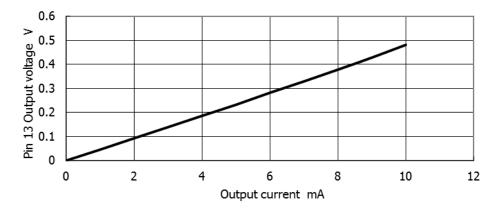

| FET diode forward voltage<br>(STK681-332-E)   | Vdf               |                                  |         | 0.75 | 1.4 | ۷    |

| FET diode forward voltage<br>(STK681-352-E)   | vai               | If=1A(RL=23 $\Omega$ )           |         | 0.76 | 1.4 | ۷    |

| Output saturation voltage 1<br>(STK681-332-E) | Vcat1             | Vsat1 RL=23Ω, F1, F2             |         | 65   | 100 | mV   |

| Output saturation voltage 1<br>(STK681-352-E) | vsati             |                                  |         | 140  | 200 | mV   |

| Output saturation voltage 2                   | Vsat2             | RL=23Ω, F3, F4                   |         | 50   | 85  | mV   |

| Output leak current                           | IOL               | F1, F2, F3, and F4 OFF operation |         |      | 50  | μA   |

| Input high voltage                            | VIH               | IN1, IN2, ENABLE pins            | 2.5     |      |     | V    |

| Input low voltage                             | VIL               | IN1, IN2, ENABLE pins            |         |      | 0.8 | V    |

| High level input current<br>(STK681-332-E)    | IILH              | IN1, IN2, ENABLE pins, VIH=5V    |         | 50   | 75  | μA   |

| High level input current<br>(STK681-352-E)    | IILH              | IN1, IN2, ENABLE pins, VIH=3.3V  |         | 33   | 50  | μA   |

| Low level input current                       | IILL              | IN1, IN2, ENABLE pins, VIL=GND   |         |      | 10  | μA   |

| Overcurrent detection voltage                 | VOC               | Between pins Vref1 and S.P       |         | 0.48 |     | V    |

| Internal PWM frequency                        | fc                |                                  | 32      | 46   | 62  | kHz  |

| Overheat detection temperature                | TSD               | Design guarantee                 |         | 144  |     | °C   |

Notes :

A fixed-voltage power supply must be used.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

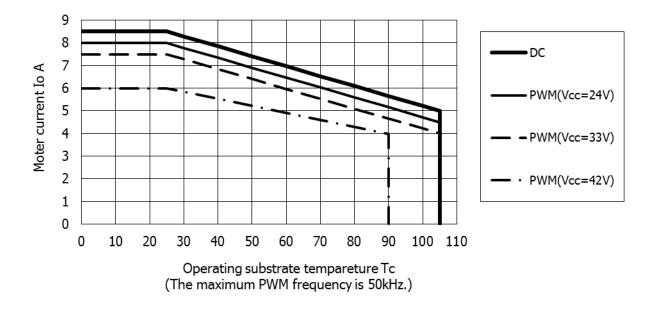

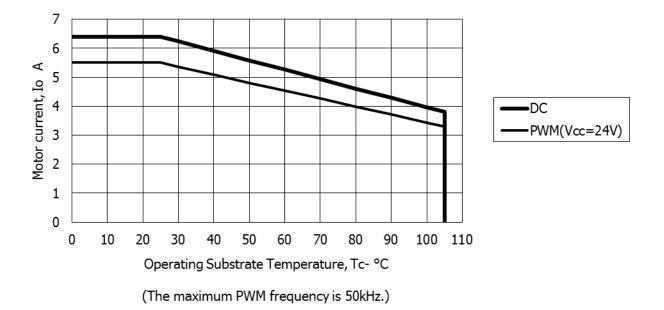

STK681-332-E motor current derating curve for the operating substrate temperature Tc

The PWM frequencies in the above graph indicate the ENABLE signal.

The same PWM Io derating curves as those shown above will be obtained when the internal PWM frequency of the STK681-332-E is used.

Increasing the Vcc supply voltage narrows the Io derating curve range, so Io should be set in reference to the above graph.

The above operating substrate temperature, Tc, is measured immediately when the motor is started. Since Tc fluctuates due to the ambient temperature, Ta, the motor current value, and continuous or intermittent operations of the motor current, always confirms these values using an actual set. The Tc temperature should be checked in the center of the metal surface of the product package.

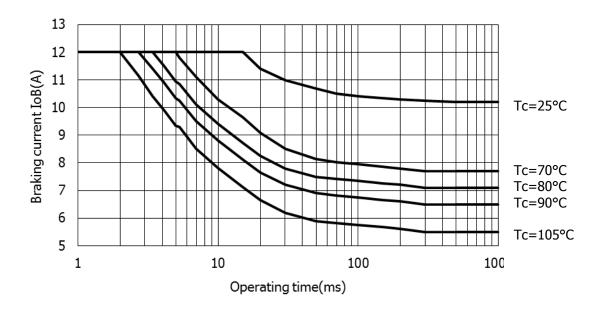

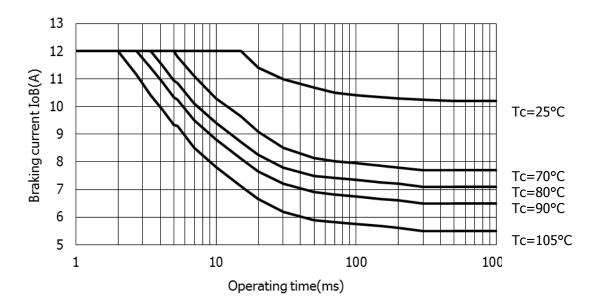

Allowable STK681-332-E braking current ranges

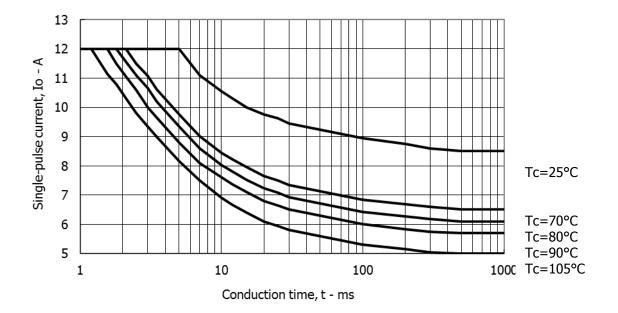

STK681-332-E Allowable Brake Current Range (High side: F1, F2=ON) or Allowable Startup Current Range

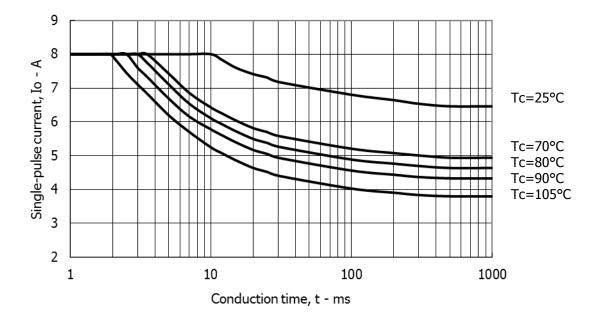

Derating Curve of Motor Current, Io, vs. STK681-352-E Operating Board Temperature, Tc

The PWM frequencies in the above graph indicate the ENABLE signal.

The same PWM Io derating curves as those shown above will be obtained when the internal PWM frequency of the STK681-352-E is used.

Increasing the Vcc supply voltage narrows the Io derating curve range, so Io should be set in reference to the above graph.

The above operating substrate temperature, Tc, is measured immediately when the motor is started. Since Tc fluctuates due to the ambient temperature, Ta, the motor current value, and continuous or intermittent operations of the motor current, always confirms these values using an actual set.

The Tc temperature should be checked in the center of the metal surface of the product package.

Allowable STK681-352-E braking current ranges

STK681-352-E Allowable Brake Current Range (High side: F1, F2=ON) or Allowable Startup Current Range

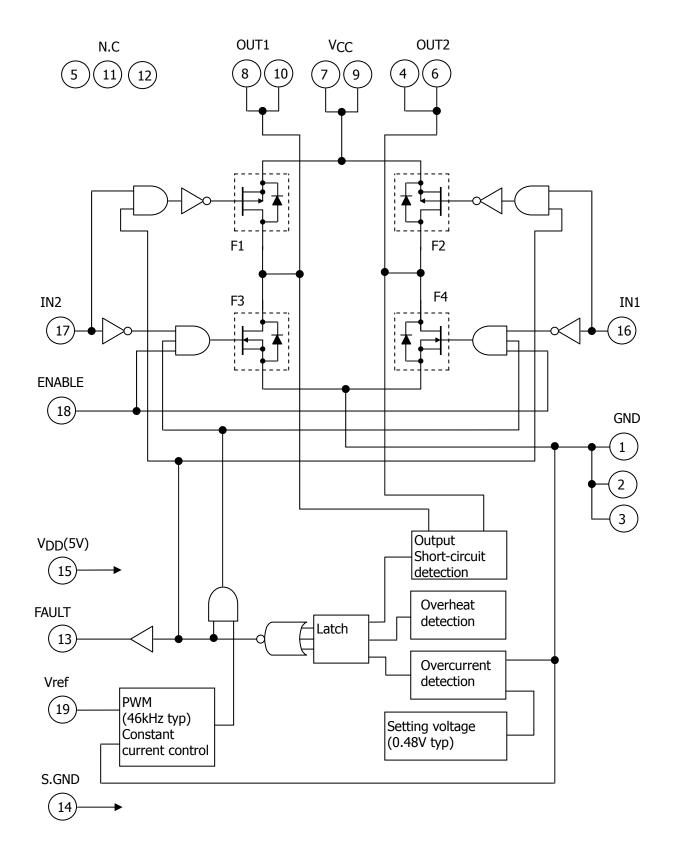

### **Pin Functions**

| Pin Functi<br>Pin Name | Pin No.    | Pin Function                                                                                                                                                                                                                                                                                            | Equivalent circuit                                           |

|------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| IN1                    | 16         | Input pin for turning F2 and F4 ON and<br>OFF<br>At low level F2: ON and F4: OFF; at<br>high level, F2: OFF and F4: ON                                                                                                                                                                                  | V <sub>DD</sub>                                              |

| IN2                    | 17         | Input pin for turning F1 and F3 ON and<br>OFF<br>At low level F1: ON and F3: OFF; at<br>high level, F1: OFF and F3: ON                                                                                                                                                                                  |                                                              |

| ENABLE                 | 18         | Pin for turning F3 and F4 ON; At high<br>level F31 and F42: ON<br>ENABLE must be set Low when VDD is<br>rising and falling.<br>ENABLE must be set High to drive the<br>motor.                                                                                                                           |                                                              |

| FAULT                  | 13         | Monitor pin used when either of the<br>output short-circuit detector,<br>overcurrent detector, or overheat<br>detector is activated.<br>When the detector is activated, this pin<br>is set low and all of F1, F2, F3 and F4 in<br>the final stage are latched off.                                      | V <sub>DD</sub>                                              |

| OUT1                   | 8, 10      | This pin connects to the motor and<br>outputs source/sync current<br>depending on conditions at IN1 and<br>IN2.                                                                                                                                                                                         |                                                              |

| OUT2                   | 4, 6       | This pin connects to the motor and<br>outputs source/sync current<br>depending on conditions at IN1 and<br>IN2.                                                                                                                                                                                         | F3 F4<br>F3 GND                                              |

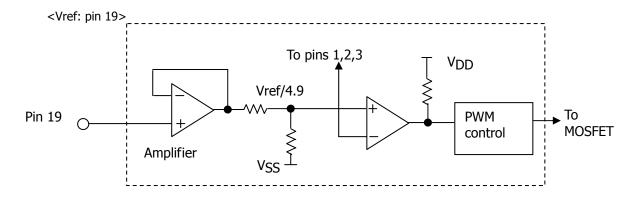

| Vref                   | 19         | This pin limits the peak current when<br>motor startup.<br>The current setting voltage, Vref, is set<br>to the value of 4.9 times the voltage<br>drop of the external current detection<br>resistor.<br>The internal overcurrent detection<br>level is 0.48V, so setting<br>Vref < 2.0V is recommended. | (19)<br>(19)<br>(19)<br>(19)<br>(19)<br>(19)<br>(19)<br>(19) |

| GND                    | 1, 2, 3    | Power system ground                                                                                                                                                                                                                                                                                     |                                                              |

| S.GND<br>Vcc           | 14<br>7, 9 | Control system ground<br>Motor system supply voltage                                                                                                                                                                                                                                                    |                                                              |

| V <sub>DD</sub>        | 15         | Control system supply voltage                                                                                                                                                                                                                                                                           | STK681-332-E                                                 |

| N.C                    | 15         | N.C                                                                                                                                                                                                                                                                                                     | STK681-352-E                                                 |

#### **Description of operation**

#### Input pins

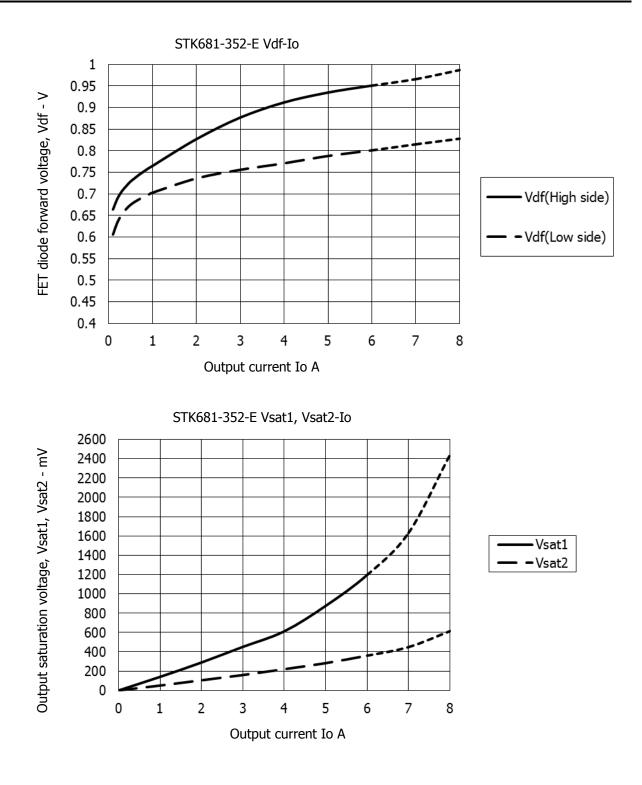

<IN1: pin 16, IN2: pin 17, ENABLE: pin 18> The input pins of this driver all use Schmitt input. Typical specifications at Tc=25°C are given below. Hysteresis voltage is 0.3V (VIHa-VILa).

Thus, the input voltage level must be considered as;

VIH=2.5Vmin

VIL=0.8Vmax

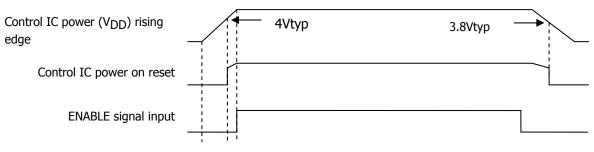

#### **Reduced voltage detection**

#### STK681-332-E

#### (1) V<sub>DD</sub>

The internal control IC of the driver has a function that detects reduced voltage when V<sub>DD</sub> is supplied. This reduced voltage threshold level is set to 4V (typ.), and the MOSFET gate voltage specification is 5V  $\pm$ 5%. So, a current flow through the output when V<sub>DD</sub> is rising results in the power stress to the MOSFET due to insufficient gate voltage.

To prevent this power stress, set ENABLE = Low when  $V_{DD} < 4.75V$ , which is outside the normal operating supply voltage range of the MOSFET.

V<sub>DD</sub>, ENABLE Signals Input Timing

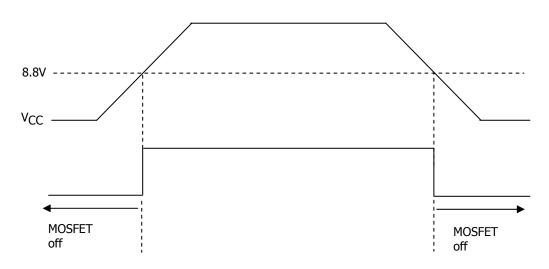

#### (2) V<sub>CC</sub>

The internal control IC of the driver has a function that detects reduced voltage when  $V_{CC}$  is supplied, to prevent insufficient internal P-channel MOSFET gate voltage. The reduced voltage detection level is set to  $V_{CC} = 8.8V(typ.)$ .

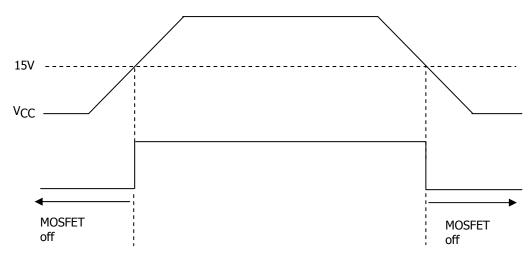

#### STK681-352-E

V<sub>CC</sub> Reduced voltage detection

The internal control IC of the driver has a function that detects reduced voltage when  $V_{CC}$  is supplied, to prevent insufficient internal P-channel MOSFET gate voltage. The reduced voltage detection level is set to  $V_{CC} = 15V(typ.)$ .

When  $V_{CC} < 15V$ , an internal control voltage has not risen above the preset threshold level, so ENABLE must be set to low in order to turn off the MOSFET.

#### Output short-circuit detection, Overcurrent Detection and Overheat Detection

Each detection function operates using a latch system and turns output off. To restore output operation, turn the V<sub>DD</sub> power supply off and then on again to apply a power-on reset.

[Output Short-circuit Detection, Overcurrent Detection]

When the output pin is simply connected to the circuit GND or  $V_{CC}$ , or when the output load is short-circuited, the output short circuit detector must be activated and turn the output off.

Constant current PWM control can be performed by connecting a current detection resistor to pins 1, 2 and 3, and setting the Vref pin voltage to less than 2.0V. In addition, when this current detection resistor voltage exceeds 0.48V(typ.), the overcurrent detector is activated and shuts the output off.

[Overheat Detection]

Rather than directly detecting the temperature of the semiconductor device, overheat detection detects the temperature

of the aluminum substrate (144°C typ).

Within the allowed operating range of IO1 (6.1A:STK681-332-E, 4.6A:STK681-352-E) recommended in the specifications, if a heat sink attached for the purpose of reducing the operating substrate temperature, Tc, comes loose, the semiconductor can operate without breaking.

However, we cannot guarantee operations without breaking in the case of operation other than those recommended, such as operations at a current exceeding IOH max (6.1A:STK681-332-E, 4.6A:STK681-352-E) that occurs before overcurrent detection is activated.

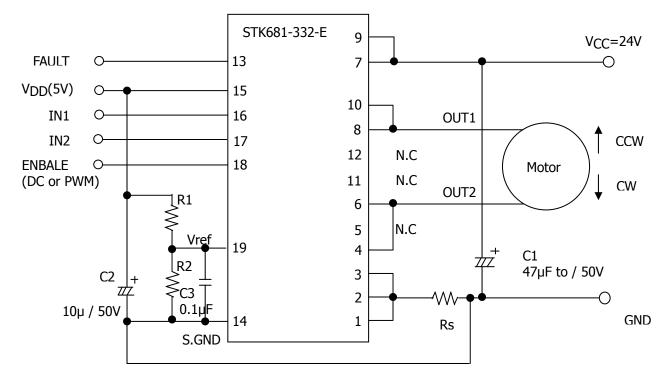

#### Application Circuit Example (STK681-332-E)

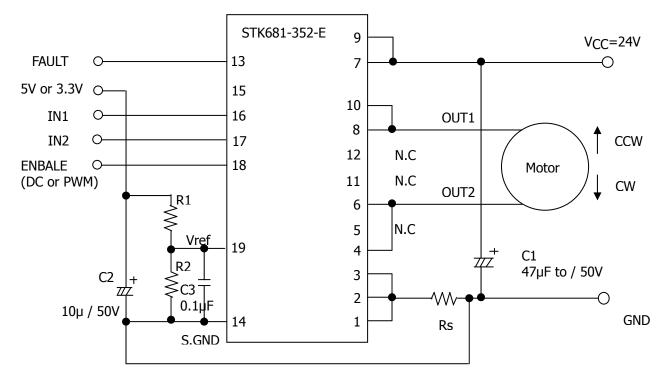

#### Application Circuit Example (STK681-352-E)

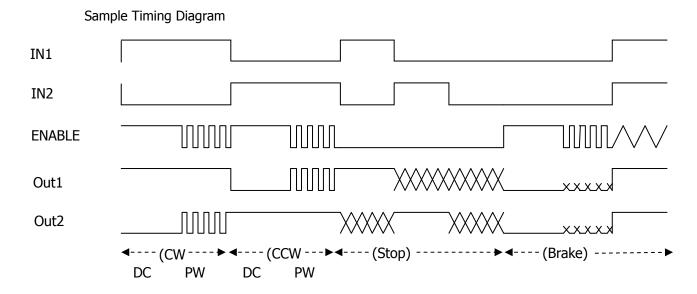

|         | IN1       | IN2 | ENABLE | Out1            | Out2            | Notes                               |

|---------|-----------|-----|--------|-----------------|-----------------|-------------------------------------|

|         | Н         | L   | L      | VCC             | Floating        | Turns the power supply OFF.         |

| Stop    | L         | Н   | L      | Floating        | V <sub>CC</sub> | ENABLE must be set Low when         |

|         | Н         | Н   | L      | Floating        | Floating        | VDD is rising or falling.           |

| Forward | Ц         |     | Н      | VCC             | GND             | No input signal is needed that      |

| (CW)    | (CW) H    | L   | PWM    | V <sub>CC</sub> | PWM(F4)         | turns off the upper- and            |

| Reverse | Reverse , |     | Н      | GND             | V <sub>CC</sub> | lower-side drive devices when       |

| (CCW)   | L         | Н   | PWM    | PWM(F3)         | V <sub>CC</sub> | switching the rotational direction. |

|         | Н         | Н   | Н      | GND             | GND             | GND side MOSFET ON                  |

| Brake   | П         | П   | PWM    | L-PWM(F3)       | L-PWM(F4)       |                                     |

|         | L         | L   | L or H | VCC             | VCC             | Vcc side MOSFET ON                  |

#### Motor Drive Conditions (H: High-level input; L: Low-Level Input)

#### STK681-332

Output control is enabled by applying an external PWM signal to the ENABLE pin.

The product can run at a minimum external PWM pulse width of 1 $\mu$ s. In the case when the high pulse width is less than 16 $\mu$ s, however, the IC may fail to detect a short-circuit condition when an output short-circuit occurs.

If  $V_{DD}$  is turned off in the condition with the ENABLE pin set to high during motor rotation or PWM operation, the FAULT signal is output when  $V_{DD}$  is falling, indicating error condition. For this reason, ENABLE must be set to low when  $V_{DD}$  is rising or falling.

When both IN1 and IN2 are set low, the MOSFET on the V<sub>CC</sub> side is driven. To minimize the loss when stopped, set IN1 = IN2 = High and ENABLE = Low to turn off the gate signal to the V<sub>CC</sub> side MOSFETs.

#### STK681-352

Output control is enabled by applying an external PWM signal to the ENABLE pin.

The product can run at a minimum external PWM pulse width of 1 $\mu$ s. In the case when the high pulse width is less than 16 $\mu$ s, however, the IC may fail to detect a short-circuit condition when an output short-circuit occurs.

FAULT signal is generated to indicate an error condition if  $V_{CC}$  falls below the allowable operating range when the ENABLE pin is set to high during motor rotation or PWM operation. For this reason, ENABLE must be set to low when  $V_{CC}$  is rising or falling.

When both IN1 and IN2 are set low, the MOSFET on the  $V_{CC}$  side is driven. To minimize the loss when stopped, set IN1 = IN2 = High and ENABLE = Low to turn off the gate signal to the  $V_{CC}$  side MOSFETs.

Setting the current limit using the Vref pin

Output current peak(Iop)=(Vref÷4.9)÷Rs

"4.9" in the above formula indicates the portion of the Vref voltage that is divided using the circuit inside the control IC.

$Vref = (R2 \div (R1 + R2)) \times 5.0V(or 3.3V)$

Rs is the external current detection resistance value of the HIC, and Vref  $\leq$  2.0V must be satisfied so that overcurrent detection is not triggered.

Notes

- (1) Be sure to set the capacitance of the power supply bypass capacitor, C1, so that the ripple current of the capacitor, which varies as motor current increases, falls within the allowed range.

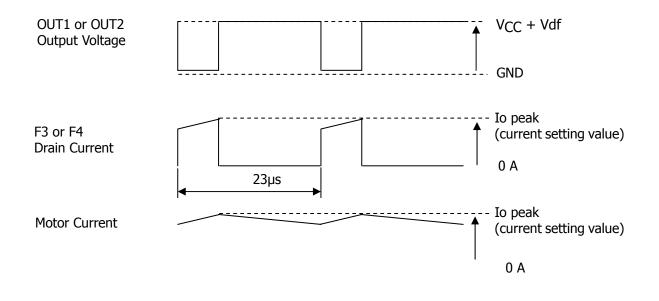

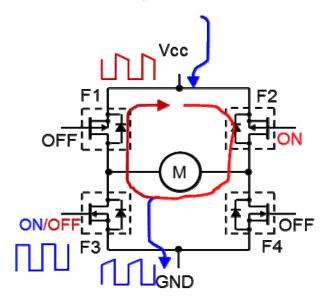

- (2) Chopping operations based on F3 and F4 are used for current control. The timing given below is used for OUT1 or OUT2 voltage output and for F3 or F4 drain current.

- (3) Do not connect the N.C pins (5, 11, 12 pin) shown in the internal block diagram or sample application circuit to a circuit pattern on the PCB.

- (4) If the current detection resistor, Rs, connected to pin1, pin2, and pin3 is short-circuited, the overcurrent detection circuit does not operate. If the output pin is short-circuited directly to V<sub>CC</sub> or connected directly to GND, an output short-circuit condition is detected and the output is latched in the off state. To restart the operation, turn on V<sub>DD</sub> again.

(In case of STK681-352-E, to restart the operation, turn on V<sub>CC</sub> again.)

(5) Smoke Emission Precautions: There is a possibility of smoke emission if the hybrid IC is subjected to physical or electrical damage as the result of being used without compliance with the specifications.

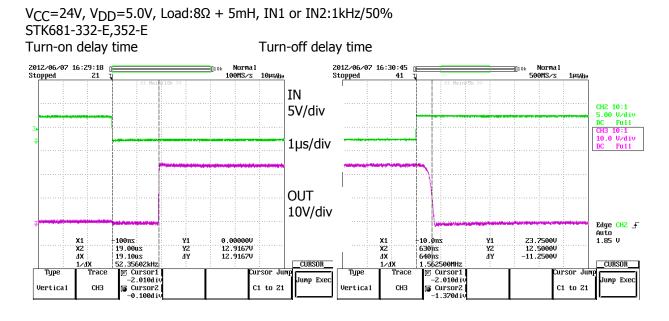

#### Delay time

**Substrate Specifications** (Substrate recommended for operation of STK681-332/352-E) Size: 100mm × 65mm × 1.6mm 1-layer board Material: Phenol

Copper side (35µ)

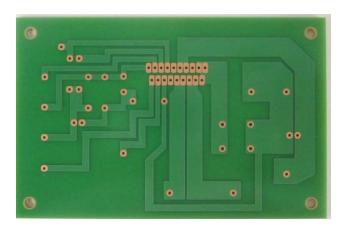

## Allowable power dissipation (Reference value)

If you need heat sink to STK681-332 and 352, mount heat sink with something such as clips.

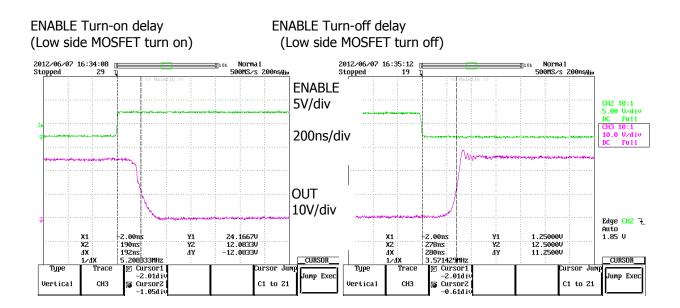

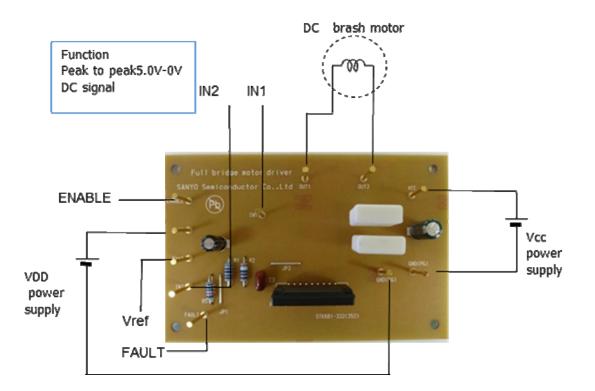

#### **Evaluation board**

STK681-332-E (100.0mm x 65.0mm x 1.6mm, phenol 1-layer board)

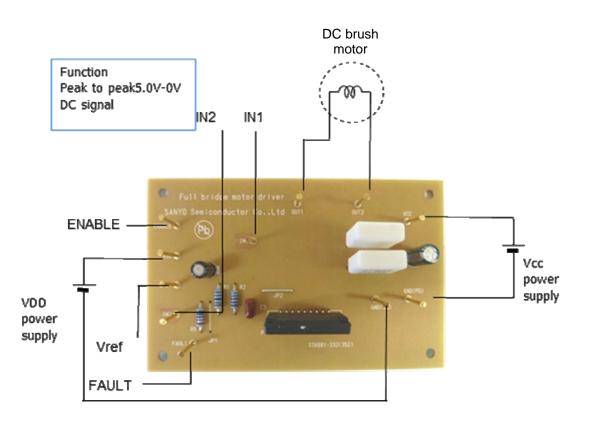

#### **Evaluation board**

STK681-352-E (100.0mm x 65.0mm x 1.6mm, phenol 1-layer board)

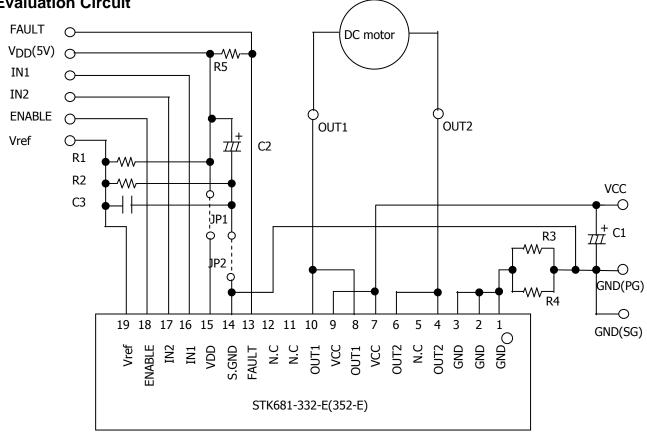

| Designator     | Quantity | Description                                | Value             | Tolerance | Footprint | Manufacturer           | Manufacturer<br>Part Number | Substitution<br>Allowed | Lead<br>Free |

|----------------|----------|--------------------------------------------|-------------------|-----------|-----------|------------------------|-----------------------------|-------------------------|--------------|

| C1             | 1        | V <sub>CC</sub> Bypass<br>Capacitor        | 47μF<br>/50V      | ±20%      |           | SUN<br>ERECTRONICS     | 50ME47CA                    | YES                     | YES          |

| C2             | 1        | V <sub>DD</sub> Bypass<br>Capacitor        | 10µF<br>/50V      | ±20%      |           | SUN<br>ERECTRONICS     | 50ME10CA                    | YES                     | YES          |

| C3             | 1        | Vref<br>stabilization<br>Capacitor         | 0.1µF<br>/50<br>V | ±10%      |           | Panasonic              | ECQV1H104JL2                | YES                     | YES          |

| R1             | 1        | Resistor to<br>set Vref                    |                   | ±1%       |           | AKAHANE<br>ERECTRONICS | RN14S****FK                 | YES                     | YES          |

| R2             | 1        | Resistor to<br>set Vref                    |                   | ±1%       |           | AKAHANE<br>ERECTRONICS | RN14S****FK                 | YES                     | YES          |

| R3, R4         | 2        | Output<br>current<br>detective<br>resistor | 0.1Ω              | ±5%       |           | КОА                    | BPR38CFR10J                 | YES                     | YES          |

| R5             | 1        | Pull-up<br>Resistor                        | 10<br>kΩ          | ±5%       |           | AKAHANE<br>ERECTRONICS | RN14S103JK                  | YES                     | YES          |

| HIC            | 1        | IPM                                        |                   |           |           | ON<br>Semiconductor    | STK681-332                  | NO                      | YES          |

| JP1, JP2       | 2        | Jumper for<br>STK681-332                   |                   |           |           | Mac-Eight              | JR-4                        | YES                     | YES          |

| JP2            | 1        | Jumper for<br>STK681-352                   |                   |           |           | Mac-Eight              | JR-4                        | YES                     | YES          |

| TP1 to<br>TP11 | 11       | Test Point                                 |                   |           |           | Mac-Eight              | ST-1-3                      | YES                     | YES          |

#### Bill of Materials for STK681-332/352-E Evaluation Board

Notes: R1 and R2 are used to Vref for current setting. Therefore their value do not mention on this table.

#### **Evaluation Circuit**

Notes: Open JP1 with STK681-352-E.

#### Waveform example

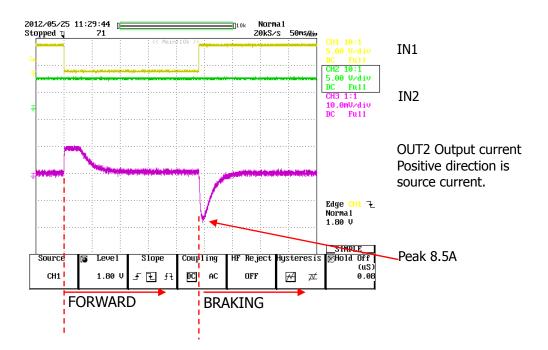

STK681-332(Current limit 5A setting) IN1 and IN2; 5V/div, Output current; 5A/div

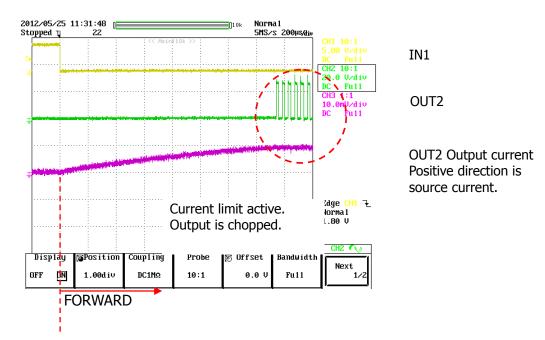

STK681-332(Current limit 5A setting) IN1 5V/div, OUT2 20V/div, Output current; 5A/div

Current control is slow decay.

STK681-332 and 352 control MOSFET at Low side by constant-current PWM control system. Current control enters Slow decay mode.

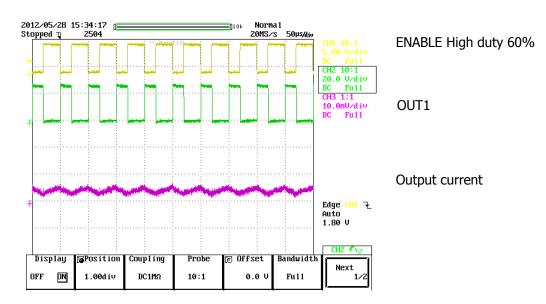

STK681-332 and 352 have ENABLE terminal built-in, which controls motor rotation. At the point of ENABLE=High, F3 or F4 at Low side turns on. STK681-332, 352(ENABLE: 20kHz) ENABLE; 5V/div, OUT1; 20V/div, Output current; 0.5A/div

#### **Evaluation Board Manual**

[Supply Voltage] V<sub>CC</sub> (10 to 38V: STK681-332-E): Power Supply for stepping motor V<sub>CC</sub> (10 to 29V: STK681-352-E): Power Supply for stepping motor

Vref (0 to 2.0V): Const. Current Control for Reference Voltage VDD (5V) : Power Supply for internal logic IC

[Operation Guide]

- 1. Motor Connection: Connect the motor to OUT1 and OUT2.

- 2. Initial Condition Setting: Set to signal condition IN1=H, IN2=H, and ENABLE=L.

- 3. Power Supply:

<STK681-332-E>

At first, supply DC voltage to V<sub>DD</sub> (5.0V), and VREF.

Next, supply DC voltage to V<sub>CC</sub>.

<STK681-352-E>

At first, supply DC voltage to V<sub>DD</sub> (3.3V or 5.0V), and VREF.

Next, supply DC voltage to V<sub>CC</sub>.

- 4. Set to Forward or Reverse signal condition with ENABLE=Low. Turn "High" ENABLE signal. Output current flows between OUT1 and OUT2.

- 5. Motor Operation

[Setting the current limit using the Vref pin]

```

Output current peak(Iop)=(Vref÷4.9)÷Rs

"4.9" in the above formula indicates the portion of the Vref voltage that is divided using

the circuit inside the control IC.

Vref=(R2÷(R1+R2))×5.0V(or 3.3V)

Rs is the external current detection resistance value of the HIC, and Vref ≤ 2.0V must

```

Rs is the external current detection resistance value of the HIC, and Vref  $\leq$  2.0V must be satisfied so that overcurrent detection is not triggered.

#### Notes in design

(1) Allowable operating range

Operation of this product assumes use within the allowable operating range. If a supply voltage or an input voltage outside the allowable operating range is applied, an overvoltage may damage the internal control IC or the MOSFET.

If a voltage application mode that exceeds the allowable operating range is anticipated, connect a fuse or take other measures to cut off power supply to the product.

(2)Input pins

If the input pins are connected directly to the PC board connectors, electrostatic discharge or other overvoltage outside the specified range may be applied from the connectors and may damage the product. Current generated by this overvoltage can be suppressed to effectively prevent damage by inserting  $100\Omega \cdot$  to  $1k\Omega \cdot$  resistors in lines connected to the input pins. Take measures such as inserting resistors in lines connected to the input pins.

(3) Power connectors (STK681-332-E)

If the motor power supply V<sub>CC</sub> is applied by mistake without connecting the GND part of the power connector when the product is operated, such as for test purposes, an overcurrent flows through the V<sub>CC</sub> decoupling capacitor, C1, to the parasitic diode between the V<sub>DD</sub> of the internal control IC and GND, and may damage the power supply pin block of the internal control IC. Always connect the GND pin before supplying V<sub>CC</sub>.

#### (4) Input Signal Lines

- 1) Do not use an IC socket to mount the driver, and instead solder the driver directly to the PC board to minimize fluctuations in the GND potential due to the influence of the resistance component and inductance component of the GND pattern wiring.

- 2) To reduce noise due to electromagnetic induction to small signal lines, do not design small signal lines (sensor signals, 5V or 3.3V power supply signal lines) that run parallel near the motor output lines OUT1 and OUT2.

- 3) Pins 5, 11 and 12 of this product are N.C pins. Do not connect any wiring to these pins.

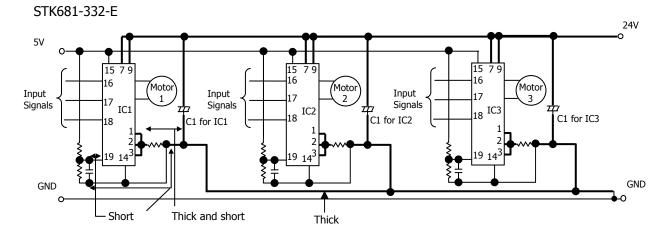

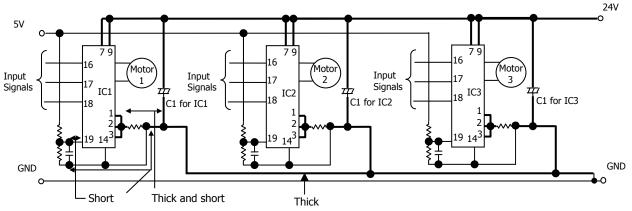

(5) When mounting multiple drivers on a single PC board When mounting multiple drivers on a single PC board, the GND design should mount a V<sub>CC</sub> decoupling capacitor, C1, for each driver to stabilize the GND potential of the other drivers. The key wiring points are as follows.

STK681-352-E

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture o