# Linear Regulator - Wide Input Voltage Range, Ultra-Low Iq, High PSRR, Adjustable Output Voltage

# 10 mA

The NCP786A is high-performance linear regulator, offering a very wide operating input voltage range of up to 450 V DC, with an output current of up to 10 mA. Ideal for high input voltage applications such as industrial and home metering, home appliances. The NCP786A family offers  $\pm 3\%$  initial accuracy, extremely high-power supply rejection ratio and ultra-low quiescent current. The NCP786A family is optimized for high-voltage line and load transients, making them ideal for harsh environment applications. The output voltage can be set by resistor divider in range from 1.27 V up to 15 V. DFN6 5x6 Pb-free package with high allowable power dissipation keep small footprint at space sensitive applications.

### **Features**

• Wide Input Voltage Range:

DC: Up to 450 V

AC: 85 V to 260 V (half-wave rectifier and 4.7 μF capacitor)

- 10 mA Guaranteed Output Current

- Ultra Low Quiescent Current: Typ. 10  $\mu$ A ( $V_{OUT} \le 15 \text{ V}$ )

- ±5% Accuracy Over Full Load, Line and Temperature Variations

- Ultra-high PSRR: 70 dB at 60 Hz, 90 dB at 100 kHz

- Stable with Ceramic Output Capacitor 2.2 µF MLCC

- Thermal Shutdown and Current Limit Protection

- Available in DFN6 5x6 Package

- This is a Pb-Free Device

# **Typical Applications**

- Industrial Applications, Home Appliances

- Home Metering / Network Application

- Off-line Power Supplies

# ON Semiconductor®

www.onsemi.com

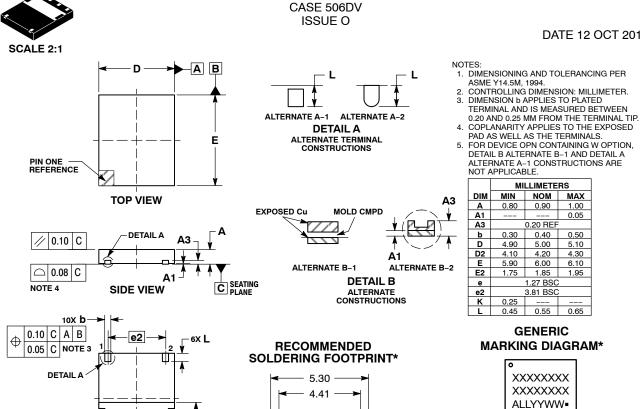

# MARKING DIAGRAM

DFN6 5x6 ST SUFFIX CASE 506DV

(Top View)

786A = Specific Device Marking

XXX = Voltage Version (see page 7)

A = Assembly Location

LL = Wafer Lot

YY = Year

WW = Work Week

= Pb-Free Package(Note: Microdot may be in either location)

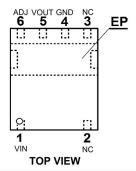

# **PIN CONNECTIONS**

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.

1

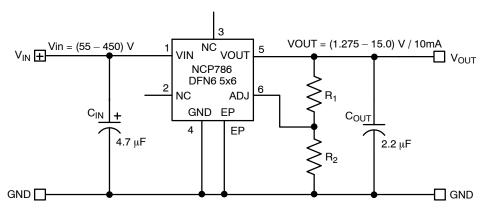

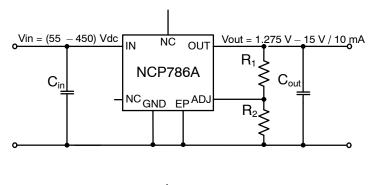

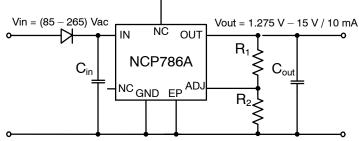

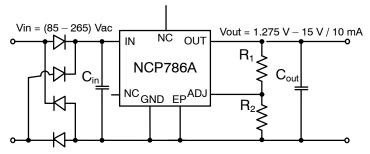

Figure 1. Typical Applications

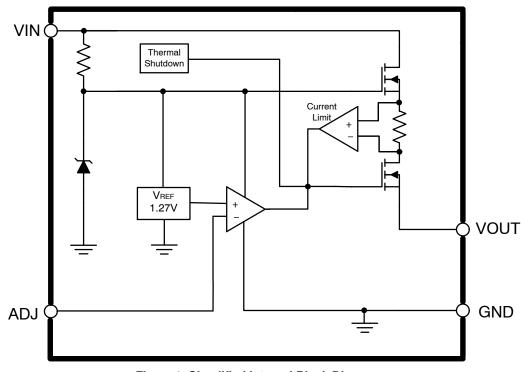

Figure 2. Simplified Internal Block Diagram

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name | Description                                                                 |  |  |

|---------|----------|-----------------------------------------------------------------------------|--|--|

| 1       | VIN      | Supply Voltage Input. Connect 4.7 μF capacitor from VIN to GND.             |  |  |

| 2       | NC       | Not connected.                                                              |  |  |

| 3       | NC       | Not connected.                                                              |  |  |

| 4       | GND      | Ground connection.                                                          |  |  |

| 5       | VOUT     | Regulator Output. Connect 2.2 μF or higher MLCC capacitor from VOUT to GND. |  |  |

| 6       | ADJ      | ADJ pin for output voltage setting via resistors divider.                   |  |  |

| EP      | EP       | EP should be connected to GND potential.                                    |  |  |

Table 2. ABSOLUTE MAXIMUM RATINGS

| Rating                       | Symbol           | Value       | Unit |

|------------------------------|------------------|-------------|------|

| Input Voltage (Note 1)       | V <sub>IN</sub>  | -0.3 to 700 | V    |

| Output Voltage               | V <sub>OUT</sub> | -0.3 to 18  | V    |

| Maximum Junction Temperature | $T_{J(MAX)}$     | 125         | °C   |

# **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                                                     | T <sub>STG</sub>   | -55 to 150 | °C |

|-------------------------------------------------------------------------|--------------------|------------|----|

| ESD Capability, Human Body Model (All pins except HV pin no.1) (Note 2) | ESD <sub>HBM</sub> | 2000       | ٧  |

| ESD Capability, Machine Model (Note 2)                                  | ESD <sub>MM</sub>  | 200        | V  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Peak 650 V max 1 ms non repeated for 1 s

- 2. This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latch-up Current Maximum Rating tested per JEDEC standard: JESD78.

# **Table 3. THERMAL CHARACTERISTICS**

| Rating                                                                                                | Symbol        | Value | Unit |

|-------------------------------------------------------------------------------------------------------|---------------|-------|------|

| Thermal Characteristics, DFN6 Thermal Resistance, Junction-to-Air JEDEC 51.3, One side, 600 sq mm PCB | $R_{	hetaJA}$ | 82    | °C/W |

**Table 4. ELECTRICAL CHARACTERISTICS NCP786A Adj.** ( $-40^{\circ}C \le T_J \le 85^{\circ}C$ ;  $V_{IN} = 340$  V;  $I_{OUT} = 100$  μA,  $C_{IN} = 4.7$  μF,  $C_{OUT} = 10$  μF, unless otherwise noted. Typical values are at  $T_J = +25^{\circ}C$ .) (Note 3)

| Parameter                             | Test Conditions                                                                                                              |                                                | Symbol              | Min  | Тур   | Max  | Unit  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------|------|-------|------|-------|

| Operating Input Voltage DC            |                                                                                                                              |                                                | V <sub>IN</sub>     | 55   |       | 450  | V     |

| Maximum output voltage                | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}$ , lout = 100 $\mu\text{A}$ , 55 V $\le$ Vin $\le$ 450 V |                                                | Voutmax             |      | 15    |      | V     |

| Reference Voltage Accuracy            | rence Voltage Accuracy $T_J = 25^{\circ}C$ , lout = 100 $\mu$ A, 55 V $\leq$ Vin $\leq$ 450 V                                |                                                | $V_{REF}$           | -3%  | 1.275 | +3%  | V     |

|                                       | $-40^{\circ}C \le T_{J} \le 85^{\circ}C$ , lout = 100 $\mu$ A, 55 $V \le V$ in $\le 450 \ V$                                 |                                                | V <sub>REF</sub>    | -5%  | 1.275 | +5%  | V     |

| Line Regulation                       | V <sub>IN</sub> = 55 V to 450 V, lout = 100 μA                                                                               | V <sub>IN</sub> = 55 V to 450 V, lout = 100 μA |                     | -0.5 | 0.1   | +0.5 | %     |

| Load Regulation                       | I <sub>OUT</sub> = 100 μA to 10 mA, Vin = 55 V                                                                               |                                                | Reg <sub>LOAD</sub> | -1.0 | 0.7   | +1.0 | %     |

| Maximum Output Current                | 55 V ≤ Vin ≤ 450 V, (Note 4)                                                                                                 |                                                | I <sub>OUT</sub>    | 11   |       |      | mA    |

| Quiescent Current                     | I <sub>OUT</sub> = 0, 55 V ≤ Vin ≤ 450 V                                                                                     |                                                | I <sub>GND</sub>    |      | 10    | 15   | μΑ    |

| Ground current                        | 55 V ≤ Vin ≤ 450 V, (Note 4)<br>0 < I <sub>OUT</sub> ≤ 10 mA                                                                 |                                                |                     |      |       | 25   | μΑ    |

| ADJ Pin current                       |                                                                                                                              |                                                |                     |      | 150   |      | nA    |

| Power Supply Rejection Ratio          | Vin = 340 VDC +1 Vpp modulation,<br>lout = 100 μA                                                                            | f = 1 kHz                                      | PSRR                |      | 65    |      | dB    |

| Noise                                 | $f$ = 10 kHz to 1 MHz Vin = 340 VDC, lout = 1 mA, $C_{OUT}$ = 10 $\mu F$                                                     |                                                | V <sub>NOISE</sub>  |      | 150   |      | μVrms |

| Thermal Shutdown Temperature (Note 5) | Temperature increasing from T <sub>J</sub> = +25°C                                                                           |                                                | T <sub>SD</sub>     |      | 145   |      | °C    |

| Thermal Shutdown Hysteresis (Note 5)  | Temperature falling from T <sub>SD</sub>                                                                                     |                                                | T <sub>SDH</sub>    | -    | 10    | -    | °C    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>3.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization production tested at T<sub>J</sub> = T<sub>A</sub> = 25°C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

<sup>4.</sup> Respect to Safe Operating Area

<sup>5.</sup> Guaranteed by design

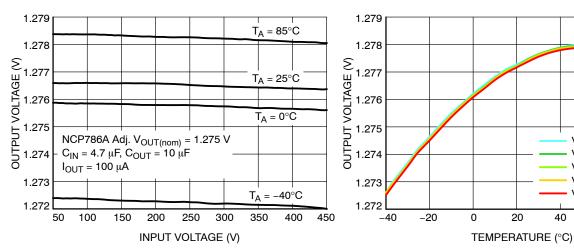

# **TYPICAL CHARACTERISTICS**

Figure 3. Output Voltage vs. Input Voltage

Figure 4. Output Voltage vs. Temperature

$V_{IN} = 55 V$

$V_{IN} = 150 \text{ V}$

$V_{IN} = 250 \text{ V}$  $V_{IN} = 350 \text{ V}$

$V_{IN} = 450 \text{ V}$

40

60

8

80

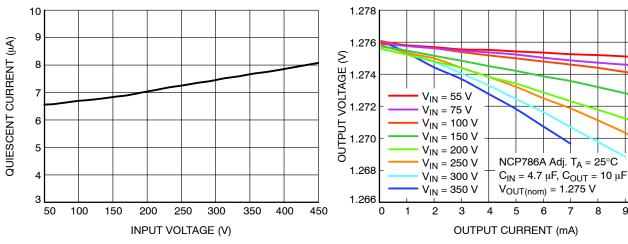

Figure 5. Quiescent Current vs. Input Voltage

25 20 NOISE DENSITY (μV√Hz) 15 10 5 0.1 1000 0.01 FREQUENCY (kHz)

Figure 7. Noise Density vs. Frequency

Figure 6. Output Voltage vs. Output Current

# **APPLICATION INFORMATION**

Figure 8. Typical Application Schematics

### Input Decoupling (C1)

A 4.7  $\mu F$  capacitor either ceramic or electrolytic is recommended and should be connected close to the input pin of NCP786A. Higher value 4.7  $\mu F$  is necessary to keep the input voltage above the required minimum input voltage at full load for AC voltage as low as 85 V with half wave rectifier. The capacitor 2.2  $\mu F$  or 1  $\mu F$  could be acceptable for DC input voltage or AC input voltage 235 V  $\pm 20\%$ . There must be assured minimum Input Voltage more than 55 V at input pin of NCP786A regulator in order to keep stable desired output voltage with guaranteed parameters.

# **Output Decoupling (C2)**

The NCP786A Regulator does not require any specific Equivalent Series Resistance (ESR). Thus capacitors exhibiting ESRs ranging from a few m $\Omega$  up to 0.5  $\Omega$  can be used safely. The minimum decoupling value is 2.2  $\mu$ F. The regulator accepts ceramic chip capacitors as well as tantalum devices or low ESR electrolytic capacitors. Larger values improve noise rejection and especially load transient response.

# **Layout Recommendations**

Please be sure that the  $V_{IN}$  and GND lines are sufficiently wide. When the impedance of these lines is high, there is a chance to pick up noise or to cause the malfunction of regulator.

Set external components, especially the output capacitor, as close as possible to the circuit, and make leads as short as possible.

### **Thermal**

As power across the NCP786A increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design layout and used package. Mounting pad configuration on the PCB, the board material, and also the ambient temperature affect the rate of temperature rise for the part. This is stating that when the NCP786A has good thermal conductivity through the PCB, the junction temperature will be relatively low with high power dissipation applications.

# **Output Voltage**

The output voltage can be set by using a resistor divider as shown in Figure 1 in range from 1.275 V up to 15 V. The appropriate resistor divider can be found by solving the equation below.

$$V_{OUT} = 1.275 \times \left(1 + \frac{R1}{R2}\right) + \left(I_{ADJ} \times R1\right) \;\; \text{(eq. 1)}$$

The recommended current through the resistor divider is from 1  $\mu A$  to 3  $\mu A$  in order to keep negligible ADJ pin consumption. In this case we can simplify Equation 1 to:

$$V_{OUT} = 1.275 \times \left(1 + \frac{R1}{R2}\right)$$

(eq. 2)

# **ORDERING INFORMATION**

| Part Number     | Output Voltage | Marking | Package               | Shipping <sup>†</sup> |

|-----------------|----------------|---------|-----------------------|-----------------------|

| NCP786AMNADJTBG | Adjustable     | ADJ     | DFN6 5x6<br>(Pb–Free) | 1000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

**DATE 12 OCT 2016**

E2

D2

**BOTTOM VIEW**

6X 0.60

0.20

6

DFN6 5x6, 1.27P

### 1.27 BSC 3.81 BS0

1.00

0.05

0.50

5.10

4.30

6.10

1.95

0.65

# **GENERIC MARKING DIAGRAM\***

= Assembly Location

= Wafer Lot

= Year

1.27 PITCH

6.30

0.75

**DIMENSIONS: MILLIMETERS**

WW = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

3.81

PITCH

| DOCUMENT NUMBER: | 98AON16235G     | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | DFN6 5X6, 1.27P |                                                                                                                                                                                    | PAGE 1 OF 1 |  |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales