## Dual CAN FD Transceiver, High Speed, Low Power

# NCV7446

#### Description

NCV7446 is a dual CAN FD physical layer transceiver. It allows interfacing of two independent CAN physical buses and two independent CAN protocol controllers. The transceivers provide differential transmit capability to the bus and differential receive capability to the CAN controllers.

It is consisted of two fully independent NCV7344 transceivers. The NCV7446 guarantees additional timing parameters to ensure robust communication at data rates beyond 1 Mbps to cope with CAN flexible data rate requirements (CAN FD). These features make the NCV7446 an excellent choice for all types of HS–CAN networks, in nodes that require a low–power mode with wake–up capability via the CAN bus.

#### Features

- Compliant with the ISO 11898–2:2016

- CAN FD Timing Specified up to 5 Mbps

- Very Low Current Standby Mode with Wake-up via the Bus

- Low Electromagnetic Emission (EME) and High Electromagnetic Immunity

- No Disturbance of the Bus Lines with an Un-powered Node

- Transmit Data (TxD) Dominant Timeout Function

- Under All Supply Conditions the Chip Behaves Predictably

- Very High ESD Robustness of Bus Pins

- Thermal Protection

- Bus Pins Short Circuit Proof to Supply Voltage and Ground

- Bus Pins Protected Against Transients in an Automotive Environment

#### Quality

- Wettable Flank Package for Enhanced Optical Inspection

- AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- Automotive

- Industrial Networks

### **ON Semiconductor®**

www.onsemi.com

#### MARKING DIAGRAM

NV7446-0 = Specific Device Code

= Assembly Site

A L

Y

W

- = Wafer Lot

- = Year of Production, Last Number

- = Work Week Number

- = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

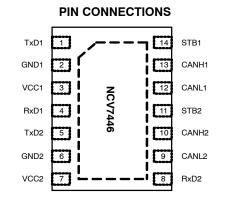

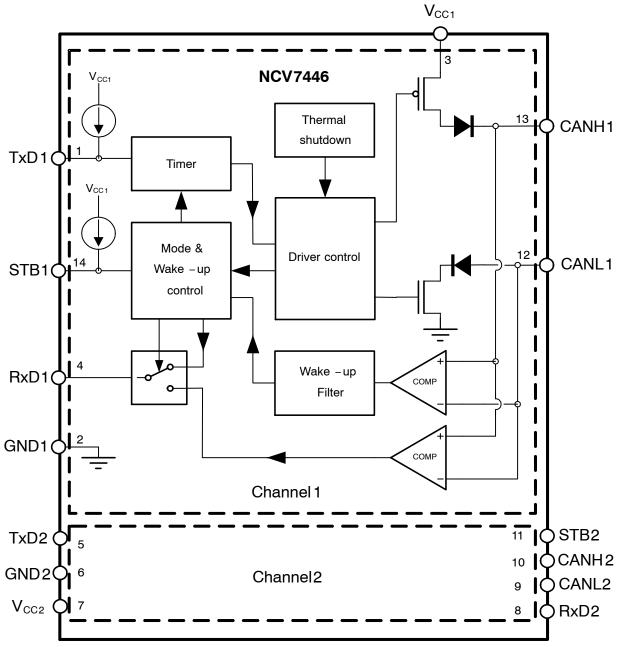

Figure 1. NCV7446 Block Diagram

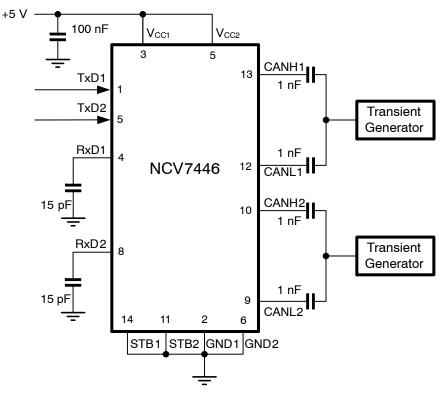

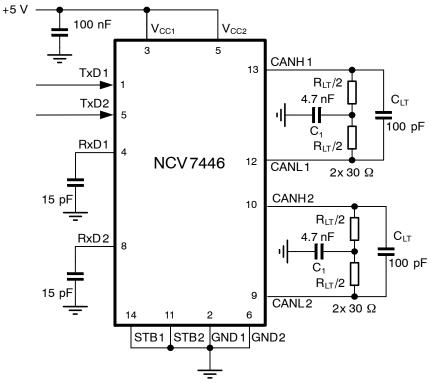

#### **TYPICAL APPLICATION DIAGRAM**

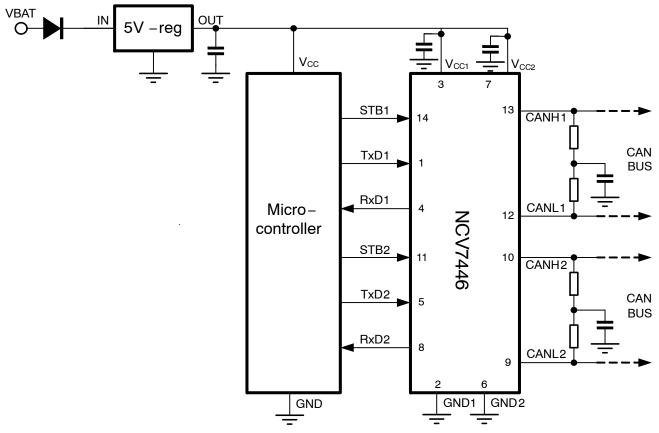

Figure 2. NCV7446 Application Diagram

| Table 1. | PIN F | UNCTION | DESCRIP | TION |

|----------|-------|---------|---------|------|

|----------|-------|---------|---------|------|

| Pin Number | Pin Name         | Description                                                                                          |

|------------|------------------|------------------------------------------------------------------------------------------------------|

| 1          | TxD1             | Transmit data input for channel 1; low input $\rightarrow$ dominant driver; internal pull-up current |

| 2          | GND1             | Ground for channel 1                                                                                 |

| 3          | V <sub>CC1</sub> | Supply voltage for channel 1                                                                         |

| 4          | RxD1             | Receive data output for channel 1; dominant transmitter $\rightarrow$ low output                     |

| 5          | TxD2             | Transmit data input for channel 2; low input $\rightarrow$ dominant driver; internal pull-up current |

| 6          | GND2             | Ground for channel 2                                                                                 |

| 7          | V <sub>CC2</sub> | Supply voltage for channel 2                                                                         |

| 8          | RxD2             | Receive data output for channel 2; dominant transmitter $\rightarrow$ low output                     |

| 9          | CANL2            | Low-level CAN bus line channel 2 (low in dominant mode)                                              |

| 10         | CANH2            | High-level CAN bus line channel 2 (high in dominant mode)                                            |

| 11         | STB2             | Standby mode control input for channel 2; internal pull-up current                                   |

| 12         | CANL1            | Low-level CAN bus line channel 1 (low in dominant mode)                                              |

| 13         | CANH1            | High-level CAN bus line channel 1 (high in dominant mode)                                            |

| 14         | STB1             | Standby mode control input for channel 1; internal pull-up current                                   |

| EP         | Exposed Pad      | Recommended to connect to GND or left floating in application                                        |

#### FUNCTIONAL DESCRIPTION

#### **Operating Modes**

NCV7446 provides two modes of operation per transceiver as illustrated in Table 2. These modes are selectable through pins STB1 and STB2 independently for each transceiver.

#### **Table 2. OPERATING MODES**

| Pins<br>STBx | Mode    | Pins RxDx                                   |                                               |  |  |

|--------------|---------|---------------------------------------------|-----------------------------------------------|--|--|

| Low          | Normal  | Low when bus<br>dominant                    | High when bus recessive                       |  |  |

| High         | Standby | Follows the bus<br>when wake-up<br>detected | High when no<br>wake–up re-<br>quest detected |  |  |

#### **Normal Mode**

In the normal mode, the selected transceiver is able to communicate via the bus lines. The signals are transmitted and received to the CAN controller via the pins TxDx and RxDx. The slopes on the bus lines outputs are optimized to give low EME.

#### Standby Mode

In standby mode both the transmitter and receiver are disabled and a very low-power differential receiver monitors the bus lines for CAN bus activity. The bus lines are biased to ground and supply current is reduced to a minimum. When a wake-up request is detected by the low-power differential receiver, the signal is first filtered and then verified as a valid wake signal after a time period of twake\_filt, the corresponding RxDx pin is driven low by the transceiver (following the bus) to inform the controller of the wake-up request.

#### Wake-up

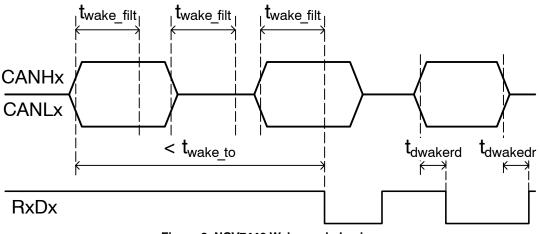

When a valid wake-up pattern (phase in order dominant – recessive – dominant) is detected during the standby mode the RxDx pins follows the bus. Minimum length of each phase is  $t_{wake filt}$  – see Figure 3.

Pattern must be received within t<sub>wake\_to</sub> to be recognized as valid wake-up otherwise internal logic is reset.

Figure 3. NCV7446 Wake-up behavior

#### **Overtemperature Detection**

A thermal protection circuit protects the IC from damage by switching off the affected transmitter if the junction temperature exceeds a value of approximately 170°C. Because the transmitter dissipates most of the power, the power dissipation and temperature of the IC is reduced. All other IC functions continue to operate. The transmitter off–state resets when the temperature decreases below the shutdown threshold and pins TxDx goes high. The thermal protection circuit is particularly needed when a bus line short circuits.

#### **TxDx Dominant Timeout Function**

A TxD dominant timeout timer circuit prevents the bus lines being driven to a permanent dominant state (blocking all network communication) if pins TxDx are forced permanently low by a hardware and/or software application failure. The timer is triggered by a negative edge on pins TxDx. If the duration of the low–level on pins TxDx exceeds the internal timer value  $t_{dom(TxD)}$ , the transmitter is disabled, driving the bus into a recessive state. The timer is reset by a positive edge on pins TxDx. This TxD dominant timeout time  $t_{dom(TxD)}$  defines the minimum possible bit rate to 17 kbps.

#### Fail Safe Features

A current–limiting circuit protects the transmitter output stage from damage caused by accidental short circuit to either positive or negative supply voltage, although power dissipation increases during this fault condition.

Undervoltage on  $V_{CC1}$  or  $V_{CC2}$  pins prevents the chip sending data on the bus when there is not enough  $V_{CC}$  supply voltage.

After supply is recovered, corresponding TxD pin must be first released to high to allow sending dominant bits again. Recovery time from undervoltage detection is equal to td(stb-nm) time.

The pins CANHx and CANLx are protected from automotive electrical transients (according to ISO 7637; see Figure 5). Pins TxDx and STBx are pulled high internally should the input become disconnected. Pins TxDx, STBx and RxDx will be floating, preventing reverse supply should the adjacent VCCx supply be removed.

#### **ELECTRICAL CHARACTERISTICS**

#### Definitions

All voltages are referenced to GNDx (pin 2 or pin 6). Positive currents flow into the IC. Sinking current means the current is flowing into the pin; sourcing current means the current is flowing out of the pin.

#### Table 3. ABSOLUTE MAXIMUM RATINGS

| Symbol                 | Parameter                                                      | Conditions                                   | Min  | Max                    | Unit |

|------------------------|----------------------------------------------------------------|----------------------------------------------|------|------------------------|------|

| V <sub>SUP</sub>       | Supply voltage V <sub>CC1</sub> , V <sub>CC2</sub>             |                                              | -0.3 | +6                     | V    |

| V <sub>CANH</sub>      | DC voltage at pins CANHx                                       | 0 < V <sub>CCX</sub> < 5.25 V; no time limit | -42  | +42                    | V    |

| V <sub>CANL</sub>      | DC voltage at pins CANLx                                       | 0 < V <sub>CCX</sub> < 5.25 V; no time limit | -42  | +42                    | V    |

| V <sub>CANH-CANL</sub> | DC voltage between any two pins<br>(including CANHx and CANLx) |                                              | -42  | +42                    | V    |

| V <sub>IN</sub>        | DC Voltage at pins TxDx, STBx                                  |                                              | -0.3 | +6                     | V    |

| V <sub>OUT</sub>       | DC Voltage at pin RxDx                                         |                                              | -0.3 | V <sub>CCx</sub> + 0.3 | V    |

| V <sub>esdHBM</sub>    | Electrostatic discharge voltage at all pins,<br>Component HBM  | (Note 1)                                     | -8   | +8                     | kV   |

| V <sub>esdCDM</sub>    | Electrostatic discharge voltage at all pins,<br>Component CDM  | (Note 2)                                     | -750 | +750                   | V    |

| V <sub>esdIEC</sub>    | Electrostatic discharge voltage at pins CANHx                  | Without bus filter (Note 3)                  | -7   | +7                     | kV   |

|                        | and CANLx, System HBM (Note 4)                                 | With bus filter (Note 3)                     | -11  | +11                    | kV   |

| V <sub>schaff</sub>    | Voltage transients, pins CANHx, CANLx.                         | test pulses 1                                | -100 |                        | V    |

|                        | According to ISO7637-3, Class C (Note 4)                       | test pulses 2a                               |      | +75                    | V    |

|                        |                                                                | test pulses 3a                               | -150 |                        | V    |

|                        |                                                                | test pulses 3b                               |      | +100                   | V    |

| Latch-up               | Static latch-up at all pins                                    | (Note 5)                                     |      | 150                    | mA   |

| T <sub>stg</sub>       | Storage temperature                                            |                                              | -55  | +150                   | °C   |

| ТJ                     | Maximum junction temperature                                   |                                              | -40  | +170                   | °C   |

| MSL                    | Moisture Sensitivity Level                                     |                                              |      | 1                      | -    |

| T <sub>SLD</sub>       | Lead temperature Soldering - Reflow (Note 11)                  |                                              | -    | 260                    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Standardized human body model electrostatic discharge (ESD) pulses in accordance to EIA-JESD22. Equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  resistor.

Standardized charged device model ESD pulses when tested according to AEC-Q100-011.

3. System human body model electrostatic discharge (ESD) pulses in accordance to IEC 61000-4-2. Equivalent to discharging a 150 pF capacitor through a 330  $\Omega$  resistor referenced to GNDx.

Results were verified by external test house.

5. Static latch-up immunity: Static latch-up protection level when tested according to EIA/JESD78.

6. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

#### **Table 4. THERMAL CHARACTERISTICS**

| Symbol            | Parameter                                          | Conditions          | Value | Unit |

|-------------------|----------------------------------------------------|---------------------|-------|------|

| $R_{\theta JA_1}$ | Thermal Resistance Junction-to-Air, JEDEC 1S0P PCB | Free air; (Note 8)  | 101   | K/W  |

| $R_{\theta JA_2}$ | Thermal Resistance Junction-to-Air, JEDEC 2S2P PCB | Free air; (Note 9)  | 53    | K/W  |

| $R_{\theta JA_3}$ | Thermal Resistance Junction-to-Air                 | Free air; (Note 10) | 76    | K/W  |

| $R_{\theta JA_4}$ | Thermal Resistance Junction-to-Air                 | Free air; (Note 11) | 46    | K/W  |

7. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

8

Test board according to EIA/JEDEC Standard JESD51–3, signal layer with 10% trace coverage. Test board according to EIA/JEDEC Standard JESD51–7, signal layers with 10% trace coverage. 9

10. Test board according to EIA/JEDEC Standard JESD51-3 and JESD51-5, signal layer with 10% trace coverage and with thermal via array under the exposed pad connected to the second copper layer.

11. Test board according to EIA/JEDEC Standard JESD51-5 and JESD51-7, signal layers with 10% trace coverage and thermal via array under the exposed pad connected to the first inner copper layer.

Table 5. ELECTRICAL CHARACTERISTICS  $V_{CC1}$ ,  $V_{CC2}$  = 4.75 V to 5.25 V;  $T_J$  = -40°C to +150°C;  $R_{LT}$  = 60  $\Omega$ ,  $C_{LT}$  = 100 pF,  $C_1$  not used,  $C_{RxD}$  = 15 pF, unless specified otherwise.

| Symbol                       | Parameter                                            | Conditions                                                                                                                               | Min  | Тур  | Max  | Unit |

|------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY (PINS                 | V <sub>ccx</sub> )                                   |                                                                                                                                          |      |      |      |      |

| V <sub>CCx</sub>             | Power supply voltage                                 | (Note 12)                                                                                                                                | 4.75 | 5.0  | 5.25 | V    |

| I <sub>CCx</sub>             | Supply current on single channel                     | Dominant; V <sub>TxDx</sub> = Low                                                                                                        | 20   | 45   | 55   | mA   |

|                              |                                                      | Recessive; V <sub>TxDx</sub> = Low                                                                                                       | 1.9  | 5.0  | 10   | mA   |

|                              |                                                      | Normal mode, Dominant;<br>$V_{TxDx} = 0$ V; one of bus wires<br>shorted; -3 V $\leq$ (V <sub>CANHx</sub> ,<br>$V_{CANLx}$ ) $\leq$ +18 V | 2.0  | _    | 105  | mA   |

| I <sub>CCSx</sub>            | Supply current in standby mode on<br>single channel  | $T_J \le 100^{\circ}C$ , (Note 13)                                                                                                       | -    | 10   | 15   | μΑ   |

| VUVD(VCC)(stby)              | Standby undervoltage detection $V_{CCx}$ pins        |                                                                                                                                          | 3.5  | 4.0  | 4.3  | V    |

| V <sub>UVD(VCC)(swoff)</sub> | Switch-off undervoltage detection $V_{CCx}$ pins     |                                                                                                                                          | 2.0  | 2.3  | 2.6  | V    |

| TRANSMITTER                  | DATA INPUT (Pins TxDx)                               |                                                                                                                                          |      |      |      |      |

| VIH                          | High-level input voltage                             | Output recessive                                                                                                                         | 2.0  | -    | -    | V    |

| VIL                          | Low-level input voltage                              | Output dominant                                                                                                                          | -    | -    | +0.8 | V    |

| I <sub>IH</sub>              | High-level input current                             | V <sub>TxDx</sub> = V <sub>CCx</sub>                                                                                                     | -5.0 | 0    | +5.0 | μA   |

| I <sub>IL</sub>              | Low-level input current                              | V <sub>TxDx</sub> = 0 V                                                                                                                  | -300 | -150 | -70  | μA   |

| Ci                           | Input capacitance                                    | (Note 13)                                                                                                                                | -    | 5    | 10   | pF   |

| TRANSMITTER                  | MODE SELECT (Pins STBx)                              |                                                                                                                                          |      |      |      |      |

| VIH                          | High-level input voltage                             | Standby mode                                                                                                                             | 2.0  | -    | -    | V    |

| VIL                          | Low-level input voltage                              | Normal mode                                                                                                                              | -    | -    | +0.8 | V    |

| I <sub>IH</sub>              | High-level input current                             | V <sub>STBx</sub> = V <sub>CCx</sub>                                                                                                     | -1.0 | 0    | +1.0 | μA   |

| I <sub>IL</sub>              | Low-level input current                              | V <sub>STBx</sub> = 0 V                                                                                                                  | -15  | -    | -1.0 | μA   |

| Ci                           | Input capacitance                                    | (Note 13)                                                                                                                                | -    | 5    | 10   | pF   |

| RECEIVER DAT                 | A OUTPUT (Pins RxDx)                                 |                                                                                                                                          |      |      |      |      |

| I <sub>ОН</sub>              | High-level output current                            | Normal mode<br>V <sub>RxDx</sub> = V <sub>CCx</sub> – 0.4 V                                                                              | -8.0 | -3.0 | -1.0 | mA   |

| I <sub>OL</sub>              | Low-level output current                             | $V_{RxDx} = 0.4 V$                                                                                                                       | 1.0  | 6.0  | 12   | mA   |

| BUS LINES (Pir               | ns CANHx and CANLx)                                  |                                                                                                                                          |      |      |      |      |

| I <sub>o(rec)</sub>          | Recessive output current at pins<br>CANHx and CANLx  | –27 V < V <sub>CANHx</sub> , V <sub>CANLx</sub> <<br>+32 V; Normal mode                                                                  | -5.0 | -    | +5.0 | mA   |

| ILI                          | Input leakage current                                | 0 $\Omega$ < R(V <sub>CCx</sub> to GNDx) < 1 MΩ; V <sub>CANLx</sub> = V <sub>CANHx</sub> = 5 V                                           | -5.0 | 0    | +5.0 | μΑ   |

| V <sub>o(rec)</sub> (CANH)   | Recessive output voltage at pins CANHx               | Normal mode, $V_{TxDx} = High;$<br>$R_{LT}$ and $C_{LT}$ not used                                                                        | 2.0  | 2.5  | 3.0  | V    |

| V <sub>o(rec)</sub> (CANL)   | Recessive output voltage at pins CANLx               | Normal mode, $V_{TxDx}$ = High;<br>R <sub>LT</sub> and C <sub>LT</sub> not used                                                          | 2.0  | 2.5  | 3.0  | V    |

| V <sub>o(off)(CANH)</sub>    | Recessive output voltage at pin CANHx                | Standby mode; ${\rm R}_{\rm LT}$ and ${\rm C}_{\rm LT}$ not used                                                                         | -0.1 | _    | +0.1 | V    |

| $V_{o(off)(CANL)}$           | Recessive output voltage at pin CANLx                | Standby mode; $\rm R_{LT}$ and $\rm C_{LT}$ not used                                                                                     | -0.1 | _    | +0.1 | V    |

| $V_{o(off)(CANL)}$           | Differential bus output voltage<br>(VCANHx - VCANLx) | Standby mode; $R_{LT}$ and $C_{LT}$ not used                                                                                             | -0.2 | _    | +0.2 | V    |

| V <sub>o(dom)(CANH)</sub>    | Dominant output voltage at pins CANHx                | $\label{eq:VTxDx} \begin{array}{l} V_{TxDx} = 0 \; V; \; t < tdom(TxD); \\ 50 \; \Omega < R_{LT} < 65 \; \Omega \end{array}$             | 2.75 | 3.5  | 4.5  | V    |

| V <sub>o(dom)(CANL)</sub>    | Dominant output voltage at pins CANLx                | $V_{TxDx} = 0 \text{ V; } t < tdom(TxD);$<br>50 $\Omega < R_{LT} < 65 \Omega$                                                            | 0.5  | 1.5  | 2.25 | V    |

$\label{eq:cc1} \begin{array}{l} \textbf{Table 5. ELECTRICAL CHARACTERISTICS} \\ \textbf{V}_{CC1}, \textbf{V}_{CC2} = 4.75 \text{ V to 5.25 V}; \ \textbf{T}_J = -40^{\circ}\text{C to } +150^{\circ}\text{C}; \ \textbf{R}_{LT} = 60 \ \Omega, \ \textbf{C}_{LT} = 100 \ \textbf{pF}, \ \textbf{C}_1 \ \textbf{not used}, \ \textbf{C}_{RxD} = 15 \ \textbf{pF}, \ \textbf{unless specified otherwise}. \end{array}$

| Symbol                          | Parameter                                                                      | Conditions                                                                                                                                         | Min  | Тур  | Max  | Unit |

|---------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| BUS LINES (Pin                  | s CANHx and CANLx)                                                             |                                                                                                                                                    |      |      |      | -    |

| V <sub>o(dom)(diff)</sub>       | Differential bus output voltage<br>(V <sub>CANHx</sub> – V <sub>CANLx</sub> )  | $V_{TxDx}$ = 0 V; dominant;<br>45 $\Omega$ < R <sub>LT</sub> < 65 $\Omega$                                                                         | 1.5  | 2.25 | 3.0  | V    |

| V <sub>o(rec)(diff)</sub>       | Differential bus output voltage<br>(V <sub>CANHx</sub> – V <sub>CANLx</sub> )  | V <sub>TxDx</sub> = High; recessive; no<br>load                                                                                                    | -50  | 0    | +50  | mV   |

| V <sub>o(dom)(diff)_arb</sub>   | Differential bus output voltage during arbitration ( $V_{CANHx} - V_{CANLx}$ ) | R <sub>LT =</sub> 2.24kΩ (Note 13)                                                                                                                 | 1.5  | -    | 5.0  | V    |

| V <sub>o(dom)(sym)</sub>        | Dominant output voltage driver symmetry<br>(VCANHx + VCANLx)                   | $\label{eq:RLT} \begin{array}{l} RLT = 60\Omega; \ C1 = 4.7 \ nF; \ C_{LT} \\ not \ used; \ TxDx = square \\ wave \ up \ to \ 1 \ MHz \end{array}$ | 0.9  | 1.0  | 1.1  | VCCx |

| I <sub>o(sc)(CANH)</sub>        | Short circuit output current at pins CANHx                                     | –3 V < V <sub>CANHx</sub> < +18 V                                                                                                                  | -100 | -    | 1.5  | mA   |

| I <sub>o(sc)(CANL)</sub>        | Short circuit output current at pins CANLx                                     | –3 V < V <sub>CANLx</sub> < +36 V                                                                                                                  | -1.5 | -    | 100  | mA   |

| V <sub>i(rec)(diff)_NM</sub>    | Differential input voltage range recessive state                               | Normal mode;<br>$-12 V \le V_{CANHx}$ ,<br>$V_{CANLx} \le +12 V$ ; no load                                                                         | -3.0 | -    | 0.5  | V    |

| V <sub>i(rec)(diff)_</sub> LP   |                                                                                | Standby mode;<br>$-12 V \le V_{CANHx}$ ,<br>$V_{CANLx} \le +12 V$ ; no load                                                                        | -3.0 |      | 0.4  | V    |

| V <sub>i(dom)(diff)_NM</sub>    | Differential input voltage range dominant state                                | Normal mode;<br>-12 V $\leq$ V <sub>CANHx</sub> ,<br>V <sub>CANLx</sub> $\leq$ +12 V; no load                                                      | 0.9  | -    | 8.0  | V    |

| V <sub>i(dom)(diff)_</sub> LP   |                                                                                | Standby mode;<br>$-12 V \le V_{CANHx}$ ,<br>$V_{CANLx} \le +12 V$ ; no load                                                                        | 1.05 |      | 8.0  | V    |

| $V_{i(diff)(th)\_NORM}$         | Differential receiver threshold voltage in normal mode                         | $\begin{array}{l} -12 \ V \leq V_{CANLx} \leq +12 \ V; \\ -12 \ V \leq V_{CANHx} \leq +12 \ V \end{array}$                                         | 0.5  | _    | 0.9  | V    |

| V <sub>i(diff)(th)_NORM_H</sub> | Differential receiver threshold voltage in normal mode, extended range         | -30 V < V <sub>CANLx</sub> < +35 V;<br>-30 V < V <sub>CANHx</sub> < +35 V                                                                          | 0.4  | -    | 1.0  | V    |

| $V_{i(diff)(th)\_STDBY}$        | Differential receiver threshold voltage in standby mode                        | $\begin{array}{c} -12~V \leq V_{CANLx} \leq +12~V; \\ -12~V \leq V_{CANHx} \leq +12~V \end{array}$                                                 | 0.4  | _    | 1.05 | V    |

| R <sub>i(cm)</sub> (CANH)       | Common-mode input resistance at pin CANHx                                      | $\begin{array}{c} -2 \ V \leq V_{CANLx} \leq +7 \ V; \\ -2 \ V \leq V_{CANHx} \leq +7 \ V \end{array}$                                             | 15   | 26   | 37   | kΩ   |

| R <sub>i(cm)(CANL)</sub>        | Common-mode input resistance at pin CANLx                                      | $\begin{array}{l} -2 \ V \leq V_{CANLx} \leq +7 \ V; \\ -2 \ V \leq V_{CANHx} \leq +7 \ V \end{array}$                                             | 15   | 26   | 37   | kΩ   |

| R <sub>i(cm)(m)</sub>           | Matching between pin CANHx and pin CANLx common mode input resistance          | $V_{CANHx} = V_{CANLx} = +5 V$                                                                                                                     | -1   | 0    | +1   | %    |

| R <sub>i(diff)</sub>            | Differential input resistance                                                  | $\begin{array}{c} -2 \ V \leq V_{CANLx} \leq +7 \ V; \\ -2 \ V \leq V_{CANHx} \leq +7 \ V \end{array}$                                             | 25   | 50   | 75   | kΩ   |

| C <sub>i(CANH)</sub>            | Input capacitance at pins CANHx                                                | V <sub>TxDx</sub> = High; (Note 13)                                                                                                                | -    | 4.5  | 20   | pF   |

| C <sub>i(CANL)</sub>            | Input capacitance at pins CANLx                                                | V <sub>TxDx</sub> = High; (Note 13)                                                                                                                | -    | 4.5  | 20   | pF   |

| C <sub>i(diff)</sub>            | Differential input capacitance                                                 | V <sub>TxDx</sub> = High; (Note 13)                                                                                                                | -    | 3.75 | 10   | pF   |

| THERMAL SHU                     | TDOWN                                                                          |                                                                                                                                                    |      |      |      | -    |

| T <sub>J(sd)</sub>              | Shutdown junction temperature per channel                                      | Junction temperature rising                                                                                                                        | 160  | 180  | 200  | °C   |

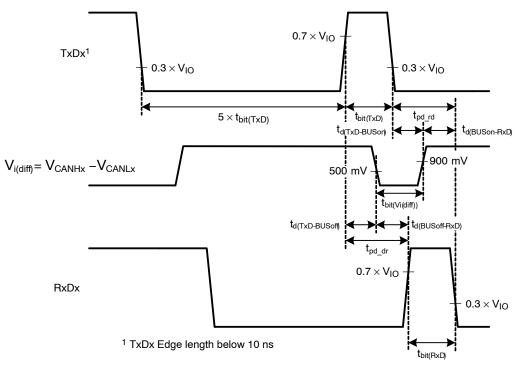

| TIMING CHARA                    | CTERISTICS (see Figure 4 and Figure 6)                                         |                                                                                                                                                    |      |      |      |      |

| t <sub>d(TxD-BUSon)</sub>       | Delay TxDx to bus active                                                       |                                                                                                                                                    | -    | 75   | -    | ns   |

| t <sub>d(TxD-BUSoff)</sub>      | Delay TxDx to bus inactive                                                     |                                                                                                                                                    | -    | 85   | -    | ns   |

| t <sub>d(BUSon-RxD)</sub>       | Delay bus active to RxDx                                                       |                                                                                                                                                    | -    | 24   | -    | ns   |

| t <sub>d(BUSoff-RxD)</sub>      | Delay bus inactive to RxDx                                                     |                                                                                                                                                    | -    | 32   | -    | ns   |

| t <sub>pd_dr</sub>              | Propagation delay TxDx to RxDx dominant to recessive transition                |                                                                                                                                                    | 50   | 100  | 210  | ns   |

#### **Table 5. ELECTRICAL CHARACTERISTICS**

$V_{CC1}, V_{CC2} = 4.75 \text{ V to } 5.25 \text{ V}; T_J = -40^{\circ}\text{C to } + 150^{\circ}\text{C}; R_{LT} = 60 \ \Omega, C_{LT} = 100 \text{ pF}, C_1 \text{ not used}, C_{RxD} = 15 \text{ pF}, \text{ unless specified otherwise}.$

| Symbol                     | Parameter                                                       | Conditions                           | Min | Тур | Max | Unit |  |

|----------------------------|-----------------------------------------------------------------|--------------------------------------|-----|-----|-----|------|--|

| TIMING CHAR                | TIMING CHARACTERISTICS (see Figure 4 and Figure 6)              |                                      |     |     |     |      |  |

| t <sub>pd_rd</sub>         | Propagation delay TxDx to RxDx recessive to dominant transition |                                      | 50  | 120 | 210 | ns   |  |

| t <sub>d(stb-nm)</sub>     | Delay standby mode to normal mode                               |                                      | 5.0 | 11  | 20  | μs   |  |

| t <sub>wake_filt</sub>     | Dominant time for wake-up via bus                               |                                      | 0.5 | -   | 5.0 | μs   |  |

| t <sub>dwakerd</sub>       | Delay to flag wake event<br>(recessive to dominant transitions) | Valid bus wake-up event              | 0.5 | 2.6 | 6.0 | μs   |  |

| t <sub>dwakedr</sub>       | Delay to flag wake event (dominant to recessive transitions)    | Valid bus wake-up event              | 0.5 | 2.6 | 6.0 | μs   |  |

| t <sub>wake_to</sub>       | Bus time for wake-up timeout                                    | Standby mode                         | 1.0 | -   | 10  | ms   |  |

| t <sub>dom(TxD)</sub>      | TxDx dominant time for timeout                                  | V <sub>TxDx</sub> = 0 V; Normal mode | 1.0 | -   | 10  | ms   |  |

| t <sub>Bit(RxD)</sub>      | Bit time on RxDx pin                                            | t <sub>Bit(TxD)</sub> = 500 ns       | 400 | -   | 550 | ns   |  |

|                            |                                                                 | t <sub>Bit(TxD)</sub> = 200 ns       | 120 | -   | 220 | ns   |  |

| t <sub>Bit(Vi(diff))</sub> | Bit time on bus (CANHx – CANLx pin)                             | t <sub>Bit(TxD)</sub> = 500 ns       | 435 | -   | 530 | ns   |  |

|                            |                                                                 | t <sub>Bit(TxD)</sub> = 200 ns       | 155 | -   | 210 | ns   |  |

| $\Delta t_{\text{Rec}}$    | Receiver timing symmetry                                        | t <sub>Bit(TxD)</sub> = 500 ns       | -65 | -   | +40 | ns   |  |

|                            | $\Delta t_{Rec} = t_{Bit(RxD)} - t_{Bit(Vi(diff))};$            | t <sub>Bit(TxD)</sub> = 200 ns       | -45 | -   | +15 | ns   |  |

12. In the range of 4.5 V to 4.75 V and from 5.25 V to 5.5 V the chip is fully functional; some parameters may be outside of the specification. 13. Values based on design and characterization, not tested in production.

#### **MEASUREMENT SETUPS AND DEFINITIONS**

Figure 4. Transceiver Timing Diagram

Figure 5. Test Circuit for Automotive Transients

Figure 6. Test Circuit for Timing Characteristics

#### Table 6. ISO 11898-2:2016 PARAMETER CROSS-REFERENCE TABLE

| ISO 11898–2:2016 Specification                                                 |                                          | NCV7446 Datasheet                                      |

|--------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------|

| Parameter                                                                      | Notation                                 | Symbol                                                 |

| Dominant output characteristics                                                |                                          |                                                        |

| Single ended voltage on CAN_H                                                  | V <sub>CAN_H</sub>                       | V <sub>o(dom)(CANH)</sub>                              |

| Single ended voltage on CAN_L                                                  | V <sub>CAN_L</sub>                       | V <sub>o(dom)(CANL)</sub>                              |

| Differential voltage on normal bus load                                        | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)</sub>                              |

| Differential voltage on effective resistance during arbitration                | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)_arb</sub>                          |

| Differential voltage on extended bus load range (optional)                     | V <sub>Diff</sub>                        | V <sub>o(dom)(diff)</sub>                              |

| Driver symmetry                                                                |                                          |                                                        |

| Driver symmetry                                                                | V <sub>SYM</sub>                         | V <sub>o(dom)(sym)</sub>                               |

| Driver output current                                                          |                                          |                                                        |

| Absolute current on CAN_H                                                      | I <sub>CAN_H</sub>                       | I <sub>o(SC)(CANH)</sub>                               |

| Absolute current on CAN_L                                                      | I <sub>CAN_L</sub>                       | I <sub>o(SC)(CANL)</sub>                               |

| Receiver output characteristics, bus biasing active                            |                                          |                                                        |

| Single ended output voltage on CAN_H                                           | V <sub>CAN_H</sub>                       | V <sub>o(rec)(CANH)</sub>                              |

| Single ended output voltage on CAN_L                                           | V <sub>CAN_L</sub>                       | V <sub>o(rec)(CANL)</sub>                              |

| Differential output voltage                                                    | V <sub>Diff</sub>                        | V <sub>o(rec)(diff)</sub>                              |

| Receiver output characteristics, bus biasing inactive                          |                                          |                                                        |

| Single ended output voltage on CAN_H                                           | V <sub>CAN_H</sub>                       | V <sub>o(off)(CANH)</sub>                              |

| Single ended output voltage on CAN_L                                           | V <sub>CAN_L</sub>                       | V <sub>o(off)(CANL)</sub>                              |

| Differential output voltage                                                    | V <sub>Diff</sub>                        | V <sub>o(off)(dif)</sub>                               |

| Optional transmit dominant timeout                                             |                                          |                                                        |

| Transmit dominant timeout, long                                                | t <sub>dom</sub>                         | t <sub>dom(TxD)</sub>                                  |

| Transmit dominant timeout, short                                               | t <sub>dom</sub>                         | NA                                                     |

| Static receiver input characteristics, bus biasing active                      |                                          |                                                        |

| Recessive state differential input voltage range                               | V <sub>Diff</sub>                        | V <sub>i(rec)(diff)_NM</sub>                           |

| Dominant state differential input voltage range                                | V <sub>Diff</sub>                        | V <sub>i(dom)(diff)_NM</sub>                           |

| Static receiver input characteristics, bus biasing inactive                    |                                          |                                                        |

| Recessive state differential input voltage range                               | V <sub>Diff</sub>                        | V <sub>i(rec)(diff)_LP</sub>                           |

| Dominant state differential input voltage range                                | V <sub>Diff</sub>                        | V <sub>i(dom)(diff)</sub> LP                           |

| Receiver input resistance                                                      |                                          | · ··· · <b>-</b>                                       |

| Differential internal resistance                                               | R <sub>Diff</sub>                        | R <sub>i(diff)</sub>                                   |

| Single ended internal resistance                                               | R <sub>CAN_H</sub><br>R <sub>CAN_L</sub> | R <sub>i(cm)</sub> (CANH)<br>R <sub>i(cm)</sub> (CANL) |

| Receiver input resistance matching                                             |                                          |                                                        |

| Matching a of internal resistance                                              | m <sub>R</sub>                           | R <sub>i(cm)(m)</sub>                                  |

| Implementation loop delay requirement                                          | •                                        |                                                        |

| Loop delay                                                                     | t <sub>Loop</sub>                        | t <sub>pd_rd</sub><br>t <sub>pd_dr</sub>               |

| Optional implementation data signal timing requirements for use with bit rates | above 1 Mbit/s and up t                  | o 2 Mbit/s                                             |

| Transmitted recessive bit width @ 2 Mbit/s                                     | t <sub>Bit(Bus)</sub>                    | t <sub>Bit(Vi(diff))</sub>                             |

| Received recessive bit width @ 2 Mbit/s                                        | t <sub>Bit(RXD)</sub>                    | t <sub>Bit(RxD)</sub>                                  |

| Receiver timing symmetry @ 2 Mbit/s                                            | Δt <sub>Rec</sub>                        | $\Delta_{tRec}$                                        |

#### Table 6. ISO 11898-2:2016 PARAMETER CROSS-REFERENCE TABLE

| ISO 11898–2:2016 Specification                                                     |                                          | NCV7446 Datasheet                      |

|------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------|

| Parameter                                                                          | Notation                                 | Symbol                                 |

| Optional implementation data signal timing requirements for use with bit rates abo | ove 2 Mbit/s and up                      | to 5 Mbit/s                            |

| Transmitted recessive bit width @ 5 Mbit/s                                         | t <sub>Bit(Bus)</sub>                    | t <sub>Bit(Vi(diff))</sub>             |

| Transmitted recessive bit width @ 5 Mbit/s                                         | t <sub>Bit(RXD)</sub>                    | t <sub>Bit(RxD)</sub>                  |

| Received recessive bit width @ 5 Mbit/s                                            | $\Delta t_{Rec}$                         | $\Delta t_{Rec}$                       |

| Maximum ratings of $V_{CAN_H}$ , $V_{CAN_L}$ and $V_{Diff}$                        |                                          |                                        |

| Maximum rating V <sub>Diff</sub>                                                   | V <sub>Diff</sub>                        | V <sub>CANH-CANL</sub>                 |

| General maximum rating $V_{CAN\_H}$ and $V_{CAN\_L}$                               | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub> | V <sub>CANH</sub><br>V <sub>CANL</sub> |

| Optional: Extended maximum rating $V_{CAN\_H}$ and $V_{CAN\_L}$                    | V <sub>CAN_H</sub><br>V <sub>CAN_L</sub> | NA                                     |

| Maximum leakage currents on CAN_H and CAN_L, unpowered                             |                                          |                                        |

| Leakage current on CAN_H, CAN_L                                                    | I <sub>CAN_H</sub><br>I <sub>CAN_L</sub> | lLI                                    |

| Bus biasing control timings                                                        |                                          |                                        |

| CAN activity filter time, long                                                     | t <sub>Filter</sub>                      | t <sub>wake_filt</sub>                 |

| CAN activity filter time, short                                                    | t <sub>Filter</sub>                      | NA                                     |

| Wake-up timeout, short                                                             | t <sub>Wake</sub>                        | NA                                     |

| Wake-up timeout, long                                                              | t <sub>Wake</sub>                        | t <sub>wake_to</sub>                   |

| Timeout for bus inactivity (Required for selective wake-up implementation only)    | t <sub>Silence</sub>                     | NA                                     |

| Bus Bias reaction time (Required for selective wake-up implementation only)        | t <sub>Bias</sub>                        | NA                                     |

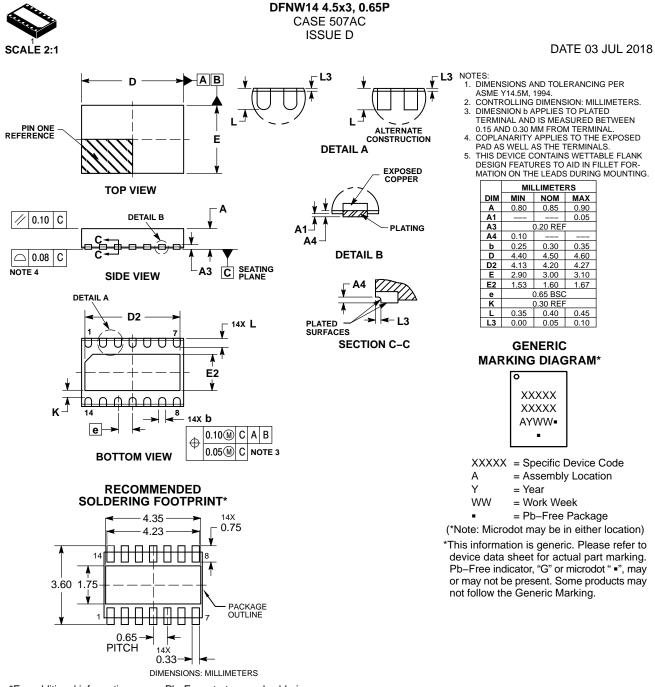

#### **ORDERING INFORMATION**

| Device        | Description                                    | Package             | Shipping <sup>†</sup> |

|---------------|------------------------------------------------|---------------------|-----------------------|

| NCV7446MW0R2G | Dual CAN FD Transceiver, High Speed, Low Power | DFNW14<br>(Pb–Free) | 5000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# onsemi

\*For additional information on our Pb–Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

DOCUMENT NUMBER:

98AON14979G

Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

DESCRIPTION:

DFNW14 4.5x3, 0.65P

PAGE 1 OF 1

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>