Selection. Service. Support.

www.onsemi.com

#### **ON Semiconductor®**

# **Interleaved PFC**

# Agenda

#### □ Introduction:

- Basics of interleaving

- Main benefits

- □ NCP1631: a novel controller for interleaved PFC

- Out-of-phase management

- The NCP1631 allows the use of smaller inductors

- Main functions

- Experimental results and performance

- General waveforms

- Efficiency

- Conclusion

## **Interleaved PFC**

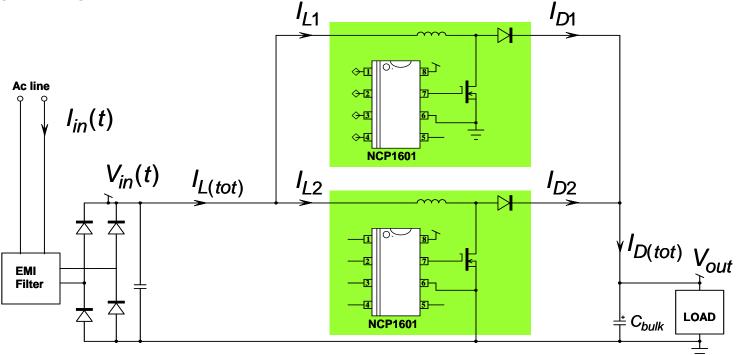

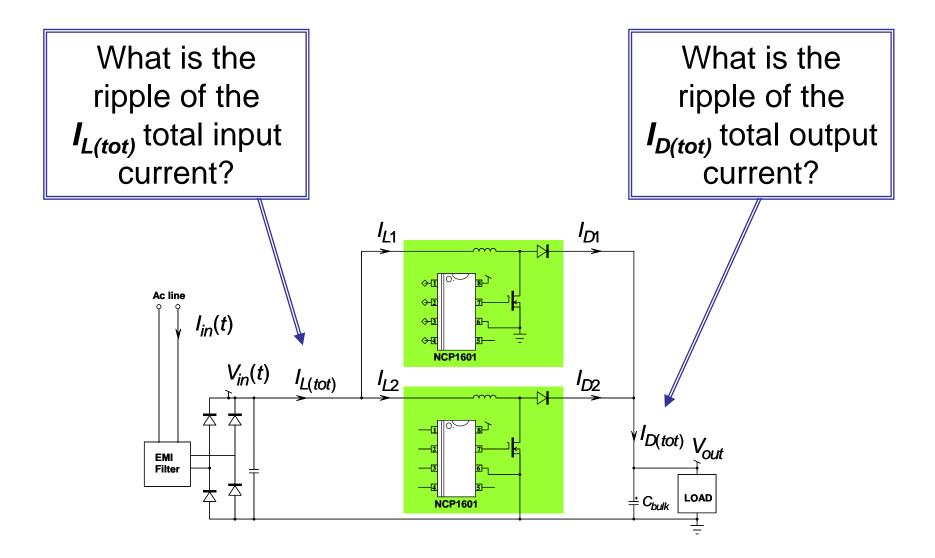

Two small PFC stages delivering (*P<sub>in(avg)</sub>* / 2) in lieu of a single big one

□ If the two phases are out-of-phase, the resulting currents  $(I_{L(tot)})$  and  $(I_{D(tot)})$  exhibit a dramatically reduced ripple.

## **Interleaved Benefits**

□ More components but:

- A 150 W PFC is easier to design than a 300 W one

- Modular approach

- Better heating distribution

- Extended range for Critical Conduction Mode (CrM)

- Smaller components

(help meet strict form factor needs – e.g., flat panels)

- Two DCM PFCs look like a CCM PFC converter...

- Eases EMI filtering and reduces the output rms current

## **Input and Output Current**

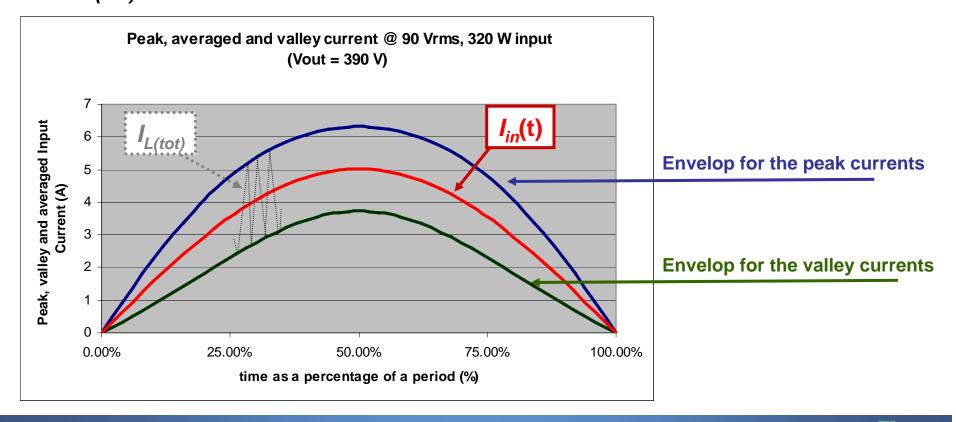

## **Input Current Ripple at Low Line**

- When V<sub>in</sub> remains lower than V<sub>out</sub>/2, the input current looks like that of a CCM, hysteretic PFC

- $\Box$  ( $I_{L(tot)}$ ) swings between two nearly sinusoidal envelops

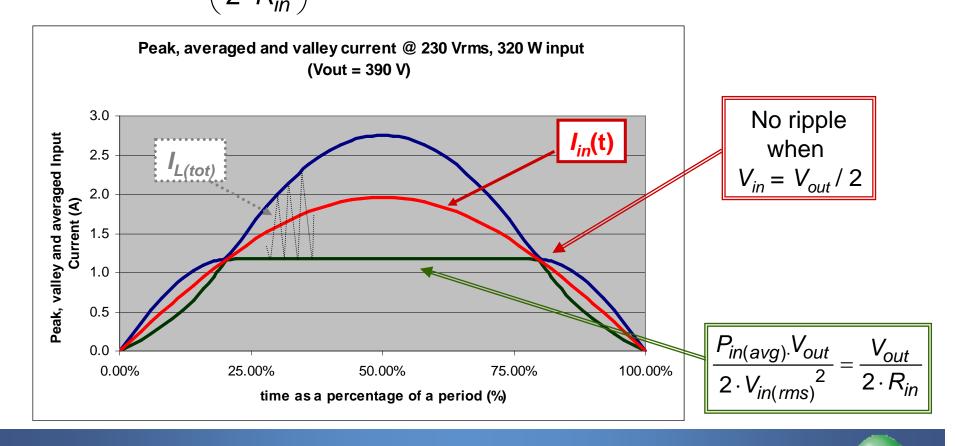

## **Input Current Ripple at High Lline**

□ When  $V_{in}$  exceeds  $(V_{out}/2)$ , the valley current is constant! □ It equates  $\left(\frac{V_{out}}{2 \cdot R_{in}}\right)$  where  $R_{in}$  is the PFC input impedance

## **Line Input Current**

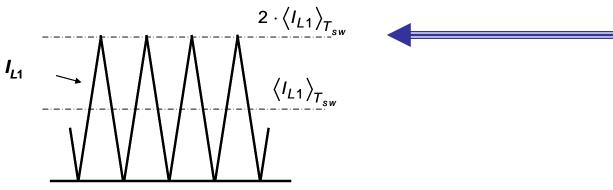

□ <u>For each branch</u>, somewhere within the sinusoid:

The sum of the two averaged, sinusoidal phases currents gives the total line current:

$$I_{in} = \left\langle I_{L(tot)} \right\rangle_{\frac{T_{sw}}{2}} = \left\langle I_{L1} \right\rangle_{T_{sw}} + \left\langle I_{L2} \right\rangle_{T_{sw}}$$

Assuming a perfect current balacing:

$$2 \cdot \left\langle I_{L1} \right\rangle_{T_{sw}} = 2 \cdot \left\langle I_{L2} \right\rangle_{T_{sw}} = I_{in}$$

□ The peak current in each branch is *I<sub>in</sub>*(t)

# Ac Component of the Refueling Current

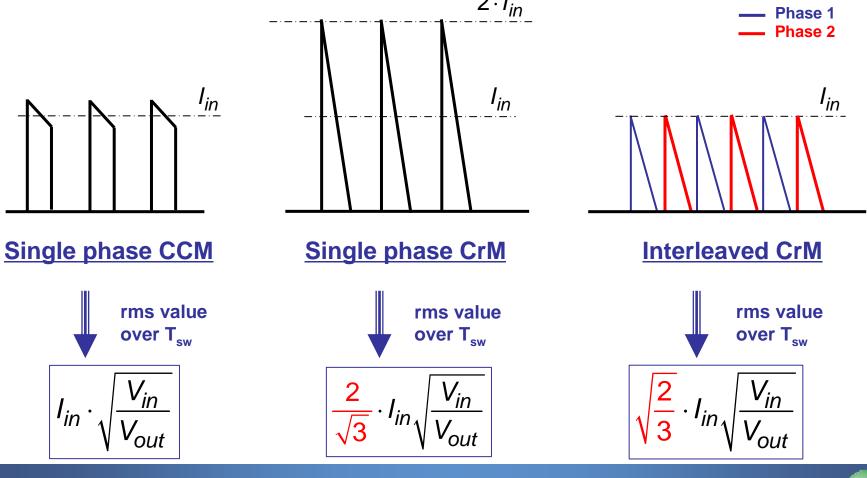

□ The refueling current (output diode(s) current) depends on the mode:  $2 \cdot I_{in}$  — Phase 1

# A Reduced Rms Current in the Bulk Capacitor

□ Integration over the sinusoid leads to (resistive load):

|                                                                 | Single phase CCM<br>PFC                                                                                                                         | Single phase CrM or<br>FCCrM* PFC                                                                                                                   | Interleaved CrM or<br>FCCrM* PFC                                                                                                                    |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Diode(s) rms<br>current<br>( <i>I<sub>D</sub></i> (rms))        | $\sqrt{\frac{8\sqrt{2} \cdot \left(\frac{P_{out}}{\eta}\right)^2}{3\pi \cdot V_{in(rms)} \cdot V_{out}}}$                                       | $\frac{2}{\sqrt{3}} \cdot \sqrt{\frac{8\sqrt{2} \cdot \left(\frac{P_{out}}{\eta}\right)^2}{3\pi \cdot V_{in(rms)} \cdot V_{out}}}$                  | $\sqrt{\frac{2}{3}} \cdot \sqrt{\frac{8\sqrt{2} \cdot \left(\frac{P_{out}}{\eta}\right)^2}{3\pi \cdot V_{in(rms)} \cdot V_{out}}}$                  |

| Capacitor<br>rms current<br>( <i>I<sub>c</sub></i> (rms))       | $\sqrt{\frac{8\sqrt{2}\cdot\left(\frac{P_{out}}{\eta}\right)^2}{3\pi\cdot V_{in(rms)}\cdot V_{out}}} - \left(\frac{P_{out}}{V_{out}}\right)^2}$ | $\sqrt{\frac{32\sqrt{2} \cdot \left(\frac{P_{out}}{\eta}\right)^2}{9\pi \cdot V_{in(rms)} \cdot V_{out}} - \left(\frac{P_{out}}{V_{out}}\right)^2}$ | $\sqrt{\frac{16\sqrt{2} \cdot \left(\frac{P_{out}}{\eta}\right)^2}{9\pi \cdot V_{in(rms)} \cdot V_{out}} - \left(\frac{P_{out}}{V_{out}}\right)^2}$ |

| 300 W,<br>V <sub>out</sub> =390 V<br>V <sub>in(rms)</sub> =90 V | <i>I<sub>D</sub></i> (rms) = 1.9 A<br><i>I<sub>C</sub></i> (rms) = 1.7 A                                                                        | I <sub>D(rms)</sub> = 2.2 A<br>I <sub>C(rms)</sub> = 2.1 A                                                                                          | $I_{D(tot)(rms)} = 1.5 \text{ A}$<br>$I_{C(rms)} = 1.3 \text{ A}$                                                                                   |

□ Interleaving dramatically reduces the rms currents

→ reduced losses, lower heating, increased reliability

\* Frequency Clamped CrM

# Finally...

□ Interleaved PFC combines:

- The advantages of CrM operations

- No need for low t<sub>rr</sub> diode

- High efficiency

- A reduced input current ripple and a minimized rms current in the bulk capacitor

- A better distribution of heating

- □ More components but "small" ones

- Well adapted to slim form factor applications such as notebook adapters and LCD TVs

- □ Refer to application note AND8355 for more details

# Agenda

#### □ Introduction:

- Basics of interleaving

- Main benefits

#### □ NCP1631: a novel controller for interleaved PFC

- Out-of-phase management

- The NCP1631 allows the use of smaller inductors

- Main functions

- Experimental results and performance

- General waveforms

- Efficiency

#### Conclusion

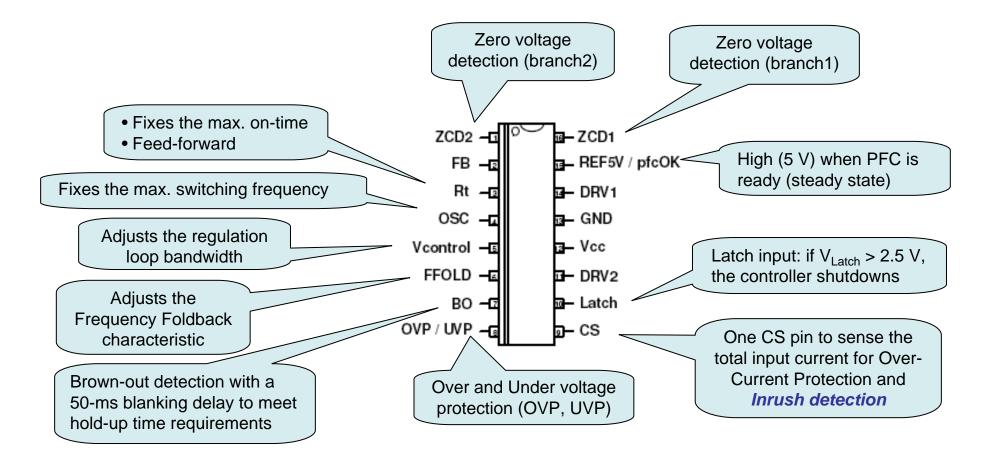

# **NCP1631 Overview**

- □ Interleaved, 2-phase PFC controller

- Frequency Clamped Critical conduction Mode (FCCrM) to optimize the efficiency over the load range.

- Substantial out-of-phase operation in all conditions including start-up, OCP or transient sequences.

- □ Feedforward for improved loop compensation

- □ Eased design of the downstream converter:

- pfcOK, dynamic response enhancer, standby management

- □ High protection level:

- Brown-out protection, accurate 1-pin current limitation, in-rush currents detection, separate pin for (programmable) OVP...

## **NCP1631 Overview**

#### □ Interleaved, 2-phase PFC controller

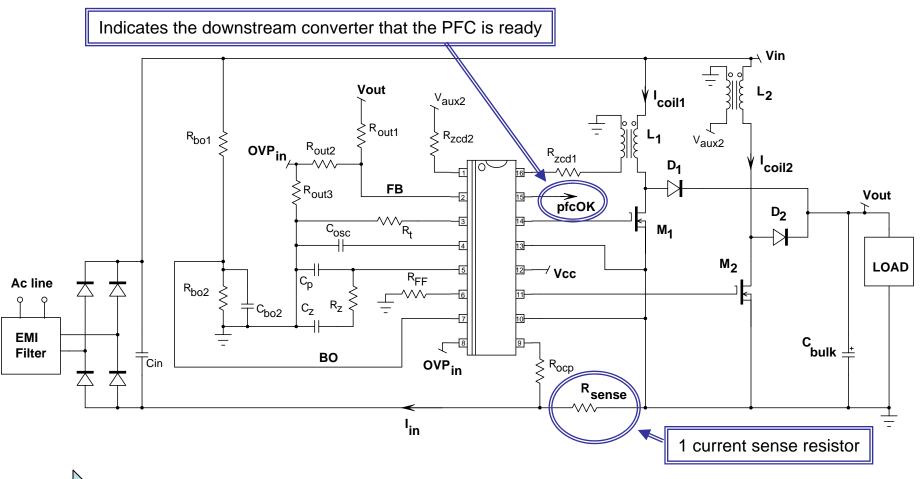

# **NCP1631 Typical Application**

Synchronization of phases is completely internal

٦N

## Interleaving: Master / Slave Approach...

- □ The master branch operates freely

- $\Box$  The slave follows with a 180° phase shift

- Main challenge: maintaining the CrM operation (no CCM, no dead-time)

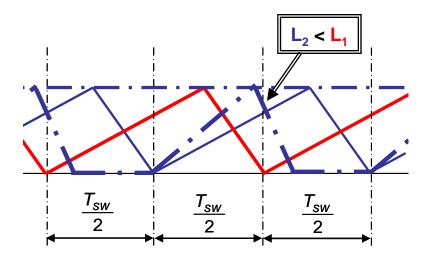

Current mode: inductor unbalance

Voltage mode: on-time shift

### Interleaving: Interactive-Phase Approach...

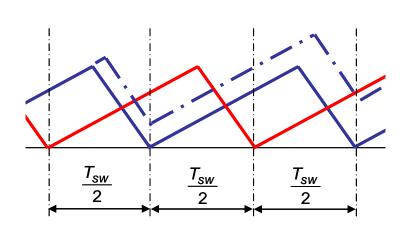

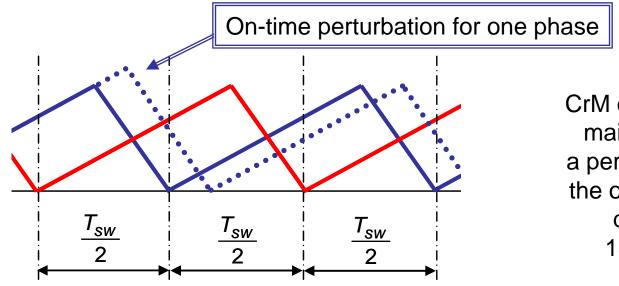

- □ Each phase properly operates in CrM

- □ The two branches interact to set the 180° phase shift

- □ Main challenge: to keep the proper phase shift

CrM operation is maintained but a perturbation of the on-time may degrade the 180° phase shift

#### **We selected this approach**

## **Interleaving Management**

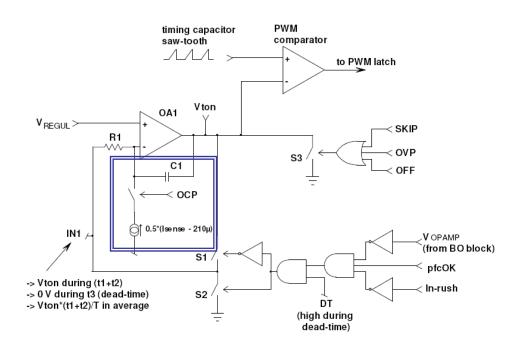

□ The oscillator manages the out-of-phase operation

□ It acts as the *interleaved clocks generator*

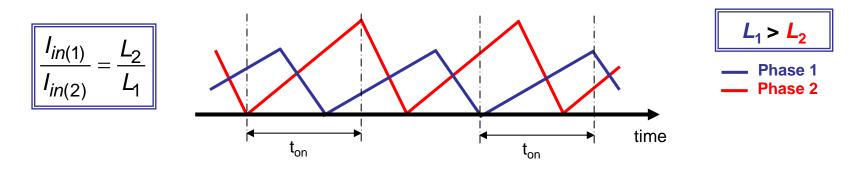

## **Current Balancing between the 2 Branches**

- □ The NCP1631 operates in voltage mode

- □ Same on-time and hence switching period in the two branches

- □ An imbalance in the inductors:

- Does not affect the switching period

- "Only" causes a difference in the power amount conveyed by each branch

- □ The two branches remains synchronized

- □ CrM operation is kept (or FCCrM)

- □ No alteration of the 180 degree phase shift

# **Artificial Unbalancing**

- □ In this test, the 150 µH inductor of branch 1 is replaced by a 300 µH coil !!!!

- Hence, more current is drawn by branch2 and MOSFET of branch2 is (normally) hotter

- The following plots show how the PFC stage behaves in these extreme conditions and full load

## Still Operates in a Robust Manner...

**ON Semiconductor**<sup>\*\*</sup>

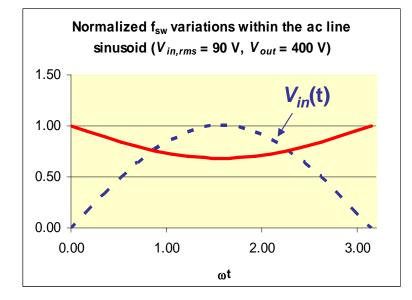

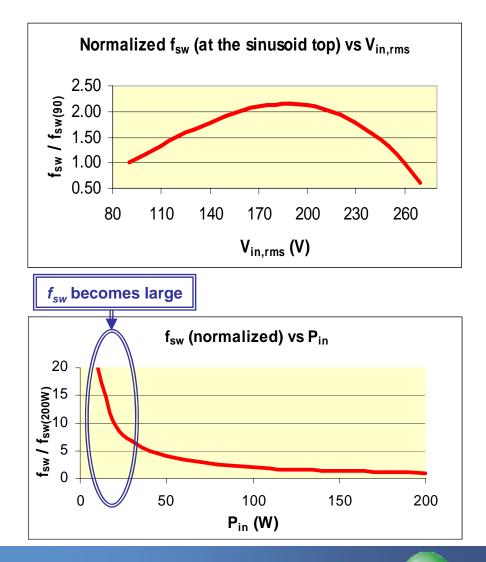

# **Switching Frequency Variations in CrM**

□ The switching frequency varies versus the input power, the ac line amplitude and within the sinusoid □  $f_{sw}$  becomes high at light load, leading to large switching losses □  $f_{sw}$  should be limited

# Limiting $f_{sw}$ to Optimize the Efficiency

□ At the top of the sinusoid:

$$f_{sw} = \frac{\left(V_{in,pk}\right)^{2}}{4 \cdot L \cdot P_{in,avg}} \left(1 - \frac{V_{in,pk}}{V_{out}}\right)$$

CrM operation requires large inductors to limit the switching losses at light load

$\Box$  Can't we clamp  $f_{sw}$  not to over-dimension L?

→ Frequency Clamped Critical conduction Mode (FCCrM)

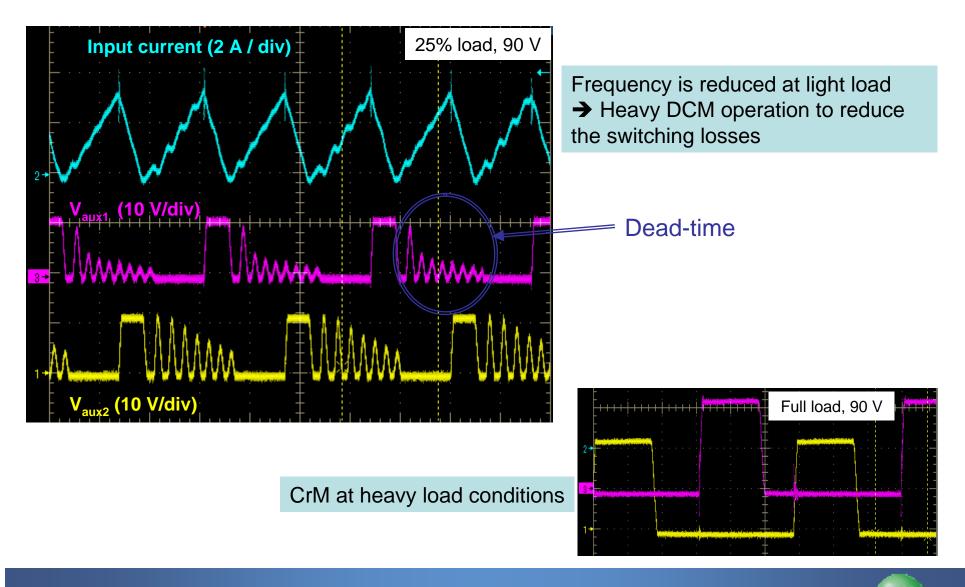

## **Frequency Clamped Critical Conduction Mode**

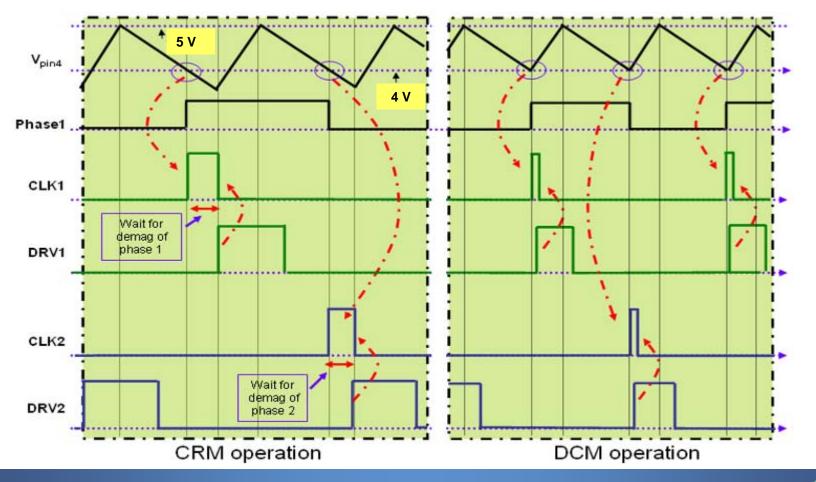

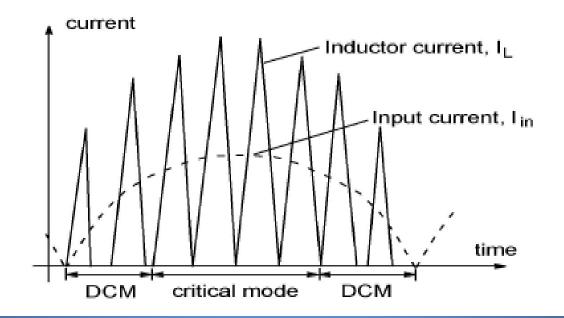

- □ At light load, the current cycle is short

- ❑ When shorter than the oscillator period, no new cycle until the oscillator period is elapsed → dead-times (DCM)

- □ On-times are increased to compensate the dead-times → no PF degradation (ON proprietary)

# **NCP1631 Operation - FCCrM**

□ In FCCrM, the switching frequency is clamped:

- Fixed frequency in light load mode and near the line zero crossing

- Critical conduction mode (CrM) achieved at full load.

- □ FCCrM optimizes the efficiency over the load range.

- □ FCCrM reduces the range of frequencies to be filtered (EMI)

- □ FCCrM allows the use of smaller inductors

- No need for large inductances to limit the frequency range!

- E.g., 150 µH (PQ2620) for a wide mains 300-W application

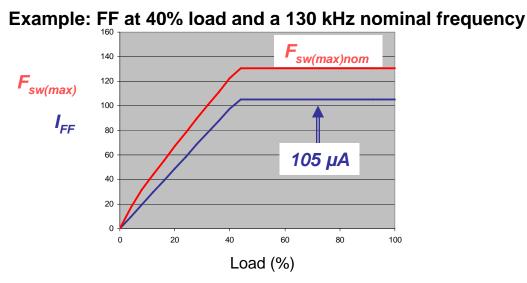

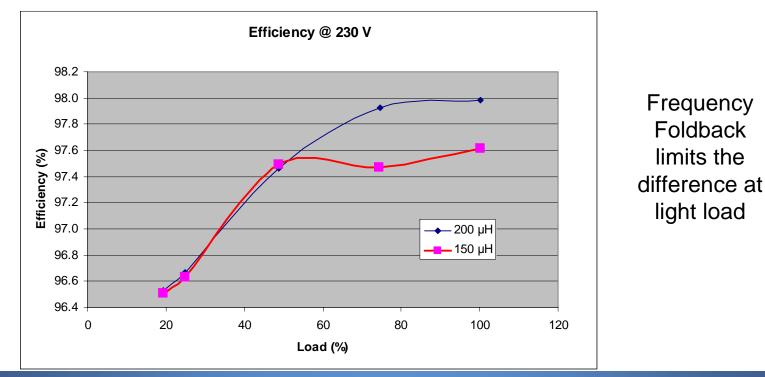

- Frequency Foldback reduces the clamp fequency at light load to further improve the efficiency

# **NCP1631 Frequency Foldback**

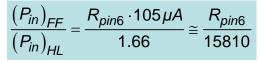

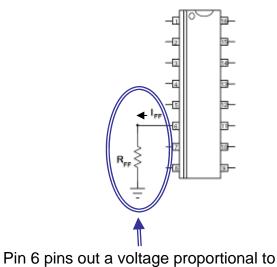

- $\Box$  The clamp frequency *linearly* decays when P<sub>in</sub> goes below a preset level (**P**<sub>LL</sub>)

- $\square$  **P**<sub>LL</sub> is programmed by the pin6 resistor

(*P<sub>in</sub>*)<sub>*HL*</sub> is the max. power deliverable by the PFC stage

Gradual decay of the clamp frequency

No discontinuity in the operation

□ A resistor across the oscillator capacitor sets a minimum clamp frequency

(e.g., 20 kHz - see application note AND8407)

the power. The I<sub>FF</sub> current is clamped to 105µA and used to charge and discharge the oscillator capacitor

# **Light Load Operation**

# **No Load Consumption**

| Conditions                                                                                                  | Line<br>Voltage<br>(V) | Input<br>Power<br>(mW) |

|-------------------------------------------------------------------------------------------------------------|------------------------|------------------------|

| No Frequency Foldback (pin6 grounded)                                                                       | 115                    | 107                    |

| □ 2 separate $V_{out}$ sensing networks for FB and OVP for a total 185-µA leakage on the $V_{out}$ rail     | 230                    | 138                    |

| <b>Γ</b> Frequency Foldback ( $R_{FF} = 4.7 \text{ k}\Omega$ )                                              | 115                    | 96                     |

| □ 2 separate $V_{out}$ sensing networks for FB and OVP for a total 185-µA leakage on the $V_{out}$ rail (*) | 230                    | 134                    |

| <b>□</b> Frequency Foldback ( $R_{FF} = 4.7 \text{ k}\Omega$ )                                              | 115                    | 38                     |

| □ one $V_{out}$ sensing network for FB and OVP for a total 48-µA leakage on the $V_{out}$ rail              | 230                    | 82                     |

- □ Measured on the 300 W NCP1631 demoboard

- $\square$  External  $V_{cc}$ , 3 \* 680 k $\Omega$  resistors to discharge the X2 capacitors

- Frequency Foldback improves the efficiency in light load but also in no-load conditions

(\*) Default demoboard configuration

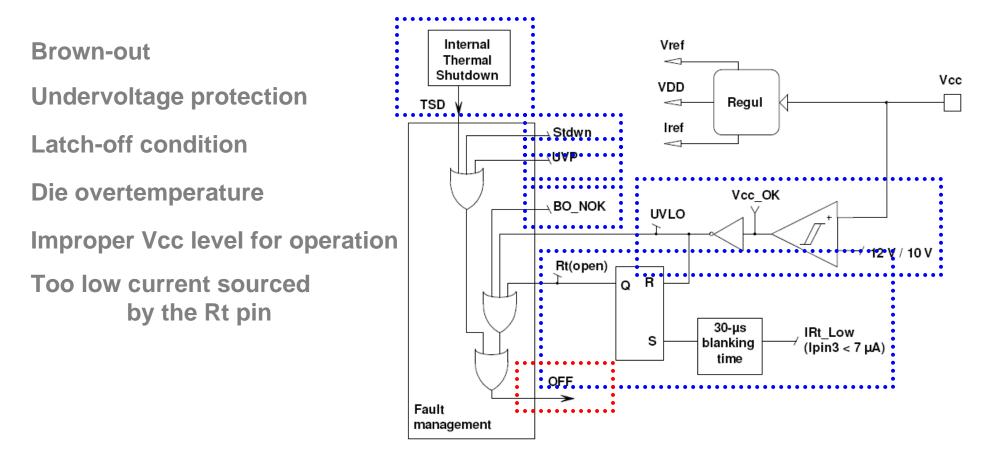

# **NCP1631 Fault Management**

In OFF mode, the major part of the circuit sleeps and consumption is minimized to < 500  $\mu A$

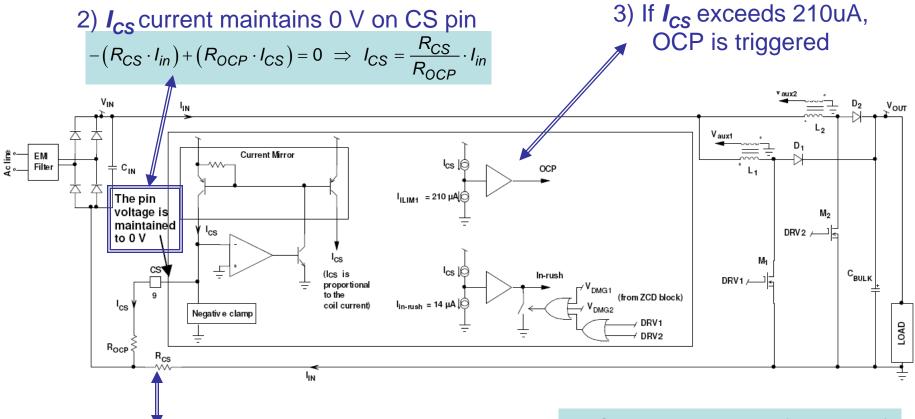

## **NCP1631 Over Current Protection**

NCP1631 monitors a negative voltage, V<sub>cs</sub>, proportional to the current drawn by both interleaved branches, I<sub>in</sub>. Select *R<sub>cs</sub>* freely (optimally)

*R<sub>ocp</sub>* sets the current limit

Minimized losses in *R<sub>cs</sub>*

## **NCP1631 Overcurrent Protection**

When  $I_{CS} > 210 \ \mu$  A, the OCP switch closes and a current equal to  $0.5^*(I_{CS} - 210 \ \mu$  A) is injected into the negative input of the V<sub>TON</sub> processing opamp  $\rightarrow$  the on-time sharply reduces proportionally to the magnitude of the overcurrent event.

# No discontinuity in the operation, out-of-phase operation is maintained No need for preventing OCP from tripping during a normal transient The current can be accurately limited

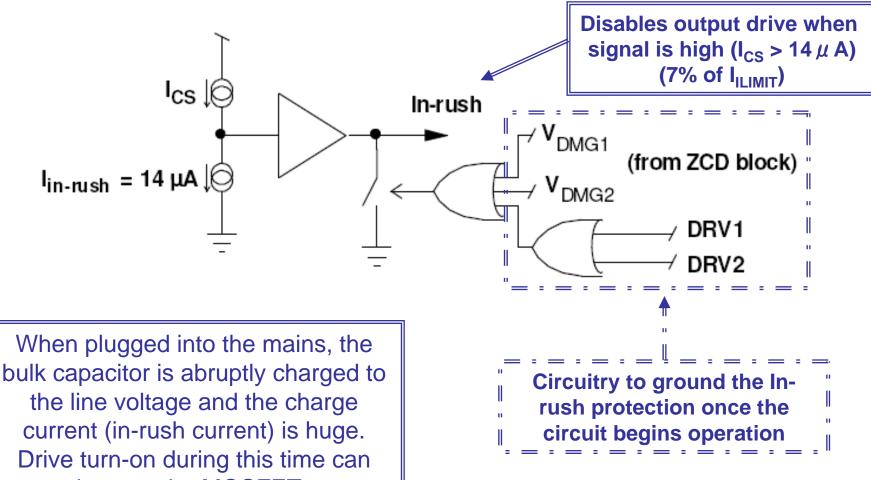

## **NCP1631 In-rush Current Detection**

damage the MOSFETs.

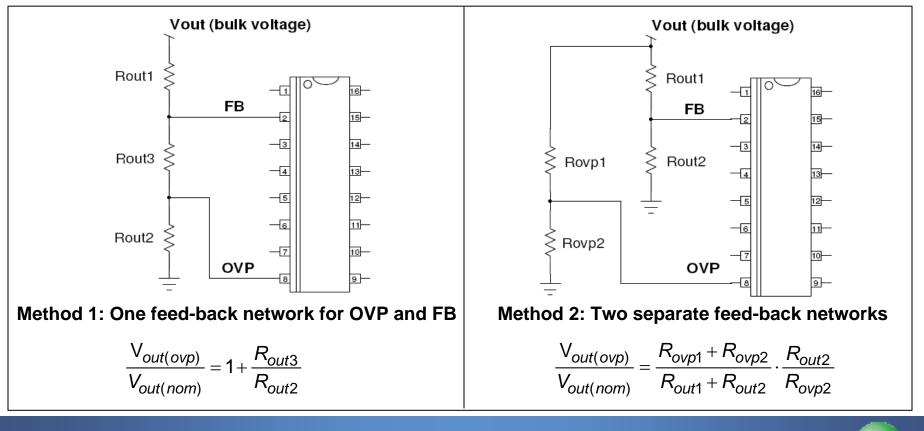

## **NCP1631 Over Voltage Protection**

□ Separate pins for FB and OVP (redundancy)

□ The two functions share the same 2.5 V internal reference for an eased and accurate setting of the OVP level

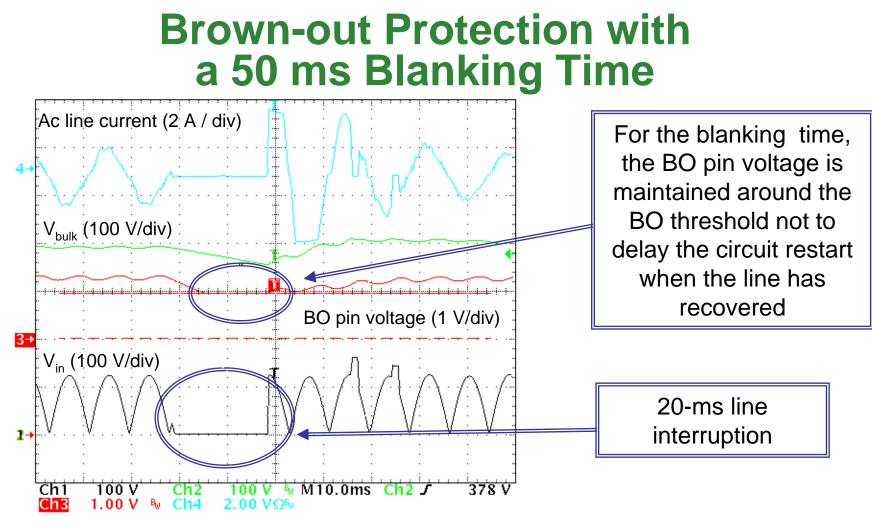

- Mains interruptions shorter than 50 ms are ignored

- □ The blanking time helps meet hold-up time requirements

- The BO pin voltage serves for feedforward

# NCP1631 PfcOK / REF5V Signal

- The pfcOK signal can be used to enable/disable the downstream converter.

- □ It is high (5 V) when the PFC stage is in normal operation and low otherwise.

- □ The pfcOK signal is low:

- Any time the PFC is off because a major fault is detected (UVLO condition, thermal shutdown,UVP, Brown-out, Latch-off / shutdown, *R<sub>t</sub>* pin open)

- For the start-up phase of the PFC stage until the nominal bulk voltage is obtained

- □ The pfcOK pin can be used as a 5 V power source (5 mA capability)

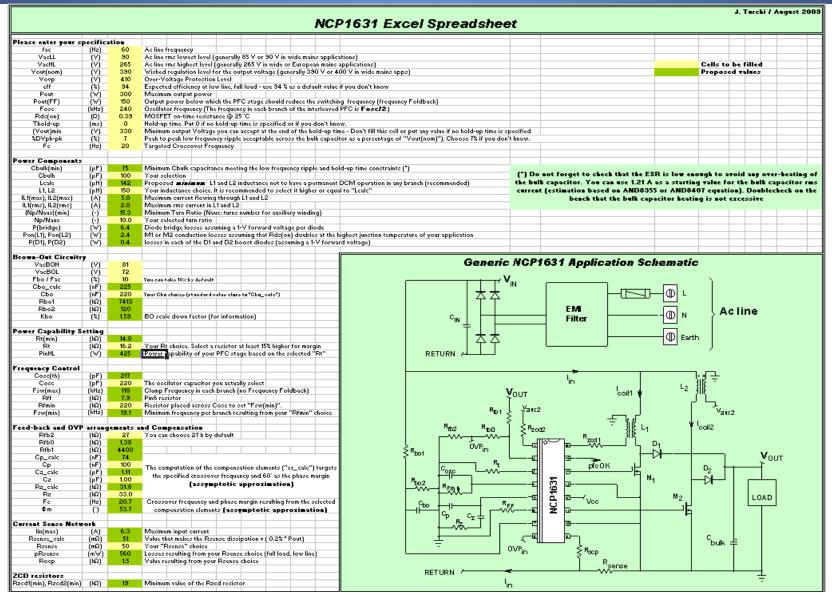

A (simple but easy to use) Excel Spreadsheet (<u>www.onsemi.com</u>) computes the external components

# Agenda

#### □ Introduction:

- Basics of interleaving

- Main benefits

- □ NCP1631: a novel controller for interleaved PFC

- Out-of-phase management

- The NCP1631 allows the use of smaller inductors

- Main functions

- Experimental results and performance

- General waveforms

- Efficiency

#### Conclusion

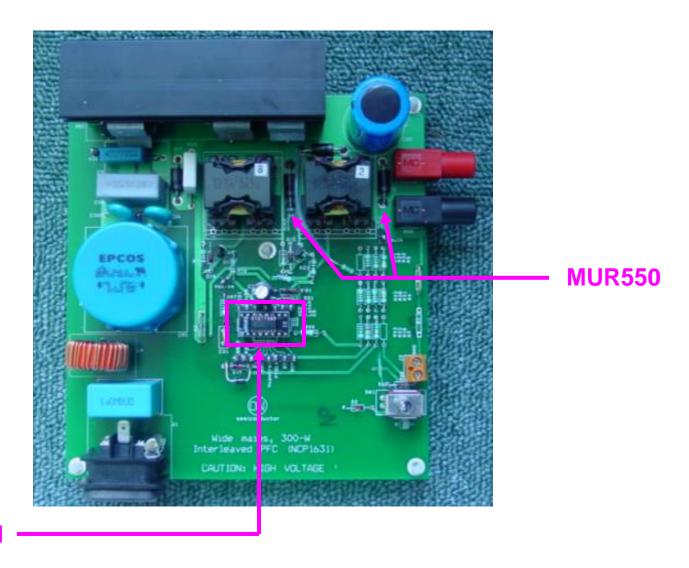

#### **NCP1631 Demoboard**

Wide mains, 300 W, PFC pre-converter

#### **NCP1631**

**ON Semiconductor**\*\*

٦N

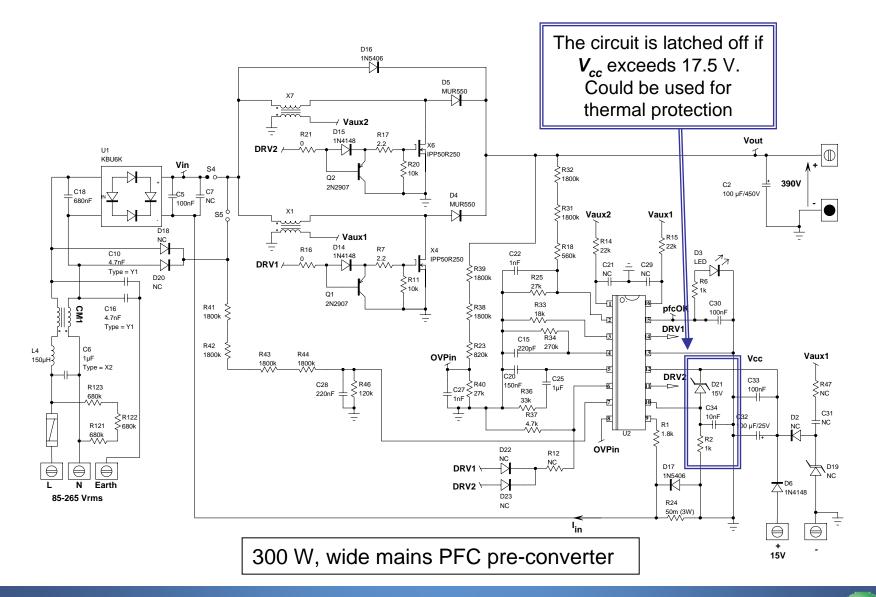

#### **NCP1631 Demoboard Schematic**

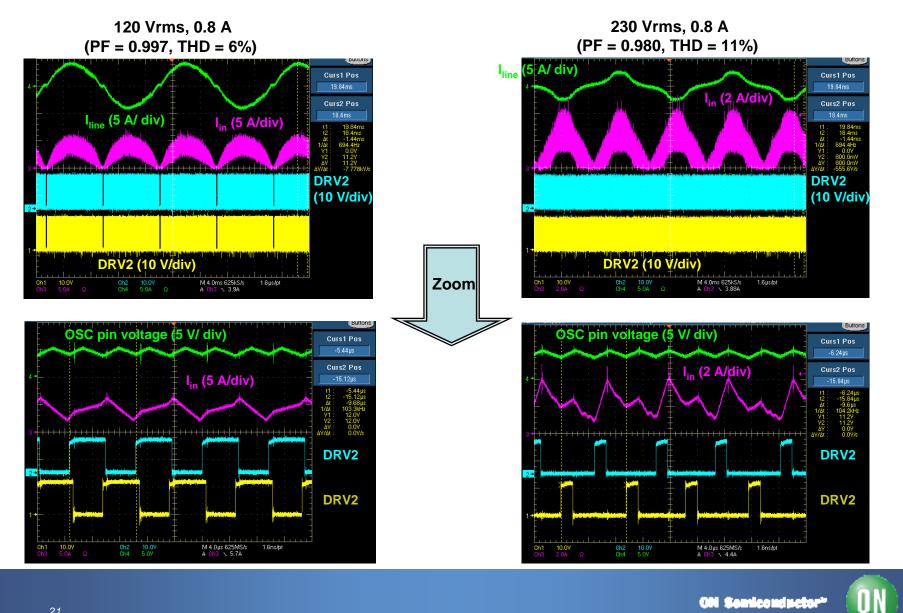

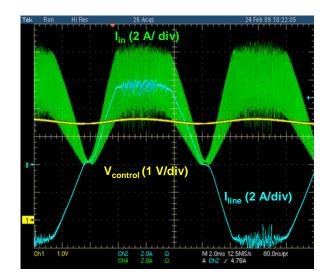

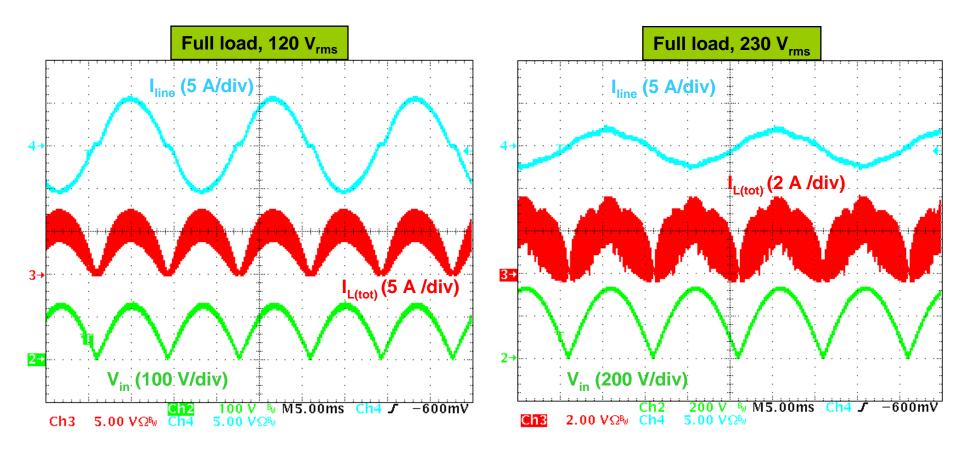

## **Input Voltage and Current**

As expected, the input current looks like a CCM one

At high line, frequency foldback influences the ripple

#### **Zoom of the Precedent Plots**

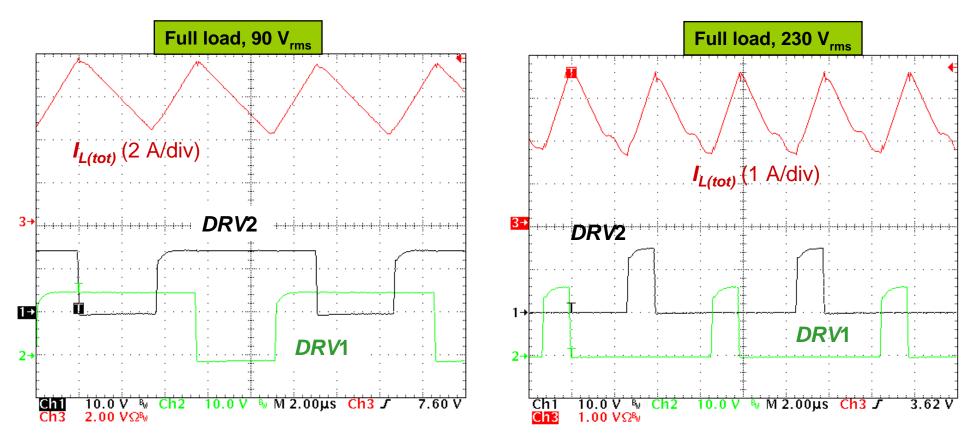

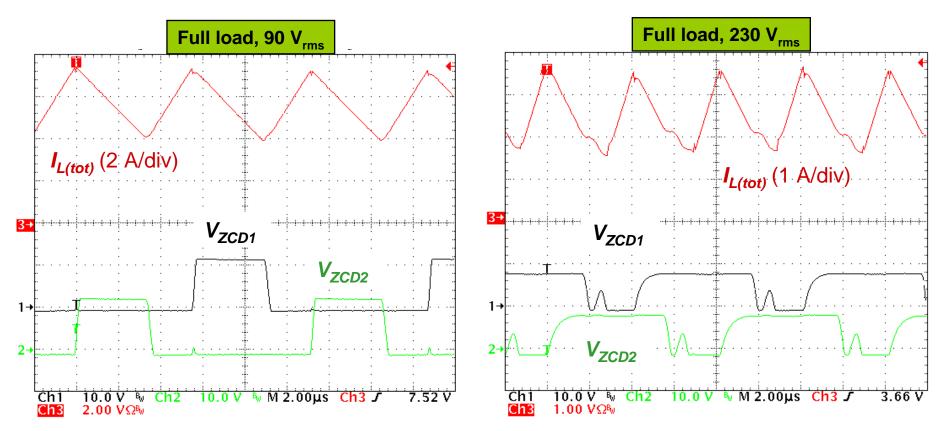

□ These plots were obtained at the sinusoid top

The current swings at twice the frequency of each phase

□ At low and high line, the phase shift is substantially 180°

# **Refueling Sequences**

CrM at low line with valley switching

- □ Fixed frequency operation at high line (frequency clamp)

- Out-of-phase operation in both cases

# **Efficiency Measurements**

- □ The output voltage is generally 390 V

- □ For a 300 W application, the output current is:

- 770 mA at full load

- 154 mA at 20% of the load

- □ Both currents are generally measured with the same tool

- □ If @ 20% of the load, the input power is 63 W

- □ 1-mA error in I<sub>out</sub> leads to

- $I_{out} = 153 \text{ mA} \Rightarrow \text{Eff} = 100 \text{ x} 390 \text{ x} 0.153 / 63 = 94.7 \%$

- $I_{out} = 155 \text{ mA} \Rightarrow \text{Eff} = 100 \text{ x} 390 \text{ x} 0.155 / 63 = 95.9 \%$

- $\Box$  A 1-mA error causes a 1.2% difference in the efficiency!

- □ Measurements @ 10% and 20% of the load need care!!!

## **Efficiency Measurements**

The efficiency does not only depend on the control mode

- □ The inductor, the MOSFETs, diodes, EMI filter... play a role

- □ For instance, if we compare the efficiency with a 200 µH PQ2625 inductor to that with a 150 µH PQ2620 one:

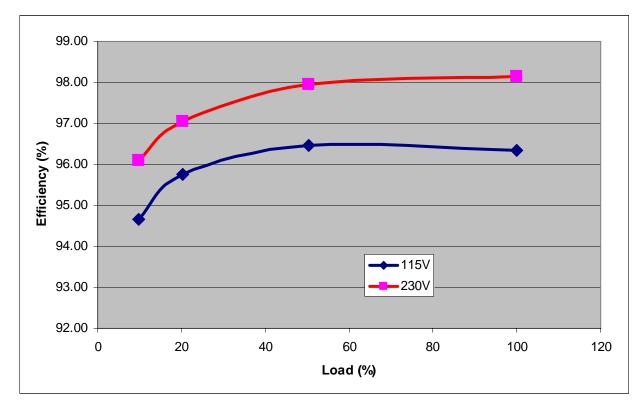

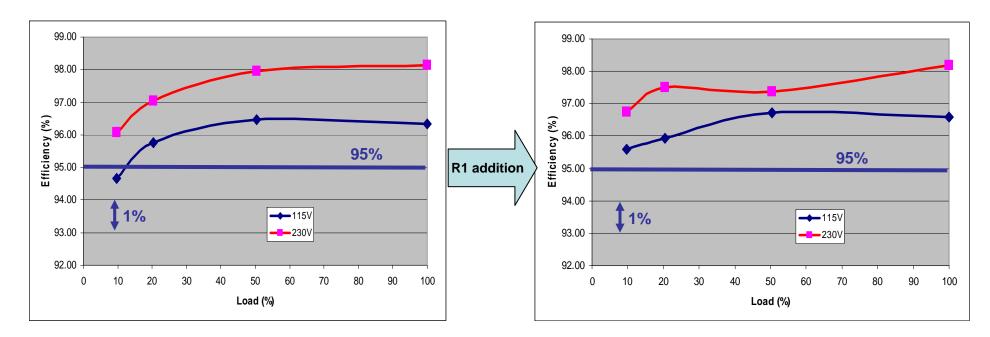

## **Demoboard Efficiency**

□ In the 20% to 100% range, the efficiency remains:

- > 95.8% at low line

- > 97.0 % at high line

□ Refer to NCP1631EVB/D at <u>www.onsemi.com</u> for details

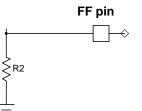

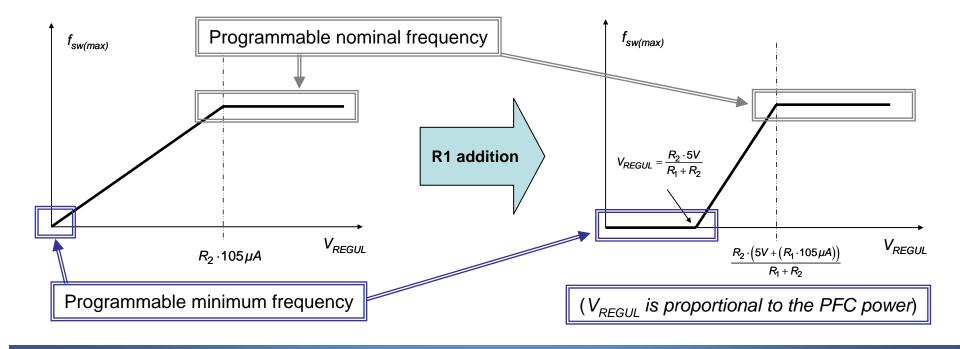

## **Tweaking Frequency Foldback ...**

A resistor can be added between

the pfcOK (5 V) and frequency foldback pins

Doing so, the frequency clamp decays more sharply:

## **Efficiency Improvement**

A resistor on the oscillator pin sets the minimum frequency

- ❑ With R<sub>1</sub>, the PFC stage operates at the minimum frequency (20 kHz) at 10% and 20% of the load

- □ The tweak further improves the light load efficiency

# Agenda

#### □ Introduction:

- Basics of interleaving

- Main benefits

- □ NCP1631: a novel controller for interleaved PFC

- Out-of-phase management

- The NCP1631 allows the use of smaller inductors

- Main functions

- Experimental results and performance

- General waveforms

- Efficiency

#### Conclusion

# Conclusion

- Interleaved PFC allows use of smaller components, improves thermal performance, increases the CrM power range and reduces current ripple.

- The NCP1631 provides a single IC solution which incorporates all the features necessary for building a robust and compact 2-phase interleaved PFC stage with minimal external components.

- □ Its FCCrM and frequency foldback allows an efficient operation over the load range with small inductors

## **For More Information**

View the extensive portfolio of power management products from ON Semiconductor at <u>www.onsemi.com</u>

View reference designs, design notes, and other material supporting the design of highly efficient power supplies at <u>www.onsemi.com/powersupplies</u>