**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# Addressing Thermal Challenges in High-Density Power Applications

Demand for more features and higher performance from ever-smaller form factors presents significant challenges for engineers developing applications such as DC-DC conversion, computing, industrial motor drives, and telecommunications. In many cases, for example, enhancing capabilities and functionality can lead to the need for larger components and, consequently, demand for more cooling. Forced-air cooling can be cumbersome, unreliable and inefficient. Passive cooling using heatsinks adds bulk and cost to the design and, ultimately, the end product. Thermal issues can, effectively, stop innovation in its tracks.

Experienced power designers know that the best way to deal with heat is to not generate it in the first place, meaning that each design generation has to be more efficient than the previous. Correct selection of the topology and, more importantly, the power switching components, is critical to a successful design. However, all power circuits generate some heat, no matter how efficient they are. As designs get smaller, the opportunities for passive convection cooling are reduced and designers have to find intelligent and innovative ways to thermally connect semiconductor junctions to the ambient environment where the heat can dissipate.

Not only does the package affect thermal performance, the leads themselves can also have an impact. For instance, packages with longer leads introduce parasitic elements into the circuit that can affect both speed of operation and efficiency.

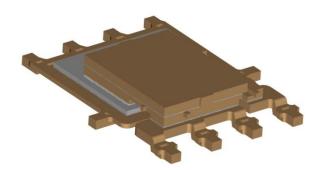

## DUAL COOL<sup>®</sup> Advances PQFN Packaging

Pursuing a strategy of power density leadership, ON Semiconductor has developed a power-specific packaging technology to meet the escalating demand for improved thermal management in modern electronic designs. Based on industry-standard Power Quad Flat No-Lead (PQFN) packaging, 'Dual Cool' technology creates a direct heat path from the drain and source sides of the vertical MOSFET die structure through the addition of a heat slug to the top of the package. This structure allows for supplemental cooling on top of the package with a heatsink system while also providing a direct thermal conduction path into the printed circuit board (PCB).

### **ON Semiconductor®**

www.onsemi.com

# **TECHNICAL NOTE**

Dual Cool package construction is an evolutionary extension of the popular PQFN form factor, incorporating new features to meet future performance expectations. By retaining the very popular Power33 and Power56 lead geometries and pinouts, the package allows designers to improve heatsink performance in existing PCB pad designs. Customers currently using a heatsink on the surface of a PowerQFN package will find this a very useful feature, allowing an easy transition.

Copper clips, similar to leadframes, replace wire bonding inside the Dual Cool concept. Not only does this approach improve thermal conductivity but it also increases current handling capability within the compact PQFN form factor, thereby enabling higher power densities with excellent thermal properties. In fact, the standard PQFN package using the clip technology offers a 13.9% improvement over the wire bond-based PQFN package. Dual Cool technology further improves the performance differential to 57.5% in a  $5 \times 6$  mm package.

# TND6224/D

| 5 x 6 Package Interconnect | QJA (°C/W) | (%) Improvement from<br>Wire Package |

|----------------------------|------------|--------------------------------------|

| PQFN Wire                  | 27.1       | —                                    |

| PQFN Clip                  | 23.8       | 13.9                                 |

| Dual Cool Package          | 17.2       | 57.5                                 |

Environment: Minimum Pad, Heat Sink, 200 LFM Forced Air

Figure 2. The Cu Clip Offers Significant Improvement in Performance

Dual Cool uses 4 mils thin silicon as the core package design constraint. This represents half the thickness of the typical MOSFET that traditionally used 8 mils thick silicon dice. By reducing the die thickness to 4 mils, thermal and electrical performance are improved. This is thanks to the lower parasitic resistance created by the bulk resistance from the doped silicon area through which electrons flow to get from the trench structure at the top of the wafer to the drain lead frame connection at the bottom.

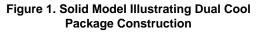

Figure 3. Cross Section of Dual Cool and Heatsink Assembly

The top and bottom surfaces of the die are plated with solderable metal to permit solder attachment of the drain lead frame on the bottom, and the source and gate clips on the top. To improve the heat transfer path from the die to the top of the package for use with a heatsink, a heat slug is soldered to the source clip. This is exposed on the top of the package to provide the heatsink interface.

Solder attachment of the silicon to the lead frames, with optimized copper clips additionally reduces electrical and thermal parasitics. The  $\theta_{JC}$  (thermal resistance from the junction to the case) has two important values with this package type: the junction to case thermal resistance to the drain tab as well as the top heat slug. The datasheet offers these values for each specific product type. These numbers are a measure of the two efficient heat paths out of the component, giving the designer options for managing the heat loads created by high power density designs.

#### **DUAL COOL Enhances POWERTRENCH<sup>®</sup> MOSFETs**

ON Semiconductor's PowerTrench MOSFETs offer excellent electrical properties including very low levels of  $R_{DS(on)}$ . The fully RoHS-compliant products include an integrated monolithic SyncFET<sup>M</sup> Schottky body diode making this technology a leading choice for power designers. PowerTrench SyncFETs became a natural choice to benefit from the new Dual Cool packaging concept. The combination of Dual Cool and PowerTrench occupies the same land pattern as  $5 \times 6$  mm and  $3.3 \times 3.3$  mm PQFN–JEDEC standard parts, yet allows for > 60% better thermal performance.

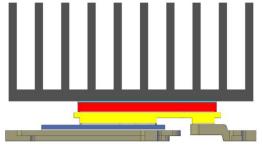

# Maximum Power Dissipation Capable of >60% Better Thermal Performance

Figure 4. Dual Cool has > 60% Better Thermal Performance than PQFN

The Dual Cool PowerTrench MOSFETs with top-side cooling have a far better thermal coupling to the top of the device. In many cases, they can be used without an additional heatsink thereby reducing size, cost and weight. With enhanced dual-path thermal performance and improved parasitics over its wire-bonded predecessors, the use of a heatsink provides even more impressive results.

Laboratory testing proves that when a heatsink is used with Dual Cool package technology, synchronous buck converters deliver higher output current and increased power density. With ON Semiconductor's trench silicon technology, Dual Cool packaging proves to be a clear leader in both power density and thermal performance.

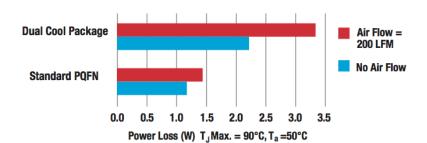

Figure 5. PQFN Based Dual Cool Packaging

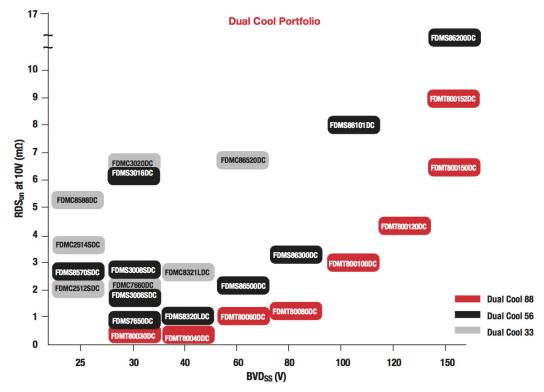

The Dual Cool portfolio offers in excess of 20 products with  $BVD_{SS}$  covering the range 25 V to 150 V and a number of choices for  $R_{DS(on)}$  and package size.

Figure 6. The Broad PowerTrench/Dual Cool Portfolio Offers Designers Choices

Dual Cool solutions are lead-free, RoHS-compliant, and available in  $3.3 \times 3.3$  mm,  $5 \times 6$  mm, and  $8 \times 8$  mm PQFN packages.

#### TND6224/D

#### **Use with Heatsinks**

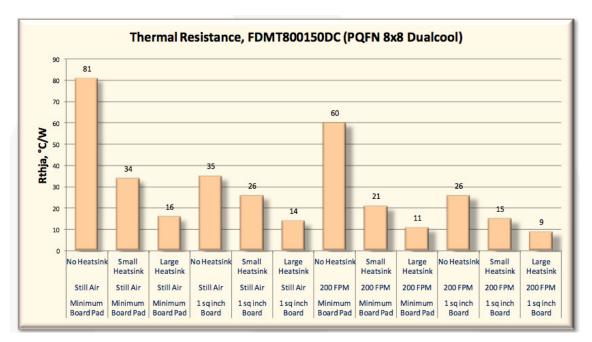

Depending on the size of any heatsink used on the top-side of the package and any air flow that may be present, the thermal resistance from the semiconductor to ambient can be further improved.

Figure 7. Comparison of Various Cooling Modes

In Figure 7 above, the large heatsink is aluminum measuring  $45.2 \times 41.4 \times 12.7$  mm, and the smaller one is  $20.9 \times 10.4 \times 12.7$  mm.

Various types of heatsinks are available and the design, form factor, and mechanism for thermal dissipation will depend on the application, available space and heat to be dissipated. Methods of attachment also vary and include solder anchoring, push pin, thermal tape, screwing, or glue/adhesive.

Thermal interface materials can be used to improve the contact between the Dual Cool package and the heatsink and eliminate the possibility of air gaps in the interface that will limit heat dissipation.

Thermal interface materials (TIM) are available in many forms and include the following:

- Thermal Grease

- Insulating Pad

- Phase-change Materials

- Thermal Tape

- Gap Filler Sheet or Gel

- Thermally Conductive Glue or Adhesives

Testing by ON Semiconductor has shown that thermal grease provides an across-the-board improvement over gap

filler sheets. It was found for the wire bonded units that performance improved 10% over gap pad, for the clip bonded 12%, and for Dual Cool performance improved 21% over the Gap Pad.

This represents a theoretical improvement in allowable dissipated power from 5.8 W with the gap pad to 7.0 W with the grease. Grease is the best performance-wise, but is more difficult to dispense, rework and does not have the electrical isolation properties of the pad. The application will dictate if these trade-offs are worth making.

In applications where tightening a screw, a push pin, or a solder anchor is used to secure the heatsink, a compression load is placed on the component. The PQFN  $8 \times 8$  Dual Cool package has been tested and simulated to withstand high compression loads. Results show that the package can withstand up to 1500 N of load without causing any electrical or mechanical failure.

#### **PCB and Manufacturing Considerations**

PQFN packages are widely used for low-voltage applications. Due to the small configuration and low profile, these packages provide a good space-saving alternative to the typical leaded options. The Dual Cool package offers a size advantage over the industrial standard D2PAK SMD package.

#### TND6224/D

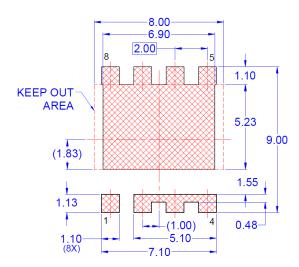

#### Figure 8. Recommended Land Pattern for $8 \times 8$ PQFN (Dimensions in mm)

The source and gate pads are larger than the package lead to allow toe filleting of the solder. The pads are also wider than the leads, providing allowance for variation in board fabrication and component placement during assembly. Combined, these tolerances can stack up to 0.10 mm.

The land pad for the exposed thermal pads is identical to the size of the exposed pad. This large connection between the board and the component allows the strong surface tension of the molten solder to pull the component so that it perfectly aligns with the land pad. Correct PCB layout will ensure that the Dual Cool packages are consistently aligned during production. In power applications where a large amount of heat is generated during operation, the Cu land pattern provides a larger area for heat to be dissipated into the PCB itself.

On the thermal characterization of PQFN  $8 \times 8$  Dual Cool packages, there is significant improvement in the thermal resistance from junction to ambient if the Cu registration on the printed circuit board is increased from a minimum pad to a larger (say  $1 \text{ in}^2$ ) Cu pad connected to the solder-mask-defined land pad.

Therefore, it is recommended that the drain pad on the board be routed and connected to a large Cu area on the board for heat dissipation.

#### Summary

Clearly the combination of PowerTrench technology with the Dual Cool packaging concept addresses the two fundamental challenges of modern power design; operating as efficiently as possible to minimize heat generation and then transmitting what heat is generated as efficiently as possible from the semiconductor junction to the ambient environment.

In some applications, the package can be used without additional cooling and, where additional cooling is required, a heatsink can be mounted easily to provide substantial thermal performance gains.

DUAL COOL and POWERTRENCH are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries, SyncFET is a trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

ON Semiconductor and image are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns ne rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent\_Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor as any support or applications or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regarding testing or or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor products are and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor design or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthori

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative