## **ON Semiconductor**

### Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# AX-RadioLAB for AX5043 User Manual

#### Introduction:

The AX-RadioLAB is hands on configuration and firmware source code generation tool for the AX5043 transceiver IC.

It creates C-code firmware projects based on the AXRadio2 API (described in DOCU/AXRadioV2API.pdf), which demonstrate the use of the AX5043 transceiver together with the AX8052F100 micro controller for packet transmission and reception in several modes. Packets can be transmitted periodically or upon pressing a button. On the receiver side the available options are:

- RX continuous (RX is always on)

- · Wake on Radio

- RX Synchronized with TX (The RX is on for the time in which packets are expected only).

Optionally received packets can be answered with an acknowledge packet in all modes.

AX-RadioLAB allows direct downloading of the created firmware to AXSEM DVK-2 main boards and AXSEM F143-MINI-DVM, where it can be run and tested immediately. A dedicated firmware project implements basic tests like putting the transmitter into CW mode or measuring bit error rates.

ON Semiconductor®

www.onsemi.com

#### **APPLICATION NOTE**

The first step in working with AX-RadioLAB is to create a new AX-RadioLAB project. Firmware projects implementing the TX and RX mode selected in the AX-RadioLAB GUI are created inside your project directory.

The AX-RadioLAB GUI makes it easy to configure physical parameters of the wireless link as well as the framing format and various possible functions of the AX5043 general purpose pins.

Optionally you can view and modify the generated firmware source code using the AXCode::Blocks IDE. The firmware also makes a nice starting point for your own development. You can always use AX-RadioLAB to modify wireless parameters of your project, even after modifying the firmware.

#### **INSTALLATION**

#### **Software Requirements:**

For AX-RadioLAB to work correctly you need to install the AX8052-IDE first. Install all sub-components of the AX8052-IDE (AXSDB, SDCC, driver, AXCode::Blocks).

Execute the setup.exe to start the installation of AX-RadioLAB. If AX-RadioLAB was already

installed, the installer automatically uninstalls previous versions of AX-RadioLAB. Run setup.exe again to install. At the end of the each process you will be asked to reboot your computer. This is not necessary.

#### **RADIOLAB MAIN PANEL**

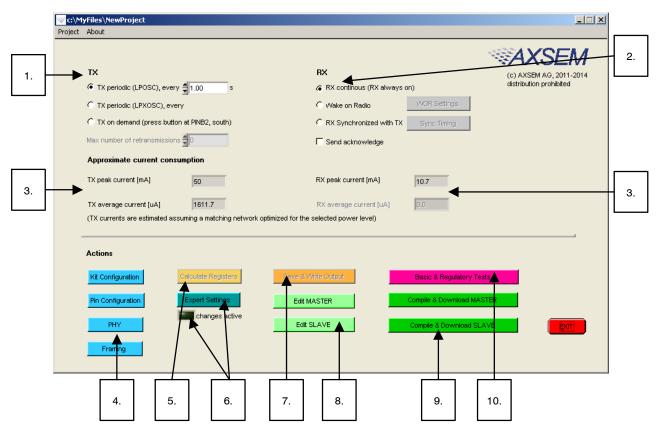

Figure 1. Radiolab Main Panel

Start a new project using the *Project* menu. You have to specify a project directory where AX-RadioLAB will create firmware projects called MASTER, SLAVE and TESTS. to open an existing project use the directory chooser dialog to descend into the project directory (where the axradiolabstate.xml file resides) and hit done.

NOTE: Do not open the template\_firmware\_5043 project inside the AX-RadioLAB installation directory, as this is the template from which the firmware is copied upon creating a new project.

Follow through the main panel step-by-step to configure your project:

- 1. Select the TX Operation Mode:

- TX Periodic (LPOSC): Periodic packet transmission driven by the MCU's low power RC oscillator.

- TX Periodic (LPXOSC):

Periodic packet transmission driven by the MCU's low power 32kHz tuning fork crystal oscillator

- TX on Demand: Packet transmission upon pressing a button.

- Select the RX Operation Mode: RX Continuous (RX always on): Packet reception keeping the receiver continuously

on. This mode is used for AC-powered systems and allows asynchronous packet reception with low latency.

#### • Wake on Radio:

Packet reception with the receiver waking up periodically and going immediately back to sleep if no signal is detected. The wake-up is driven by the AX5043's low power RC oscillator and does not require any MCU activity. The MCU is only woken up once a valid packet has been received. This mode is well suited e.g. for infrequently operated remote control applications and achieves very low (idle) current consumption. *Mind that preambles longer than the time between RX wake-ups are necessary*. The latter also determines the RX latency.

RX Synchronized with TX:

Periodic packet reception enabling the receiver only for the time slots in which packets are expected. This is appropriate whenever periodic data transmission is required. Timing is driven by the MCU's low power 32 kHz tuning fork crystal oscillator and thus requires MCU activity. It

- is mandatory to use *TX periodic (LPXOSC)* on the transmitter side.

- TX and RX modes are summarized in Table 1.

Wake on Radio and RX Synchronized with TX modes are described in more detail in their respective sections

- The MASTER and SLAVE firmware projects are created in your project directory (if not present yet) upon hitting the Save & Write Output button. Manual changes in the firmware projects are never overwritten by the GUI except for the configuration files in your\_projectdir/AX\_Radio\_Lab\_output/.

- The Send acknowledge checkbox causes the slave module ("RX") to answer successful packet reception with an acknowledge packet. The master module ("TX") tries to receive the acknowledge packet. The smiley on the LCD indicates whether the acknowledge packet has been received. Failure is also signaled via LED2. Optionally the MASTER can retransmit a packet if acknowledge fails. This feature is enabled by setting Max number of retransmissions to a nonzero value. The acknowledge mode is the reason why the terminology MASTER and SLAVE (rather than TX and RX) has been chosen. The acknowledge feature can be selected in all TX and RX modes.

- 2. Estimated current consumption is displayed here. The peak current values are drawn when TX or RX are running. For duty cycled modes the estimated average currents are also displayed. in Wake on Radio mode the average RX current is the idle current, assuming a silent channel. in RX Synchronized with TX mode receiving a packet in at each wake-up is assumed. If Send acknowledge is selected the average RX current also includes transmission of the default acknowledge packet and the average TX current includes the corresponding receive current. Currents drawn by TCXO and MCU are not included. TX currents assume a matching network optimized for the selected power level. Mind that the default matching network on the AXSEM RF modules is not optimal for reduced power levels. This leads to reduced power amplifier efficiency and thus currents higher than estimated.

- 3. Buttons to open configuration panels for Kit Configuration, Pin Configuration, PHY layer and Framing. The PHY panel covers physical parameters of the wireless link such as carrier frequency, data rate and the modulation scheme. The Framing panel deals with packet delimiting, CRC etc.

- 4. Calculate Registers calculates register values to configure the AX5043 according to your Pin Configuration, PHY and Framing selections.

- 5. After calculating register values you can optionally tweak values using Expert Settings. Click values in the rightmost column of the Expert Settings panel to edit. Tweaked values are sticky. They keep overriding the defaults even if the defaults have changed (e.g. upon making changes in the PHY panel and hitting Calculate Registers). Tweaked values are highlighted in yellow (or green if they accidentally correspond to the default values). The *changes active* indicator in the main panel reminds you that tweaked values are being used. Double click a tweaked register (column 1, 2 or 3) in order to return to the default value. Hitting Reset Changes at the bottom of the Expert Settings panel or clicking the *changes active* indicator in the main panel drops all tweaks.

- 6. Save & Write Output

- Saves configuration and register values into your projectdir/axradiolabstate.xml, allowing you to reopen your project with AX-RadioLAB.

- Outputs files config.c, configmaster.[ch] and configslave.[ch] to your\_projectdir/ AX\_Radio\_Lab\_output/. These files are included by / linked to the MASTER, SLAVE and TESTS firmware projects.

- The firmware projects MASTER and SLAVE are written into your project directory if they are not present yet.

- 7. The *Edit MASTER* and *Edit SLAVE* buttons open the corresponding firmware project from your project directory using the AXCode::Blocks IDE. This is handy for tweaking the firmware code, but touching the code is not necessary for first experiments with packet transmission. Instead you can download the demo firmware to the MCU directly from AX–RadioLAB (see next point). Button labels adapt to show which firmware projects are currently used.

- 8. The Compile & Download MASTER and Compile & Download SLAVE buttons compile and download the corresponding firmware onto the main board connected to the AXDBG USB debug adapter. Note that Compile & Download does not work if AXCode::Blocks is currently opened. In this case just use Save & Write Output and then compile and download the code from within AXCode::Blocks.

- 9. Opens the *Basic & Regulatory Tests* panel, allowing you to transmit CW, simple patterns or random data and to measure bit error rates.

10. Opens the *Basic & Regulatory Tests* panel, allowing you to transmit CW, simple patterns or random data and to measure bit error rates.

Table 1. SUMMARY of TX AND RX MODES AND CORRESPONDING FIRMWARE PROJECTS.

| Mode, Purpose                                                                                                                             | Used Timer                                                                                                                                                                                                      | Radio/MCU Activity (Note 1)                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| TX periodic (LPOSC),<br>Periodic packet transmission                                                                                      | MCU libmfwtimer infrastructure with timer 0 clocked by MCU LPOSC (640 HZ RC oscillator)                                                                                                                         | MCU periodically wakes up, powers up the TX and initiates packet transmission                                              |

| TX periodic (LPXOSC), Periodic packet transmission (used with RX Synchronized with TX)                                                    | MCU libmfwtimer infrastructure with timer 0 clocked by MCU LPXOSC (32 kHz tuning fork crystal oscillator)                                                                                                       | MCU periodically wakes up, powers up the TX and initiates packet transmission.                                             |

| TX on demand, Packet transmission upon pressing a button or similar event.                                                                | MCU libmfwtimer infrastructure with timer 0 clocked by MCU LPOSC (640 HZ RC oscillator) Only used for generating a timeout in ACK mode                                                                          | MCU wakes up upon pressing a button, powers up the TX and initiates packet transmission.                                   |

| RX Continuous,<br>AC-powered systems (allows<br>asynchronous packet reception)                                                            | MCU libmfwtimer infrastructure with timer 0 clocked by MCU LPOSC (640 HZ RC oscillator) Only used for ACK timing and channel state polling.                                                                     | RX is continuously on. Upon receiving a valid packet it generates an interrupt waking up the MCU.                          |

| Wake on Radio, Remote control (asynchronous packet reception at low idle currents at the expense of long preambles and increased latency) | AX5043 LPOSC (640 Hz RC oscillator) for autonomous wake-up of the AX5043 MCU libmfwtimer infrastructure with timer 0 clocked by MCU LPOSC (640 HZ RC oscillator) Only used for generating a timeout in ACK mode | RX periodically wakes up and checks for signal. Upon receiving a valid packet it generates an interrupt waking up the MCU. |

| RX Synchronized with TX,<br>Low power periodic data transmission                                                                          | MCU libmfwtimer infrastructure with timer 0 clocked by MCU LPXOSC (32 kHz tuning fork crystal oscillator)                                                                                                       | MCU periodically wakes up, powers up the RX and waits for packet reception or timeout.                                     |

<sup>1.</sup> MCU activity apart from timekeeping wake-ups due to the running libmfwtimer infrastructure.

#### Wake on Radio Mode (WOR)

In Wake on Radio mode the receiver periodically wakes up and searches the channel for a signal. in absence of signal the receiver is switched off again immediately in order to save power. If a signal is detected the receiver stays on and looks for a valid packet delimiter. The AX5043 performs this task autonomously. Only after a valid packet

has been received and is waiting in the FIFO, the AX5043 wakes up the micro controller via an interrupt. A typical application of this mode would be an infrequently operated remote control. The "WOR Settings" button opens the Wake on Radio panel:

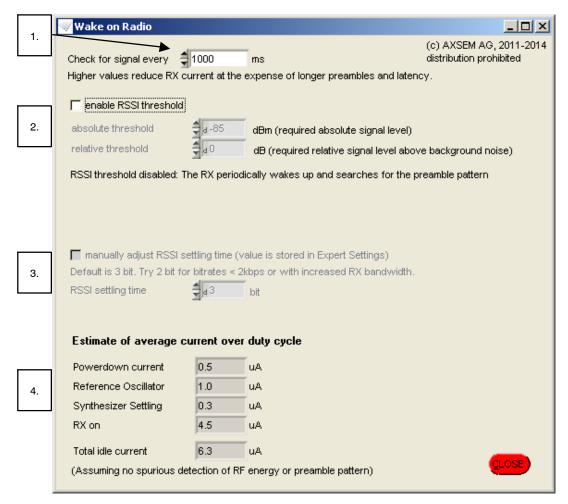

Figure 2. Wake on Radio

- This field configures how often the receiver wakes up and checks for signal. Waking up less often reduces the average RX (idle) current. However, it increases the necessary preamble length and average latency, since the preamble needs to be at least as long as the gap between two successive wake ups.

- 2. The "enable RSSI threshold" option determines how the RX searches for signal upon wake up:

- a. If this option is disabled the RX directly scans for preamble pattern. Sensitivity in this mode is comparable to continuous RX operation.

- b. If this option is enabled the RX first acquires an RSSI value. The scan for preamble pattern is performed only if RF energy is detected. This reduces current consumption (most notably at

- low data rates) since the RSSI measurement is faster than the scan for preamble pattern. The drawback is a reduction of sensitivity, since the RSSI threshold has to be set several dB above the sensitivity limit to prevent false positives. The RX proceeds to scanning for preamble if RSSI > absolute threshold AND RSSI ≥ (background RSSI + relative threshold). Background RSSI is the RSSI average over past wake ups.

- This field allows customization of the RSSI settling time. Longer settling times give more stable RSSI measurements at the expense of higher current consumption. Changes are written to the expert panel.

4. The estimated (idle) RX current is displayed. The fractions for powerdown current, reference oscillator settling, synthesizer settling and RX on (RSSI acquisition or scan for preamble) are displayed separately.

Make Sure You Understand the Following Points:

- An important part of the process of powering-up the receiver and deciding whether a preamble signal is present takes a time inversely proportional to the data rate. to achieve minimum current consumption you should therefore use the maximum possible data rate (100 kbps). The time the receiver searches for a preamble signal can be customized via the TMGRXPREAMBLE1 register in the expert panel.

- Frequency tracking (AFC) requires settling time, which adds to the receiver start-up time and therefore increases the average current consumption. Large data rates and precise frequency references render frequency tracking unnecessary.

- The average receiver (idle) current is proportional to the wake up frequency. On the other hand in the remote control mentioned above, the wake up frequency determines how quickly the receiver will react.

- Mind that the current estimate displayed in the main panel is the idle current in absence of a signal. Thus while the RX wakes up periodically, actual packet reception is the exception in this mode, occurring only e.g. if a remote control button was pressed. This is in contrast to the *Synchronized with TX* mode, in which a packet is expected each time the RX wakes up.

#### **RX Synchronized TX Mode**

The purpose of RX Synchronized with TX mode is periodic reception of packets with minimal current consumption by enabling the RX only for the time slots in which packets are expected. Short preambles can be used on the TX side . The following points explain how the RX Synchronized with TX mode works:

- RX Synchronized with TX mode is used together with TX periodic (LPXOSC) on the TX side. Timing is driven by the MCU's low power 32 kHz tuning fork crystal oscillator which ensures an accurate packet frequency and thus allows for tight margins in the time slots in which the RX in enabled.

- After power-up LPXOSC is settled and the RX is switched continuously on until a packet is received or a timeout occurs. LED3

- indicates the RX is running. When a packet is received the RX is put to sleep and only wakes up again for the time slot in which the next packet is expected.

- With each further packet reception the RX measures the effective time elapsed since the last packet and (via low pass filtering) corrects its own wake-up frequency accordingly. This corrects for crystal variations as well as temperature differences and slow gradients, and minimizes required margins in the RX-on time slots. (An increased margin is used for the packet reception right after synchronization, where the effective period has not been measured yet.)

- If no packet is received during an RX-on time slot, the RX margins are increased for the next time slot. If no packet is received during N subsequent time slots, the RX module switches back to synchronization mode, i.e. the RX is switched on continuously until a packet is received or a timeout occurs. (This synchronization mode is the same as for initial synchronization after power up. The only difference lies in the timeout interval: a timeout (in seconds) can be configured for initial synchronization after power-up (e.g. time to put batteries into the TX module). A second timeout (in packet periods) applies for re-synchronization after loosing multiple packets in a row.

- If re-synchronization fails, (no packet is received until the timeout), the RX module is put to sleep for a configurable, typically long, period before trying to synchronize again. The rationale here is to limit RX power consumption in the case where the TX is off or out of reach.

- In RX Synchronized with TX the LCD displays the usual packet information. Pressing and holding button SW03 (south button on DVK-2 mainboards, connected to PINB2) during packet reception switches to the packet timing information display:

- ◆ "T:" is the current, low pass filtered packet period deviation measured in LPXOSC periods. Thus it indicates by how much the interval between packets is (on average) longer than programmed value from the perspective of the RX. It is understood, that the position of the next time RX on time slot is corrected by this deviation. Thus if TX and RX clocks run at slightly different but constant speeds, the corresponding

- timing deviation is displayed here, but the RX on time slots are perfectly aligned to the actual packets.

- "t:" indicates by how many LPXOSC cycles the last packet was late compared to the expected time, i.e. by how much it was misaligned to the RX on time slot.

After acquisition of "T:" nonzero values of "t:" are due to timing fluctuations, which have fit into the configured RX margin.

The *Sync Timing* button opens the Sync Timing panel, where various timing parameters can be configured.

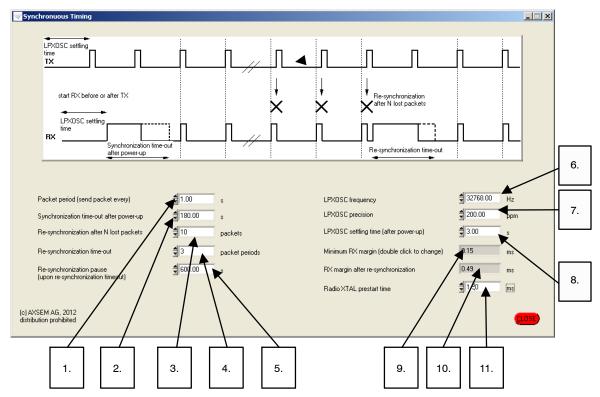

Figure 3. Synchronous Timing

- 1. Packet Period (Send Packet Every):

This is simply a duplicate of the *TX periodic* (*every*) field in the main panel for convenience.

- 2. Synchronization Time-Out After Power-up: Time the RX tries to receive the first packet, before temporarily giving up and switching to re-sync pause mode. E.g. this is the time you have to put batteries into the TX module after powering up the RX.

- Re-Synchronization After N Lost Packets:

Determines in how many subsequent

RX-on time slots packet reception can fail before the RX switches to back to synchronization mode.

- 4. Re-Synchronization Time-Out:

Time the RX tries to receive a packet for re-synchronization before temporarily giving up and switching to re-sync pause mode.

- Re-Synchronization Pause (Upon Re-Synchronization Time-Out):

Time for which the RX sleeps after failing to re-synchronize before trying again.

- 6. LPXOSC Frequency:

Frequency of the low power tuning fork crystal oscillator.

- 7. LPXOSC Precision:

Precision of the low power tuning fork crystal oscillator.

- 8. LPXOSC Settling Time (After Power-Up): TX as well as RX modules wait for this time before transmitting / trying to receive packets. This is to prevent synchronization and period measurement with an insufficiently settled clock source.

- 9. Minimum RX Margin:

RX margin determines how long the RX

is running, before the expected packet start. The

same margin is also used as a timeout: The RX

is powered down if no frame delimiter is detected

by the time it was expected plus RX margin. (RX

running means synthesizer running and analog

baseband settled, but no AGC, AFC and bit

synchronization, since there is no signal yet.) The

minimum value specified here has to accommodate timing fluctuations in normal operation. A default value is computed from packet period and LPXOSC precision. Double click the field to change it manually. If packet reception fails in a given RX—on time slot, the firmware automatically increases the margin for the next time slot.

10. RX Margin After Re-Synchronization:

An increased RX margin which is used for the RX-on time slot right after re-synchronization.

This is necessary, since re-synchronization only aligns the phases of periodic TX and RX. The RX needs a further packet to measure and adjust the wake-up period. Therefore the margin of the first RX-on time slot has to be large enough for the full, uncorrected timing deviation.

Radio XTAL Pre-Start Time:

Determines how long the XTAL reference oscillator of the radio chip is settled before the RX synthesizer is started.

#### KIT CONFIGURATION PANEL

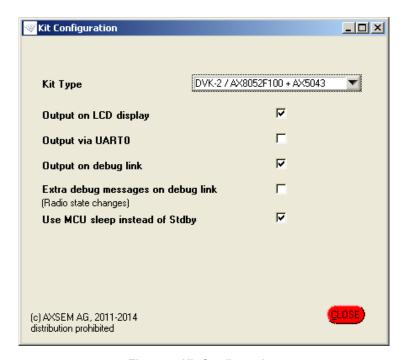

Figure 4. Kit Configuration

In the Kit Configuration panel you can select the type of debug kit and the display options being used<sup>1</sup>

Available Options:

Kit Types:

DVK-2/AX8052F100 + AX5043 and F143-MINI-DVK /AX8052F143. in case of F143-MINI-DVK the LCD output and all synchronous transfer modes are not available due to missing LCD display and 32 kHz watch crystal.

Output on LCD Display:

Packet numbers, bit and packet error rates, RSSI and other information is display on the LCD display of the DVK-2b Output on UART0:

Instead of sending the information to the LCD display it

is send to UARTO. This is the display mode for the MINI-DVK.

The Usage of LCD and COM0 are mutually exclusive.

Output on Debug Link:

In addition to one of the displays, the information is also send to the debug link.

Extra Debug Messages on Debug Link:

This option produces extra information about the status change of the radio state on the debug link.

*MCU sleep instead of Stdby:* option decides if the MCU uses sleep mode instead Stdby mode.

<sup>&</sup>lt;sup>1</sup> Bypassing the encoder is achieved by setting the UNENC flag corresponding FIFO DATA chunk. This causes the chunk data to bypass manchester, scrambler and differential encoder, however inversion still applies. For convenience AX–RadioLab therefore inverts preamble and SYNC WORD bytes before writing them to the firmware code if "unencoded" and INV encoding are selected.

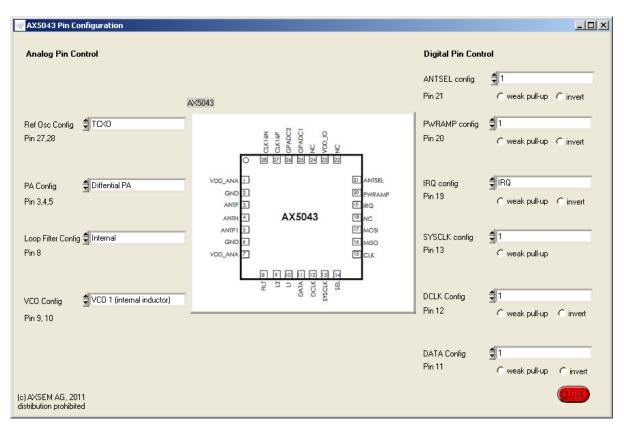

#### PIN CONFIGURATION PANEL

Figure 5. Pin Configuration

- Ref Osc Config: select XTAL or TCXO

- PA Config: select differential, single ended or both power amplifier(s)

- Loop Filter Config: determines whether the internal or an external PLL loop filter is used.

- VCO Config: Select VCO 1 (fully integrated VCO with on-chip inductor), VCO 2 (using an external inductor), or an entirely external VCO

- ANTSEL Config:

Pin can output TCXO enable signal, signal of the integrated DAC or Diversity Antenna Select. in the AX8052F143 SOC ANTSEL functionality is available on the PB3 GPIO pin.

- PWRAMP Config:

Pin can output signal of the integrated DAC,

Power Amplifier Control or TCXO enable signal. in the AX8052F143 SOC PWRAMP functionality is available on the PB2 GPIO pin.

- IRQ Config:

Output IRQ. No other setting is sensible if the AX5043 module is connected to the AXSEM main board.

- IRQ Config: use Modem Data Clock Output when observing when observing modem data on the DATA pin.

- IRQ Config:

I/O Modem Data; I/O Async Modem Data;

Output Modem Data (In this mode, during RX the received data appears on DATA. During TX data is transmitted from the FIFO but echoed on DATA.)

#### **PHY PANEL**

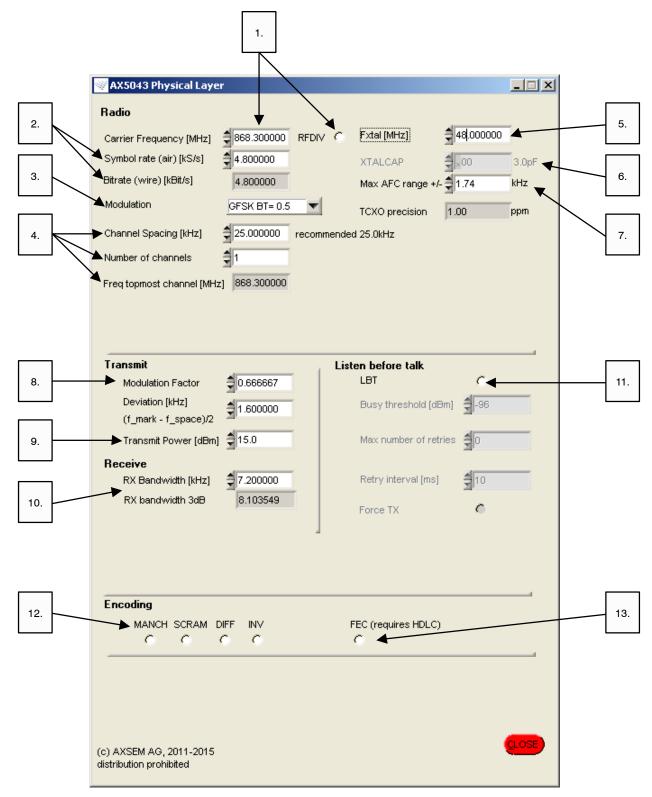

#### Overview

Figure 6. Physical Layer

- 1. Select Carrier Frequency. If more than one channel is configured (see below) the frequency selected here is that of channel number 0. RFDIV indicates that the VCO is running at 4 times the LO frequency, rather than 2 times (depending on the frequency band). This is an indicator only unless you are using an external inductor and the selected frequency can be reached in both ways (using a different inductor value, of course).

- 2. Symbol rate & Bitrate specify the data rate. The values are identical except when using Manchester encoding (bitrate = 0.5\*symbol rate) or 4-FSK (bitrate = 2\*symbol rate).

- 3. Modulation Scheme.

- 4. Width of your channel. Red values signal a conflict with the TX and / or RX bandwidth. A number of channels can be specified. The firmware determines and stores the VCO range for each channel at startup. The carrier frequency of the topmost channel is displayed for convenience.

- Frequency of the reference oscillator (XTAL / TCXO).

- 6. XTALCAP adjusts the on-chip XTAL load capacitance. Set to 0 when using a TCXO.

- 7. Max AFC range ±: This value determines how far the frequency tracker (AFC) can walk in either direction. Setting it to zero disables frequency tracking. The necessary TXCO (or XTAL) precision is displayed. The computation is TOXO precision = (max AFC range)/(2\*f<sub>carrier</sub>) (eq. 1) ensuring that the tracking range is sufficient to handle the case, where the TCXO of the TX and RX are maximally off in opposite directions.

For more details and recommendations on setting up the AFC range and FSK deviation see XTAL/TCXO Precision Frequency Tracking and Bandwidth

NOTE: Increasing the range of the AFC allows for the use of a less precise TCXO or XTAL. However, the drawbacks are:

- a. Longer preambles may be necessary to settle the AFC. in WOR and RX Sync mode this enlarges the necessary receive windows and thus the duty cycled receiver current consumption.

- b. Larger RXBW may be necessary, since for successful tracking a sufficient amount of TX spectrum needs to fall into the RXBW.

A warning is displayed if this is not guaranteed. See dedicated paragraph and figure below for details.

- 8. Modulation factor (often denoted as h).

```

FSK deviation = 0.5 * modulation factor * Symbol rate

= (f_mark - f_carrier)/2 (eq. 2)

```

sometimes called half deviation.

4-FSK: Symbols are:

f carrier +  $\{-3, -1, +1, +3\}$ \*deviation

- 9. Transmit power in dBm

- 10. Bandwidth of the RX channel filter, the upper field is used to input the desired value, the lower field shows the actual value.

- 11. Listen Before Talk (LBT) Option:

The TX measures the channel RSSI before sending a packet in order to assess whether the channel is free. If the RSSI value is found to above the busy threshold the TX can retry a number of times. If the channel continues to be busy the TX can either give up or transmit anyway (force TX).

- 12. Encoding: Manchester, scrambler, differential and inversion.

- 13. Forward Error Correction (FEC). This encoding transparently adds redundancy to the transmit data in order to make it more immune against noise. FEC can only be used together with HDLC framing and it is mandatory use HDLC flags (0x7E) as preamble characters. Other encoding modes such as SCRAM are not allowed and unnecessary in FEC mode, since FEC leads to data whitening by itself.

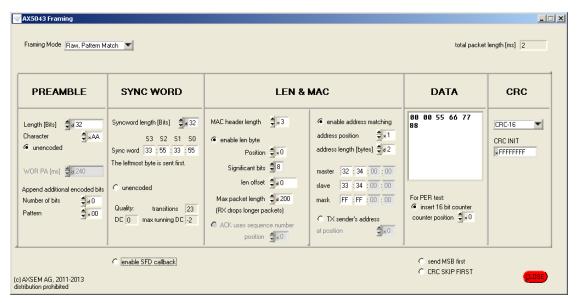

Figure 7. Framing

#### Framing Mode:

Options are HDLC, Raw Pattern Match and PN9 Compatibility. in Raw Pattern Match mode an arbitrary SYNC WORD of up to 32 bit marks the beginning of a frame. For legacy systems the PN9 Compatibility mode implements PN9 data whitening in software, based on the AX5043's Raw Pattern Match mode.

#### Preamble:

- Recommended default settings are chosen according to the selected modulation, encoding and precision of the reference clock.

- Specify the length of the preamble in bits, as well as one byte character which will be repeated length/8 times.

- The preamble character is always sent MSB first, irrespective of the "send MSB first" option in the DATA chunk. See comment on that option below.

- If length is not an integer multiple of 8, the fractional byte is sent last, e.g. for length = 33 bits the preamble character is sent 4 times followed by once the MSB of the preamble character.

- The "unencoded" option causes the preamble character to bypass the Manchester, scrambler, differential and inversion encoder. (See footnote to SYNC WORD for technical details about inversion.)

- In Wake on Radio mode an additional WOR preamble length (in ms) can be specified. This chunk is transmitted in addition to the number of bits specified above. The length of this chunk should not be shorter than the WOR period.

Occasionally it may be necessary to conclude the preamble with a few special bits. This can be achieved using the fields below "Append additional encoded bits".

#### SYNC WORD

- In Raw Preamble Mode you can choose an arbitrary sync word of up to 32 bit as a start of frame delimiter. However it is recommended to use a sync word with well peaking auto correlation function.

- The SYNC WORD is always sent MSB first, irrespective of the "send MSB first" option in the DATA chunk. See comment on that option below.

- The "unencoded" option causes the SYNC WORD to bypass the manchester, scrambler, differential and inversion encoder.<sup>2</sup>

Correspondingly the RX matching unit detecting the SYNC WORD will operate on the bit stream before

- DC content, running DC content and the number of transitions are computed in order to indicate the quality of the selected SYNC WORD. Large DC or running DC components can impede correct frequency tracking, whereas a low number of transitions slows

- Selecting the "enable SFD callback" option causes the AX-RadioAPI to notify the application level firmware each time a start of frame delimiter (a SYNC WORD or a HDLC flag) has been received.

down time tracking.

<sup>&</sup>lt;sup>2</sup> Bypassing the encoder is achieved by setting the UNENC flag corresponding FIFO DATA chunk. This causes the chunk data to bypass manchester, scrambler and differential encoder, however inversion still applies. For convenience AX–RadioLab therefore inverts preamble and SYNC WORD bytes before writing them to the firmware code if "unencoded" and INV encoding are selected.

#### LEN & MAC

- "MAC header length" specifies the length of the packet header, which can contain a length byte, a sequence number for acknowledge and addresses.

- In Raw Pattern Match mode a length byte can be used to communicate the length of the current packet to the RX. Alternatively (uncheck "enable len byte") the RX can be configured to expect packets of a fixed length.

- "Position" determines the position of the length byte inside the packet header. Zero means the length byte follows immediately after the SYNC word.

- "Significant bits" tells the RX how many bits of the length byte are used to encode the packet length. This is useful if your protocol uses a shared byte to encode the packet length plus something else.

- "len offset": The actual packet length (excluding SYNC WORD & CRC) assumed by the RX is len + len offset.

E.g. set len offset to zero if in your protocol the length byte counts the number of bytes including the length byte. Set len offset = 1 if your length byte counts the number of bytes excluding the length byte itself.

Negative values for "len offset" are allowed.

- If you check "enable len byte" in HDLC mode, the TX will send a length byte but it will be ignored by the RX.

- Specifying a maximum packet length can limit the impact of bit errors in the length byte.

- If the acknowledge feature is used an ACK sequence number field can be configured. This is not mandatory for acknowledge to work. However, without this field the SLAVE cannot detect duplicate packets occurring if packet RX has worked but the ACK packet got lost, causing the MASTER to retransmit the packet.

- Specify a device addresses of up to 4 bytes and a corresponding address mask in order to restrict reception to packets containing a matching address.

- "address position" specifies the starting position of the address inside the packet. Zero corresponds to the byte immediately after the SYNC WORD / HDLC flag.

- Optionally the sender's address can be added to the header. Note that address works on the destination address field (containing the slave's address in normal MASTER to SLAVE communication and the master's address for packets sent from SLAVE to MASTER, e.g. ACK packets in the demo firmware.)

#### DATA

- The DATA field allows you to specify a static sample payload which will be used by the demo firmware. Enter each byte as a two digit hex number (without leading 0x). Bytes may be separated by spaces.

- Optionally the firmware can insert a 16 bit counter into the data field at a specified position. This allows the RX to count the number of lost packets. The two bytes reserved for this counter are displayed as "00 00" in the data field.

- Checking the "send MSB first" button causes each byte in the DATA field to be sent MSB first. Otherwise each byte is sent LSB first.

- Note, however, that preamble character and SYNC WORD are always sent MSB first. (Technically, the RF chip will be configured to operate in MSB first or LSB first mode according to the "MSB first button", which applies to every byte. However, in LSB first mode the AX–RadioLAB GUI reverses the entered preamble and SYNC WORD bytes in order to keep the representation in the GUI MSB first. The reason for this is, that the byte and nibble order of a SYNC WORD written left to right but read LSB first can be confusing.)

- "CRC SKIP FIRST" causes the first byte of the packet to be excluded from CRC calculation.

#### CRC

- Select CRC algorithm and initial value.

- The CRC is automatically calculated by the RF chip and appended to the packet. in HDLC mode the RX will store the received packet including CRC bytes. in Raw Packet Match mode, the RX strips the CRC bytes unless you manually set bit 5 in the AX5043\_PKTSTOREFLAGS register.

- Packets with incorrect CRC are silently dropped unless you manually set bit 2 in the AX5043 PKTACCEPTFLAGS register.

#### **BASIC AND REGULATORY TESTS PANEL**

Figure 8. Basic and Regulatory Tests

- "Set CW" puts the RF chip to TX CW mode.

- "Set Pattern" transmits the specified 8 byte pattern forever. The byte specified by the two leftmost digits is sent first. Each byte is sent LSB first unless the "send MSB first" button in the framing panel is checked. Manchester, scrambler and differential encoder are bypassed (inversion encoding applies if selected!).

- "Set Random" transmits pseudo-random data forever. (This is realized using the scrambler.)

- "RX 1010" performs measurement of bit error rate (BER). Typically connect the RX to a signal generator sending an infinite 1010 stream, i.e. in FSK mode the generator should toggle between {+1, -1}\*half deviation. in 4-FSK mode, the pattern {-3, -1, +1, +3}\*half deviation should be applied. The BER value can be measured with 3, 4 or 5 digit precision.

- "TX 1010" transmits an infinite 1010 stream suitable for "RX 1010" BER measurement.

- "RX PN9", "TX PN9", "RX PN15", "TX PN15", "RX PN17", "TX PN17" are similar to "RX 1010" and "TX

- 1010", except that the BER measurement is performed using a pseudo-random data stream. in PN9 mode, the data stream is generated using the polynomial  $x^9+x^5+1$ , in PN15 mode, the polynomial  $x^{15}+x^{14}+1$  is used, and in PN17 mode, the polynomial  $x^{17}+x^{12}+1$  is used.

- "Output RX via DATA pin" allows observation of the received data via the DATA and DCLK pins. This is intended for performing BER tests where the bit errors are recorded by measurement equipment connected to the DATA and DCLK pins<sup>3</sup>. It is recommended to use measurement equipment which evaluates both, DATA and DCLK, since DATA can exhibit considerable jitter.

- This mode can be used for any kind of input data, 1010 data or pseudo random data streams. The raw received data is output on the DATA pin. Note, however, that the BER displayed on the LCD is correct only for 1010 data.

- Edit TESTS opens the firmware implementing the above test modes in the AXCode::Blocks IDE.

<sup>&</sup>lt;sup>3</sup> The "RX1010", "RX PN9", "RX PN15" and "RX PN17" modes periodically settle the receiver with aggressive settings of the receiver tracking loops (RX parameters set 0) and then switch to the less aggressive settings (RX parameter set 3), where for instance the AGC loop is frozen completely. This is similar the situation of packet reception, where RX parameter set 3 is used after detection of a SYNC WORD. When measuring the bit error rate with external instrumentation this approach cannot be used. Receiving with RX parameter set 0 may lead to an increased bit error rate, while permanently receiving with RX parameter set 3 would not allow the AGC to settle. The "Output RX via DATA pin" therefore uses a variant of RX parameter set 3 where the AGC is running, typically with 1/4 of the bandwidth of the RX parameter set 0 settings.

#### **COMMENTS ON C-CODE FIRMWARE**

#### **File Structure**

The MASTER and SLAVE and TESTS firmware projects implement the corresponding modes using the AXRADIO V2 API as a "driver" for the AX5043 RF chip.

Table 2. THE AX RADIO V2 API CONSISTS of THE FOLLOWING FILES

| File                         | Description                         |

|------------------------------|-------------------------------------|

| COMMON/axradio.h             | AXRadio API declaration             |

| COMMON/easyax5043.h          | AXRadio AX5043 private header       |

| COMMON/easyax5043.h          | AXRadio AX5043 main code            |

| AX_Radio_Lab_Output/config.c | Parameters generated by AX-RadioLAB |

It is documented in DOCU/AXRadioV2API.pdf

Table 3. THE APPLICATION LEVEL CODE CONSISTS of THE FOLLOWING FILES:

| File                                      | Description                                           |

|-------------------------------------------|-------------------------------------------------------|

| MASTER/main.c                             | MASTER application level main code                    |

| SLAVE/main.c                              | SLAVE application level main code                     |

| TESTS.main.c                              | TESTS application level main code                     |

| COMMON/misc.[ch]                          | Application level helper files                        |

| SLAVE/display.c                           | Application level helper file                         |

| SLAVE/lposc.c                             | Helper file                                           |

| AX_Radio_Lab_output/<br>configslave.[ch]  | Application level parameters generated by AX-RadioLAB |

| AX_Radio_Lab_output/<br>configmaster.[ch] | Application level parameters generated by AX-RadioLAB |

#### **Define Statements for Tweaking Firmware**

#define ADJUST\_FREQREG (SLAVE/main.c) if defined, after successful packet reception the receiver frequency is adjusted according to the tracked frequency offset. The frequency is not adjusted by the entire tracked frequency offset at once. Rather low pass filtering is applied. Low pass filtering is controlled by FREQOFFS\_K, higher values give slower adjustments.

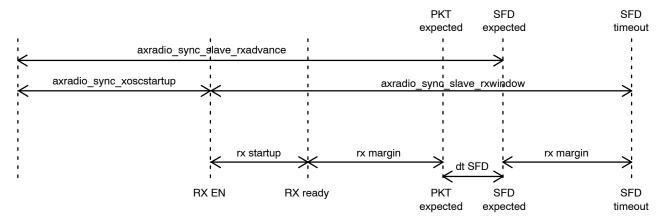

#### **SYNC Packet RX Timing**

In the AX-RadioLAB SYNC RX mode timing is controlled by the parameters axradio sync xoscstartup axradio sync slave rxadvance axradio sync slave rxwindow and axradio sync slave rxtimeout and axradio \_sync\_slave\_rxtimeout. All times are measured in periods of libmf wtimer0, which is clocked by the low power crystal oscillator. As shown at the top of Figure 1 the radio XTAL oscillator of the SLAVE is enabled axradio sync slave rxadvance before the frame delimiter (SFD) of the next packet is expected. After settling the XTAL for axradio\_sync\_xoscstartup the RX is enabled. The RX then settles and looks for an SFD, time outing after axradio sync slave rxwindow if no SFD is received. If an SFD is received the RX stays on until successfully receiving a packet or until a timeout occurs after axradio sync slave

rxtimeout. (Not shown in the figure.)

Figure 9. SYNC Firmware Packet Reception Timing

AX-RadioLAB computes axradio\_sync\_slave\_rxadvance and axradio\_sync\_slave\_rxwindow based on the rx\_margin which can be configured in the SYNC Timing panel as shown at the bottom of Figure 9. The goal is to have the RX ready rx\_margin before the expected start of the packet. (Ready means that the synthesizer and the analog baseband are settled. AGC settling and bit synchronization

can be done only if preamble signal is present.) The SFD timeout is set rx\_margin after the expected SFD. Three instances of axradio\_sync\_slave\_rxadvance and axradio\_sync\_slave\_rxwindow are computed. The first instance contains the increased rx\_margin to be used for the first packet after (re-)synchronization when the effective packet period measurement is available yet. The second instance

contains the rx\_margin used in normal operation ("Minimum RX margin" in the SYNC Timing panel). The third instance has rx\_margin scaled by a factor of 4 and is used after a failed packet reception.

NOTE: A processing delay occurs in the RX, i.e. the detection of the SFD is not signalled by the RX the very moment it is on air. On the other RX should be enabled *rx\_margin* before the packet is on air. Therefore *dt\_SFD* is not simply the length of preamble plus SFD but also contains the processing delay of roughly 19 bit.

#### XTAL/TCXO PRECISION, FREQUENCY TRACKING AND BANDWIDTH

This section gives some recommendations and background information on how to setup the PHY panel.

# Case 1: How to Set up AFC Range, FSK Deviation and RX Bandwidth

If XTAL/TCXO precision, bit rate and carrier frequency are given, how should the FSK deviation and the RX bandwidth be set to achieve maximum sensitivity?

Step 1

Set Carrier frequency and bitrate. Set Max AFC range so that XTAL/TCXO precision matches the precision of the crystal of TCXO being used. Note that changes over temperature of the XTAL/TCXO should be included.

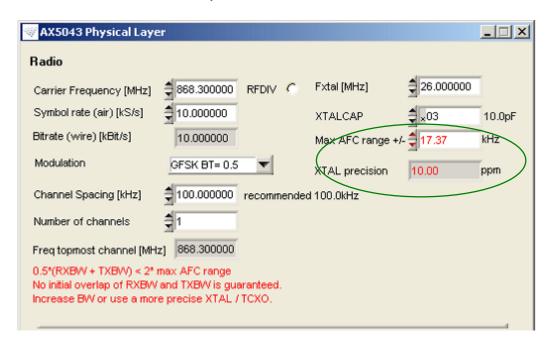

Figure 10. 868.3 MHz, 10 kbps FSK, 10 ppm XTAL Precision Example for Step 1 of PHY Setup

Step 2

Set RX Bandwidth to 2 • Max AFC Range

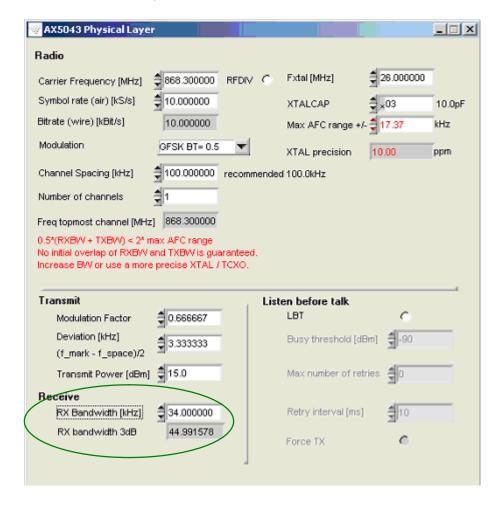

Figure 11. 868.3 MHz, 10 kbps FSK, 10 ppm XTAL Precision Example for Step 2 of PHY Setup

Step 3

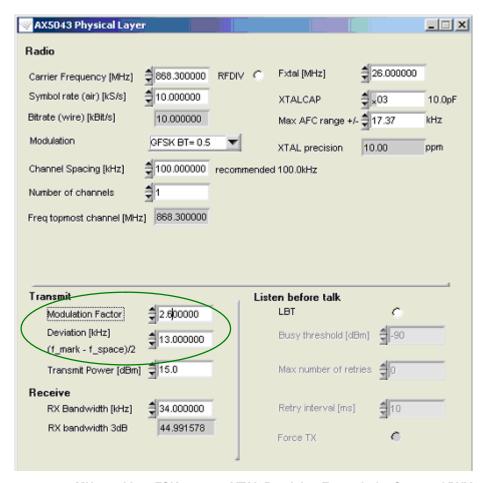

Increase the TX modulation factor or the deviation until the field XTAL precision is no longer red. This is typically at a value

$$Modulation\_Factor = \frac{2 \cdot Max\_afc\_range}{Bitrate} - 1 \quad \text{(eq. 3)}$$

If a modulation factor value larger than 5 emerges, then it is strongly recommended to increase the bitrate and to redo the setup procedure.

Figure 12. 868.3 MHz, 10 kbps FSK, 10 ppm XTAL Precision Example for Step 3 of PHY setup

#### Case 2: Bitrate and Carrier Frequency and FSK Deviation are Given

If the bitrate, carrier frequency and FSK deviations are given, how should the RX Bandwidth be set to achieve maximum sensitivity and what is the XTAL/TCXO precision that is required for this to work?

#### Step 1

Set carrier frequency, bitrate and FSK deviation or modulation factor.

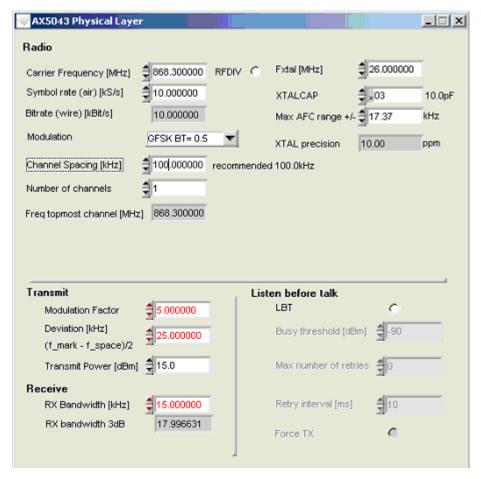

Figure 13. 868.3 MHz, 10 kbps FSK, Modulation Factor 5 Example for Step 1 of PHY Setup

Step 2

Set the RX bandwidth to: (1 + Modulation\_Factor) • bitrate. If necessary increase the XTAL/TCXO precision by decreasing the Max AFC range until the red warning (No initial overlap of RX BW and TX BW is guaranteed.)

disappears. This will occur at a Max AFC range value of RX BW/2.

If your XTAL/TCXO is not precise enough then increase the RX BW, but note that this will come at the cost of lower sensitivity.

Figure 14. 868.3 MHz, 10 kbps FSK, Modulation Factor 5 Example for Step 2 of PHY Setup

#### **Background Information**

Without frequency tracking the worst case frequency deviation between RX and TX is

$$\Delta f = f_{carrier} \cdot (ppm_{TX} + ppm_{RX})$$

(eq. 4)

where  $ppm_{TX}$  and  $ppm_{RX}$  are the precisions of the crystals used in the transmitter and the receiver. The frequency tracker must be allowed to track this deviation, thus the "MAX AFC range" field in the AX–RadioLAB PHY panel (15) should be set to this value,

Max AFC Range =

$$\Delta f = f_{carrier} \cdot (ppm_{TX} + ppm_{RX})$$

(eq. 5)

NOTE: AX-RadioLAB performs the inverse calculation. Given Max AFC Range, the necessary crystal precision is displayed.

AX-RadioLAB assumes identical crystals are used in RX and TX, thus the displayed value is

XTAL precision =

$$(ppm_{TX} + ppm_{RX})/2$$

(eq. 6)

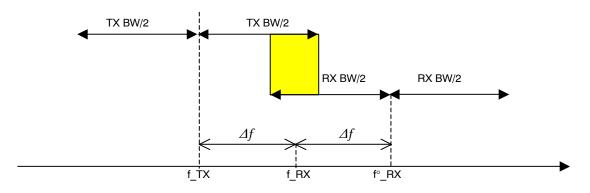

The above setting allows the tracker to walk away  $\Delta f$  in the wrong direction while there is no signal (see Figure 15). In the worst case the receiver frequency can therefore be

$f^{\circ}$ \_RX when packet transmission starts, that is  $2 \cdot \Delta f$  away from f\_TX. For successful tracking a fraction of the TX spectrum should fall into the RX BW. Thus the yellow shaded region should be non-empty:

$$(TX BW + RX BW)/2 \ge 2 \cdot \Delta f$$

(eq. 7)

AX-RadioLAB issues a warning if this constraint is not fulfilled. Inserting

$$RX BW = TX BW = (1 + h) \cdot BR = BR + 2 \cdot deviation (eq. 8)$$

into the overlap condition leads to

$$h_{min} = \frac{2 \cdot \Delta f}{BR} - 1$$

(eq. 9)

Irrespective of the overlap condition  $h \ge 0.5$  is required. For optimal sensitivity

$$RX BW_{opt} = (1 + h) \cdot BR$$

(eq. 10)

should be chosen. If values h > 5 emerges, increasing the bitrate should be considered as the RX BW for large h values has to be increased beyond RX BW<sub>opt</sub> to achieve stable operating conditions.

Figure 15. Frequency Precision, Tracking and Bandwidth

NOTE: By default, AX-RadioLAB generated firmware adjusts the programmed receiver frequency upon successful packet reception. This feature can be disabled by commenting out the #define ADJUST\_FREQREG statement in SLAVE/main.c.

ON Semiconductor and ware trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify an

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative