卓越的模拟性能:Treo平台验证了高性能与高精度

四月 09, 2025

Share:

半导体行业正以前所未有的速度发展,这主要受到人工智能(AI)、5G网络、电动汽车(EV)、工业自动化、消费电子和医疗电子等领域对尖端电子产品需求的推动。为了保持领先地位,设计人员不断挑战芯片设计的极限,力求实现更小、更节能和更高性能的解决方案。在电动汽车、由AI驱动的数据中心、医疗设备和制造业等行业中,芯片性能的微小提升都可能转化为显著的竞争优势。

功耗、性能和面积

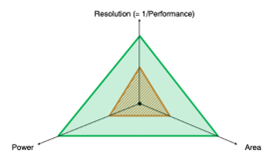

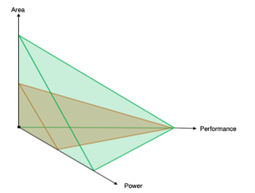

随着技术的进步,对更紧凑、更强大的半导体解决方案的需求也与日俱增。 设计人员必须平衡几个关键因素,包括性能、功耗和尺寸,统称为 PPA(功耗、性能和面积)指标。 这一指标在选择半导体元件和工艺技术以满足不断变化的市场需求方面起着关键作用。 作为一个纯数字,PPA 指标(FoM)通常表示为:

此外,PPA 指标也可以用三角形图(2D)或金字塔图(3D)来表示。

低功耗、高性能(或最小分辨率,以 mV/LSB 表示)以及更小的硅片面积通常被用来衡量电路或工艺技术的竞争力。在电路设计过程中,这三个变量通常需要相互权衡,其中一个变量的改进往往会对另一个变量产生负面影响。 问题是,以 PPA 作为衡量标准,采用下一代工艺技术能在模拟电路中可以实现哪些整体改进?

深入了解 PPA: TND6465 - Treo 平台带来出色的精密模拟

Treo 平台的技术飞跃:65 nm BCD 与 180 nm CMOS 的对比

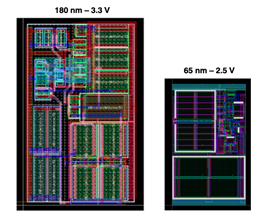

为了应对这些挑战, 安森美(onsemi)推出了 Treo 平台,这是一款尖端的半导体技术平台,旨在支持下一代模拟和混合信号产品。Treo 基于 BCD(Bipolar-CMOS-DMOS)技术构建,与现有的 BCD 平台不同,Treo 提供了业界领先的 1V 至 90V 电压范围,实现了卓越的集成度、更低的功耗和领先行业的效率。与较早的 180nm CMOS 技术相比,通过利用 65nm 工艺技术,安森美显著提升了半导体设计能力。

Treo 平台的 65nm BCD 技术具有多项关键优势,包括:

- 能效提升: 栅极氧化层厚度的减少降低了电源电压(2.5V 对 3.3V 或 5.0V),从而可节省高达 25% 或 50% 的功耗。 实际的功耗降低可能因电流消耗减少而有所不同,甚至可能超过这一数值。

- 缩小尺寸: 从 180 nm缩小到 65 nm工艺技术,可显著减少低压模拟电路的面积。

- 性能提升: 通过改进晶体管匹配和缩小几何尺寸,基于 Treo 的解决方案在相同的功耗下实现了更高的精度和更大的带宽。

- 无缝高压集成: Treo 可将高压元件嵌入芯片本身,从而无需外部电源模块,简化了设计复杂性。

案例研究: Treo 在运算放大器电路中的优势

为了展示Treo平台的优势,安森美对采用180nm CMOS工艺设计的两级米勒运算放大器与其移植到Treo 65nm BCD平台的版本进行了直接对比。

为确保性能相当,移植过程中仔细处理了失调电压、带宽、相对输入共模范围等关键参数。流片后对两种电路进行特性测试,最终验证了移植至Treo工艺带来的性能提升。

结果清楚地表明,在 Treo 平台上开发的设计具有显著优势:

- 功耗: 降低了 2.2 倍,这意味着新设计的功耗不到旧设计的一半。

- 芯片面积: 减少 43.1%,硅片使用率提高 2.32 倍。

- 整体 PPA 品质因数 (FoM): 基于 Treo 的设计性能是 180nm 版本的 5.1 倍。

这些改进不仅提高了效率,还使设计人员能够在更小的器件中集成更多的功能和性能,从而使下一代半导体产品更具竞争力和成本效益

结语

半导体行业正处于一个关键转折点,对更高效率、更小尺寸和更优性能的需求不断增长。安森美的Treo平台凭借其先进的65nm BCD技术,代表了这一领域的重大飞跃,与传统的模拟和混合信号解决方案相比具有显著优势。

在强大供应链和尖端制造技术的支持下,Treo平台将重新定义半导体行业的格局,提供高效节能且高性能的芯片,推动下一波技术创新。无论是在人工智能、汽车、医疗还是工业应用领域,Treo正在为一个更智能、更互联的世界铺平道路。

Additional Resources

TND6465 - High Performance, Precision Analog Capability Enabled by the Treo Platform

TND6464 - High Temperature Analog and Mixed‐Signal Solutions Enabled by the Treo Platform