FPGA至ASIC转换

为什么要转换?

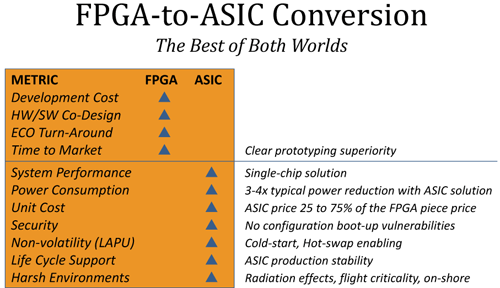

在过去几十年里,安森美已经成功地将成千上万的设计从高成本的FPGA转换为高效的ASIC。ASIC单位成本更低一直是推动转换需求的重要因素。然而,FPGA到ASIC的转换不仅仅是为了成本节约。 ASIC替代FPGA,还能够显著降低功耗,极大延长电池寿命。与FPGA中使用的可编程逻辑相比,ASIC 中逻辑的硬编码不支持器件进行再编程,从而提升了安全性和可靠性。这种更高的可靠性使得 ASIC成为航空飞行应用的更选择,这是基于SRAM的FPGA通常无法达到要求的领域。

安森美同时也提供FPGA并行开发,一方面利用FPGA开发阶段固有的灵活性,同时也加快了ASIC低成本生产的速度。安森美提供具有竞争力的设计周期时间,能够实现快速投产。我们对制造工艺进行长期持续维护,以确保生产供应的不间断。

转换参考手册

FPGA设计流程

FPGA至ASIC转换

特性

为了与旧技术生产的ASIC具备同等的系统性能,FPGA采用最新的技术 。在FPGA中执行的设计,由于架构和材料,以及可编程逻辑和互连负荷,芯片尺寸较大。

这不仅增加了FPGA的总体功耗,而且对成本产生了直接影响。对于相同数量的门和RAM,ASIC的尺寸更小,金属层更少。这是由于ASIC中使用了更高效率的定制化布线。

ASIC的主要成本优势在于更小的晶片尺寸、更少的工艺步骤和更低的工艺升级需求。通过利用ASIC的密度优势,且可能实现将多个FPGA组合到单个芯片上,我们还能获得更多收益:空间占用更小,BOM成本更低,功耗性能更优,并最大限度地节约成本。

设计自动迁移至ASIC

低成本的直接替换

多个FGPA转换为一个ASIC

维持及提升原有的电路功能和性能

接受70余种FPGA和ASIC格式

优势

安森美直接拥有和运营制造工厂,并与行业标准的第三方代工厂保持合作。我们拥有超过25年的转换经验,将超过5000个设计转换成硅产品。

单芯片、非易失性解决方案

通电即行(LAPU),安全性能增强,不受单粒子效应(SEE)导致的配置逻辑错误影响

晶片尺寸减小,成本优化

与封装供应商合作提供全套解决方案

有竞争力的开发时间,强调产品上市时效

长制造工艺寿命

大部分工艺在境内(On-shore)生产完成

可选配加强性能,更具竞争力

功耗大幅度降低

定制化带来更优性能

伴随着器件速度的提升,FPGA比起ASIC的功耗显著增加。这在很大程度上是由于FPGA的布线中,芯片上的A点到B点不能直接相连,信号必须通过许多可编程布线开关和互连线段,每一个都会产生相当大的电容开销,这就导致了功耗的增加。

此外,时钟也是根据整个芯片上按照预定的时钟网络进行布线的,需要超大尺寸的驱动程序来处理所有可能的时序要求。这个庞大的时钟网络具有相当大的电容负载,在频率升高时会消耗大量的功率。

在ASIC中,时钟驱动器和网络是根据特定的时钟网络要求定制的,并在金属层中进行高效地布线。在ASIC的功耗中没有无用逻辑。高端FPGA能够做到比ASIC尺寸更小,但同时核心电压水平相同,这样的组合会导致更多漏电,进一步增加FPGA的功耗。 ASIC使用更简洁的封装来降低功耗,同时也有助于降低产品的整体成本,因为封装成本可能占到器件总成本的三分之一甚至更多。